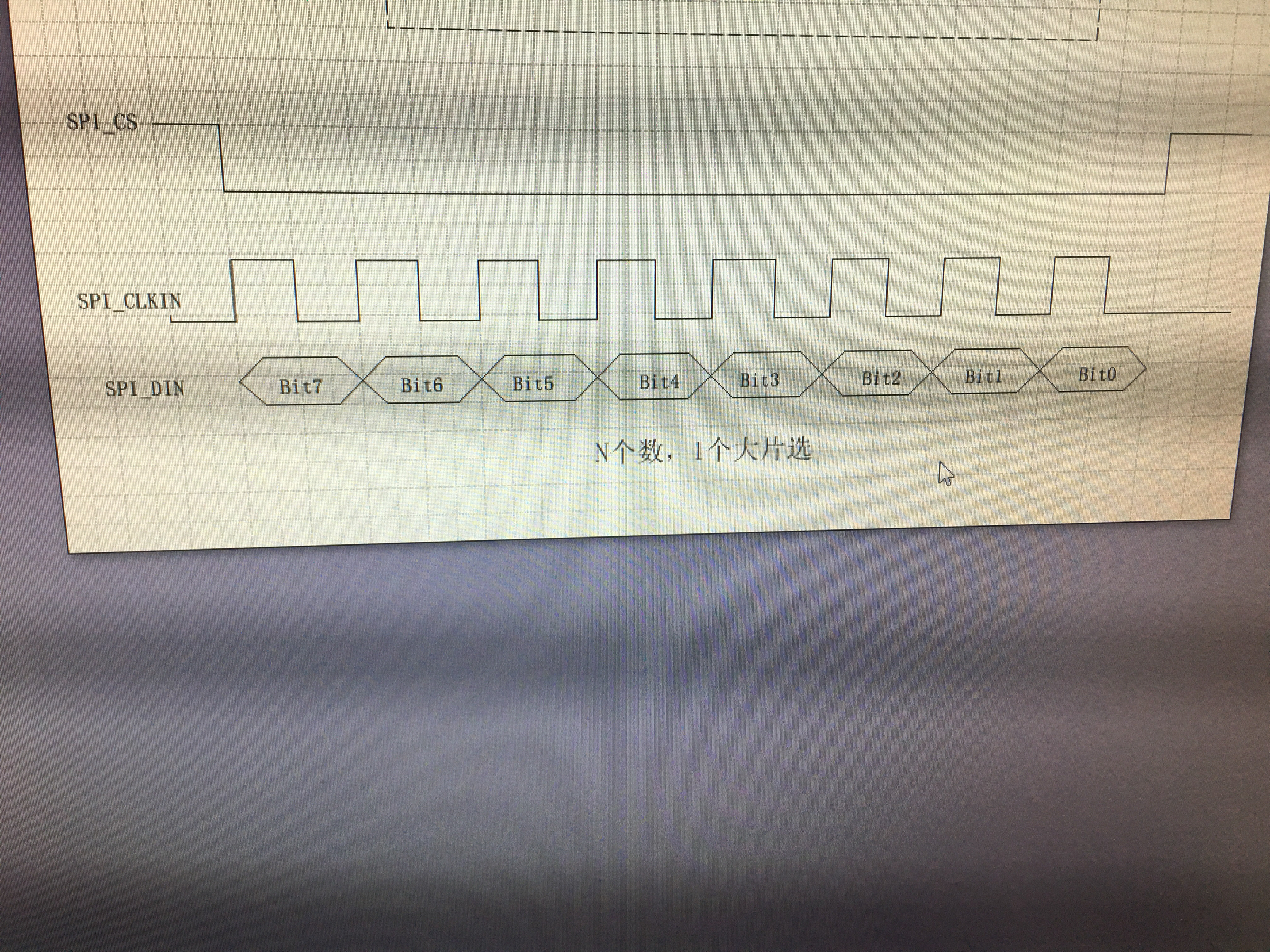

名称:基于FPGA的SPI时序图设计VHDL代码VIVADO仿真(文末获取)

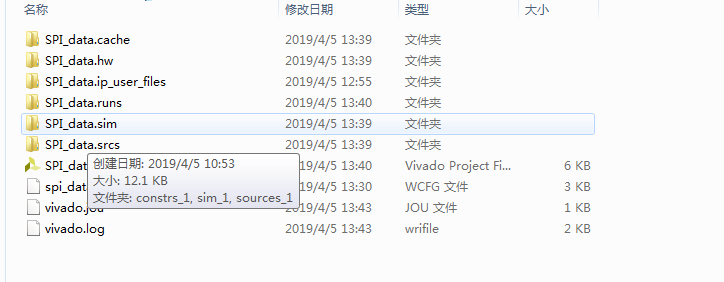

软件:VIVADO

语言:VHDL

代码功能:

1.工程文件

2.程序文件

3.管脚约束文件

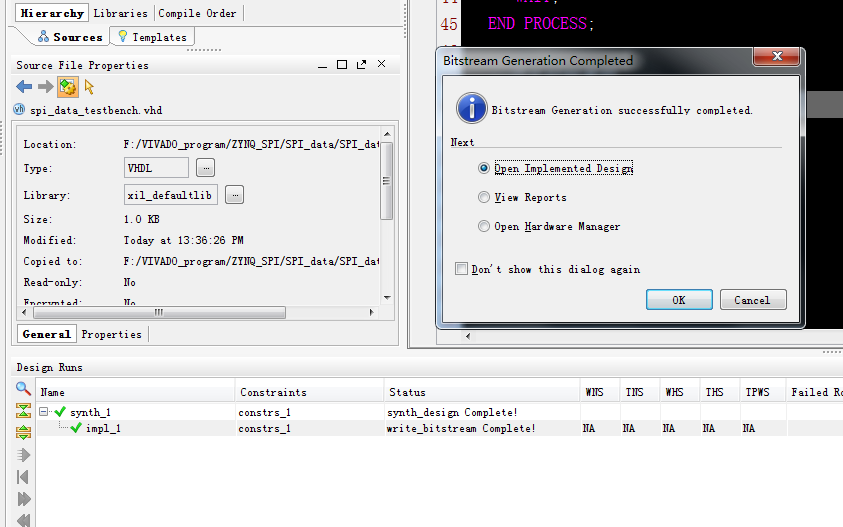

4.程序编译综合

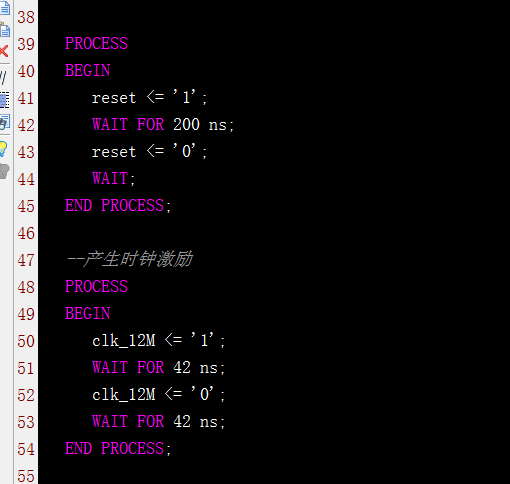

5.Testbench

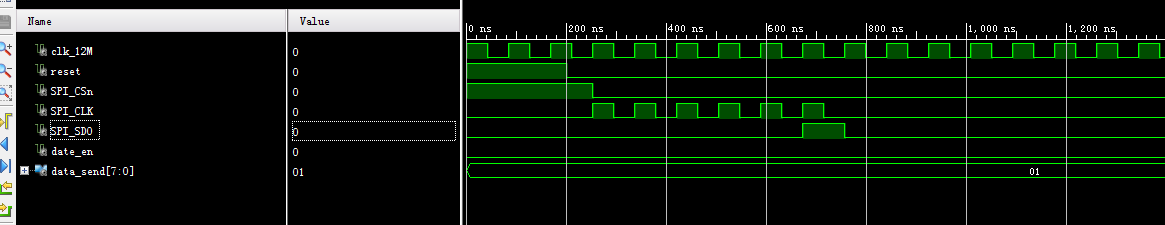

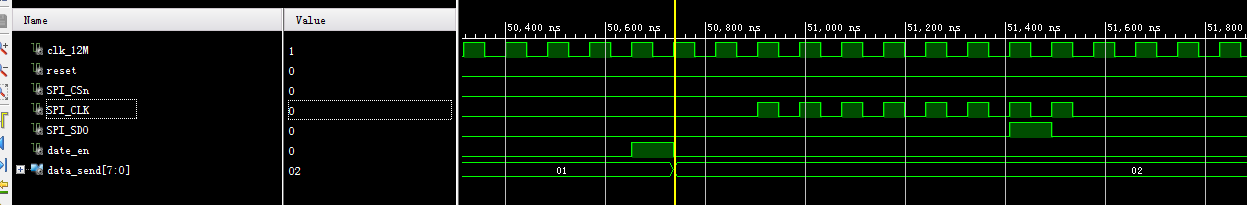

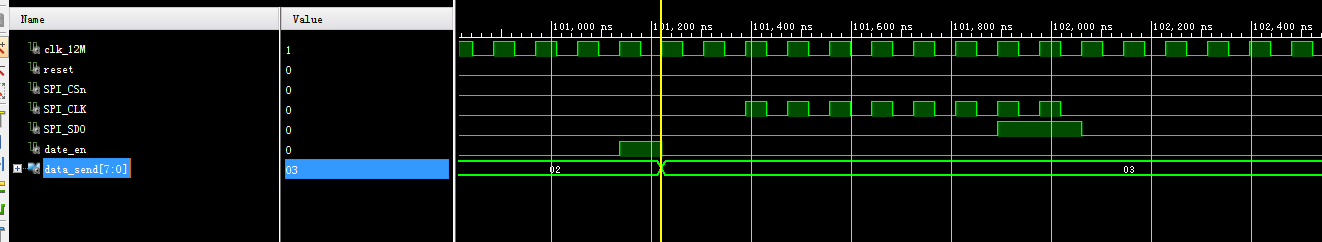

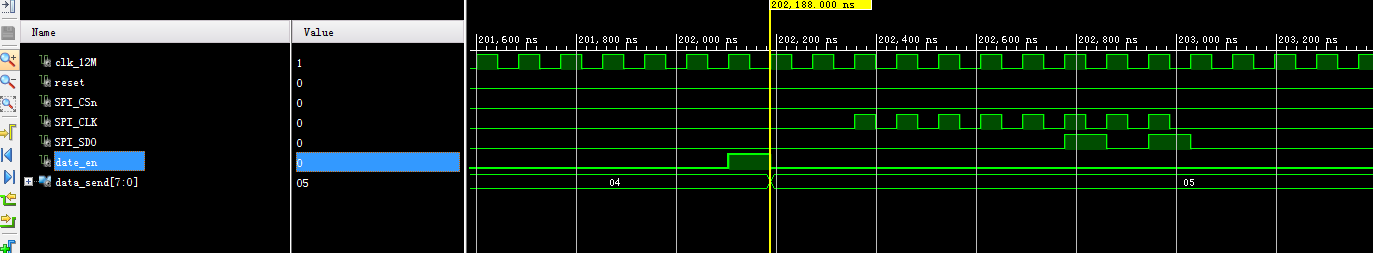

6.仿真图

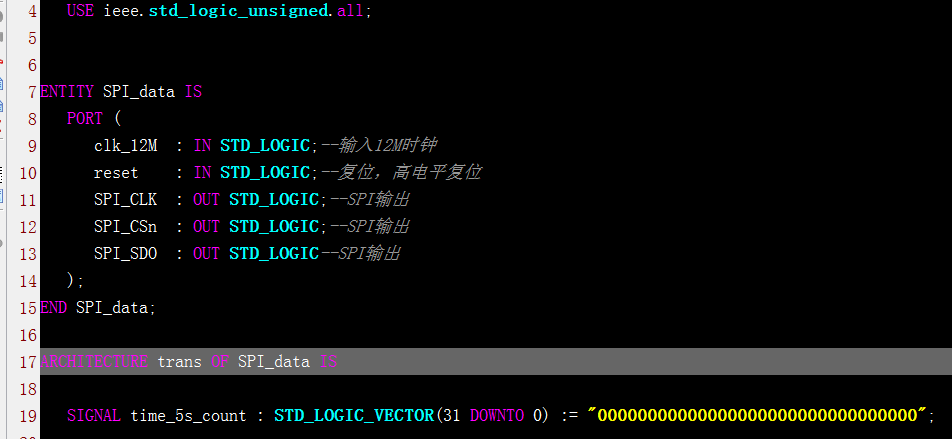

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY spi_data_testbench IS END spi_data_testbench; ARCHITECTURE trans OF spi_data_testbench IS COMPONENT SPI_data IS PORT ( clk_12M : IN STD_LOGIC; reset : IN STD_LOGIC; SPI_CLK : OUT STD_LOGIC; SPI_CSn : OUT STD_LOGIC; SPI_SDO : OUT STD_LOGIC ); END COMPONENT; SIGNAL clk_12M : STD_LOGIC; SIGNAL reset : STD_LOGIC; SIGNAL SPI_CLK : STD_LOGIC; SIGNAL SPI_CSn : STD_LOGIC; SIGNAL SPI_SDO : STD_LOGIC; BEGIN i_SPI_data : SPI_data PORT MAP ( clk_12m => clk_12M, reset => reset, spi_clk => SPI_CLK, spi_csn => SPI_CSn, spi_sdo => SPI_SDO );

源代码

扫描文章末尾的公众号二维码

655

655

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?