名称:智能洗衣机控制系统设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

其中EDA技术所用到的最D的一种语是Verilog, Verilog HDL是一种硬件描述语言(以文本形式来描述数字系统硬件的结构和行为的语言),用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。因此我们在设计智能洗衣机控制系统中就采用了这种语言

基于 Verilog HDL语言的智能洗衣机控制系统的基本功能设计如下:

1可以设计为4种洗衣模式

(1)强力洗衣模式:工作程序为,注水>洗衣>排水>用干

注水>漂洗>排水>甩干

注水>漂洗>排水>甩干。(其中洗衣时间设置为10分钟

(2)普通洗衣模式:工作程序为,注水>洗衣>排水>用干

注水>漂洗>排水>甩干

注水>漂洗>排水>用干。(其中洗衣时间设置为5分钟)

(3)漂洗模式:工作程序为,注水>漂洗>排水>甩千

注水>漂洗>排水>甩干。

(4)甩干模式:工作程序,甩干

在以上四种洗衣模式中,注水时间为1-3分钟,漂洗为5分钟,排水为2分钟,甩干为3分钟

2显示洗衣完成所需时间。

3用不同的LED灯显示洗衣机当前的工作状态(注水、洗衣、排水、甩干)

4洗衣完成后锋鸣3次提示

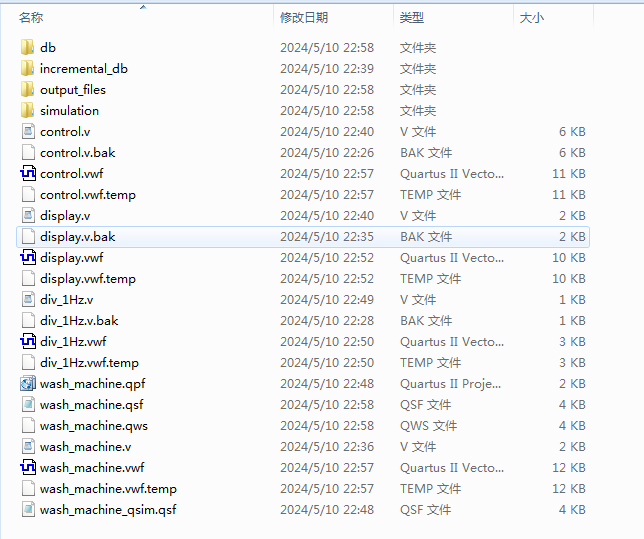

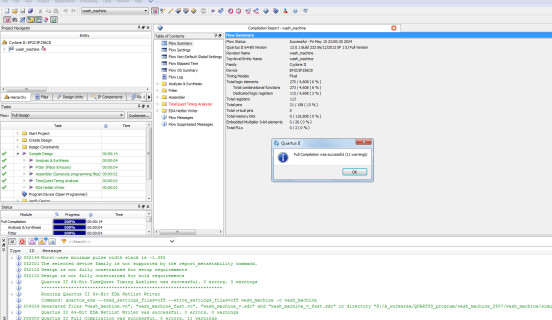

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

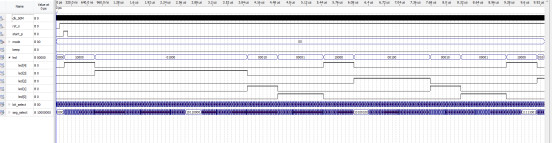

5. 仿真图(仿真图上左侧为信号名,信号名的具体含义见代码端口注释)

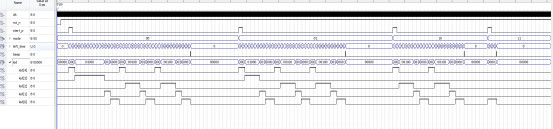

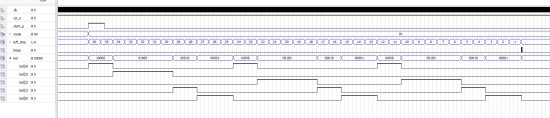

整体仿真图

上图为整体仿真图,图中start_p为开始按键,高电平表示按下按键,开始洗衣。Mode表示洗衣模式,mode=2’b00表示属于强力洗衣模式,此时通过led信号可以观察到洗衣机的工作状态。其中led[4]表示注水,led[3]表示洗衣,led[2]表示漂洗,led[1]表示排水,led[0]表示甩干。上图中,在强力洗衣模式下,依次进行了注水,洗衣,排水,甩干,再注水,漂洗,排水,甩干,注水,漂洗...等步骤。

图中bit_select表示数码管的位选信号,bit_select表示数码管段选信号,数码管显示洗衣时间。具体的显示内容分析在后文显示模块进行分析。

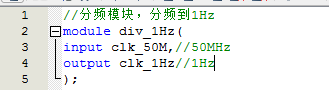

分频模块

分频模块原理为使用计数器进行计数,要将50MHz分频到1Hz,需要从0计数到24999999得到1Hz的半个周期,然后控制1Hz信号翻转,同时计数器清零并且重新开始计数。如此循环就能得到1Hz的信号。在进行仿真时,为便于仿真,将24999999的计数值减小为25。实际应该是24999999。

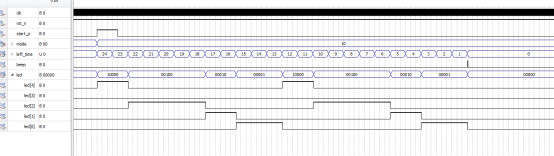

上图为分频模块仿真图,分频模块用于将50MHz的时钟分频为1Hz的时钟,1Hz对应1秒钟,使用1Hz信号就能得到分钟信号,从而控制洗衣机的运行时间。

图中clk_50M表示输入的50MHz时钟,clk_1Hz表示分频输出的1Hz时钟,可以看到1Hz时钟的周期明显大于50MHz。

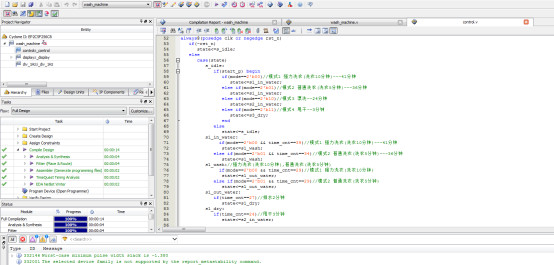

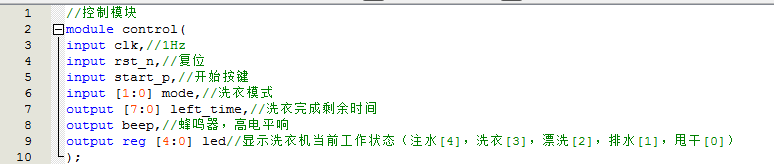

控制模块

控制模块为核心处理模块,图中start_p为开始按键,mode为洗衣模式设置信号,left_time为洗衣完成剩余时间,beep表示蜂鸣器,led表示洗衣机当前个状态,led[4]表示注水,led[3]表示洗衣,led[2]表示漂洗,led[1]表示排水,led[0]表示甩干。

上图为4个模式的洗衣仿真图,mode信号分别为00,01,10,11,代表4种模式,图中可以看到,当start_p按下后,洗衣机开始工作,分别按强力洗衣、正常洗衣、漂洗、甩干等模式洗衣,且洗衣结束后蜂鸣器信号变为高电平提示洗衣结束。下面依次详细分析强力洗衣、正常洗衣、漂洗、甩干等模式。

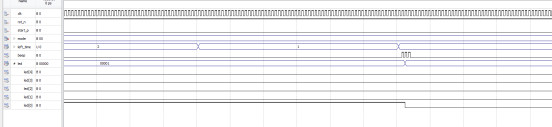

上图为强力洗衣模式,图中mode信号为00,表示强力洗衣模式。Start_p信号开始后,left_time显示41分钟,从41开始倒计时,按注水->洗衣->排水->甩干->注水->漂洗->排水->甩干->注水->漂洗->排水->甩干的步骤进行,其中洗衣时间10分钟,注水时间2分钟,漂洗5分钟,排水2分钟,甩干3分钟。

上图为强力洗衣模式,洗衣结束时,beep蜂鸣器响3次

上图为正常洗衣模式,图中mode信号为01,表示正常洗衣模式。Start_p信号开始后,left_time显示36分钟,从36开始倒计时,按注水->洗衣->排水->甩干->注水->漂洗->排水->甩干->注水->漂洗->排水->甩干的步骤进行,其中洗衣时间5分钟,注水时间2分钟,漂洗5分钟,排水2分钟,甩干3分钟,结束后蜂鸣器响3声。

上图为漂洗模式,图中mode信号为10,表示漂洗模式。Start_p信号开始后,left_time显示24分钟,从24开始倒计时,按注水->漂洗->排水->甩干->注水->漂洗->排水->甩干的步骤进行,其中注水时间2分钟,漂洗5分钟,排水2分钟,甩干3分钟,结束后蜂鸣器响3声。

上图为甩干模式,图中mode信号为11,表示甩干模式。Start_p信号开始后,left_time显示3分钟,从3开始倒计时,直接进入甩干的步骤,甩干3分钟,结束后蜂鸣器响3声。

显示模块

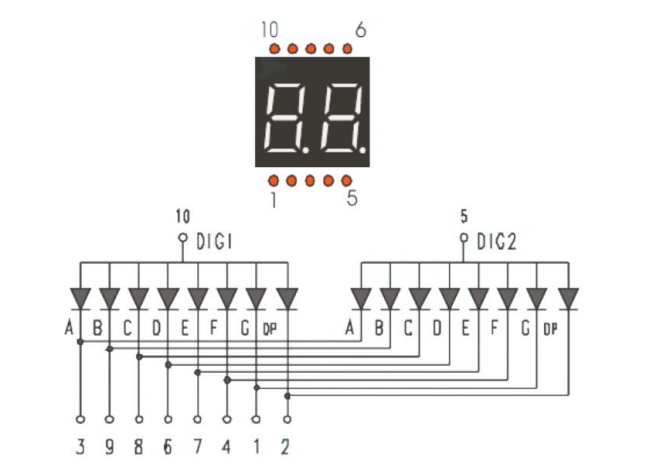

显示模块显示剩余时间,使用2位数码管显示,数码管为共阳极数码管,当数码管的段选信号为低电平时,对应的段亮。两位数码管,其内部连接如下图。

由此图可知,两位 8 段数码管共 10 个引脚,每位数码管的阳极连接在一起, 为共阳极数码管,每位数码管相同段的 led 的阴极连接在一起,这样当给第 10 和第 5 脚高电平,给第 3 脚 低电平时,两个数码管的发光二极管 A 都点亮。以显示数字“18”为例,

既然同时给第 10 和第 5 脚高电平不可行,那么是不是可以先给第 5 脚高电平,第 10 脚低电平,此时, 让其显示数字“8”时,左边的数码管不显示,右边的数码管显示数字“8”;然后给第 10 脚高电平,第 5 脚低电平,此时,让其显示数字“1”时,左边的数码管显示数字“1”,右边的数码管不显示,这样就可 以显示数字“18”了。但有一个问题,多长时间切换显示的数码管呢,时间如果太长就只能看到数字―8” 或数字“1”了,时间太短呢,结果是显示不清晰而且显示亮度不够。由于人眼的视觉暂留(人眼在观察景 物时,光信号传人大脑神经,需经过一段短暂的时间,光的作用结束后,视觉形象并不立即消失,这种残

留的视觉称“后像”,视觉的这一现象则被称为“视觉暂留”)及发光二极管的余辉效应(当停止向发光二极管供电时,发光二极管亮度仍能维持一段时间),每位数码管的点亮时间为 1~2ms 时,显示效果能满足使用需要。数码管的这种驱动方式称为数码管的动态驱动,实际上就是分时轮流控制不同数码管的显示。

以上就是数码管显示的原理,根据该原理,只需要按顺序依次显示剩余时间的十位和个位即可。

显示模块用于显示洗衣倒计时,图中left_time为洗衣剩余时间,图中可以看到时间从19开始,依次倒计时到17。Seg_select为数码管段选,bit_select为数码管位选。位选控制的是哪个数码管点亮,seg_select控制当前数码管显示什么内容,比如图中10010000表示9,11111001表示1,组合起来就是19,18,17也是同理。

不足之处:

本代码根据要求进行了仿真,并且仿真了代码功能,但是由于没有实际的硬件,并未进行硬件测试,后期有条件可以进行硬件测试,进一步验证代码功能。

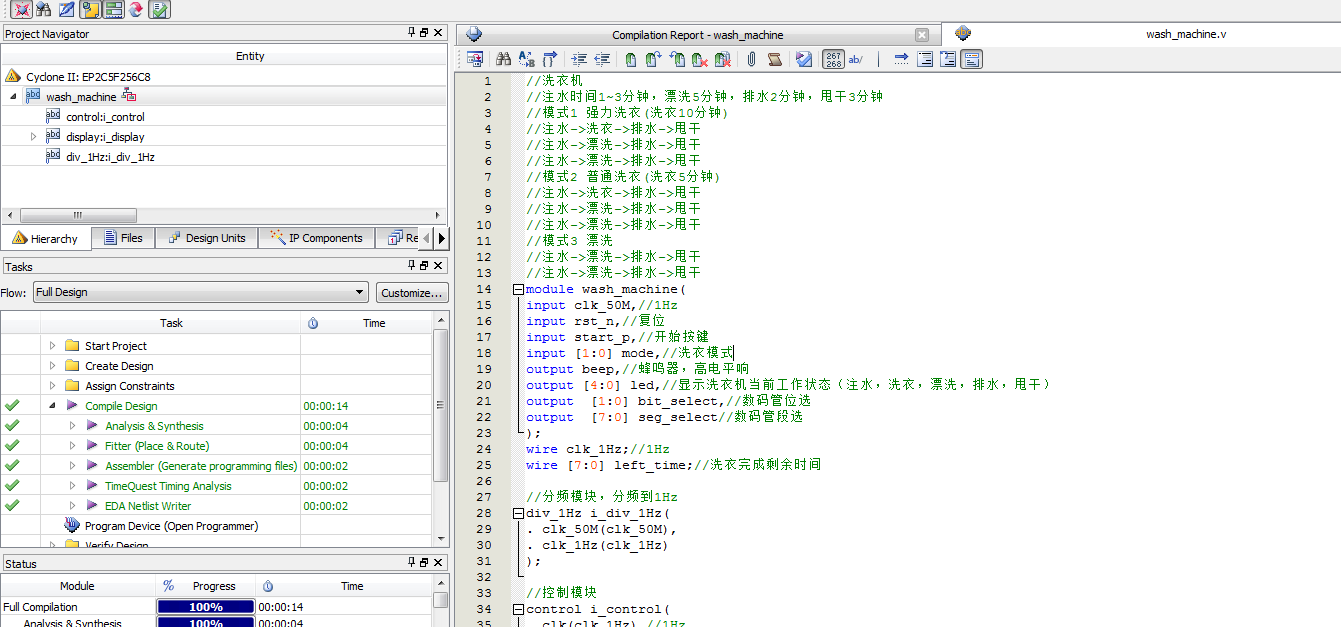

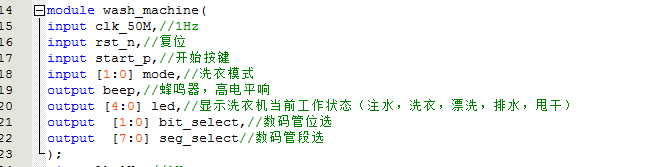

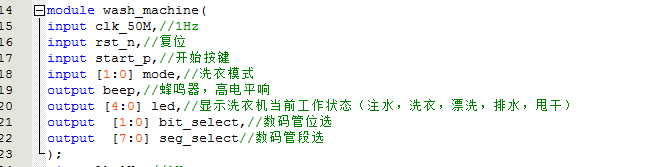

部分代码展示:

//洗衣机 //注水时间1~3分钟,漂洗5分钟,排水2分钟,甩干3分钟 //模式1 强力洗衣(洗衣10分钟) //注水->洗衣->排水->甩干 //注水->漂洗->排水->甩干 //注水->漂洗->排水->甩干 //模式2 普通洗衣(洗衣5分钟) //注水->洗衣->排水->甩干 //注水->漂洗->排水->甩干 //注水->漂洗->排水->甩干 //模式3 漂洗 //注水->漂洗->排水->甩干 //注水->漂洗->排水->甩干 module wash_machine( input clk_50M,//1Hz input rst_n,//复位 input start_p,//开始按键 input [1:0] mode,//洗衣模式 output beep,//蜂鸣器,高电平响 output [4:0] led,//显示洗衣机当前工作状态(注水,洗衣,漂洗,排水,甩干) output [1:0] bit_select,//数码管位选 output [7:0] seg_select//数码管段选 ); wire clk_1Hz;//1Hz wire [7:0] left_time;//洗衣完成剩余时间

源代码

点击下方的公众号卡片获取

435

435

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?