名称:汉字点阵显示系统的设计与实现VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

汉字点阵显示系统的设计与实现

属性:综合性

实验目的:设计并制作一个LED汉字点阵显示系统

实验内容:实现16×16点阵的任意汉字的左右及上下滚屏显示,并制作本校学生会工作的广告、通知标语

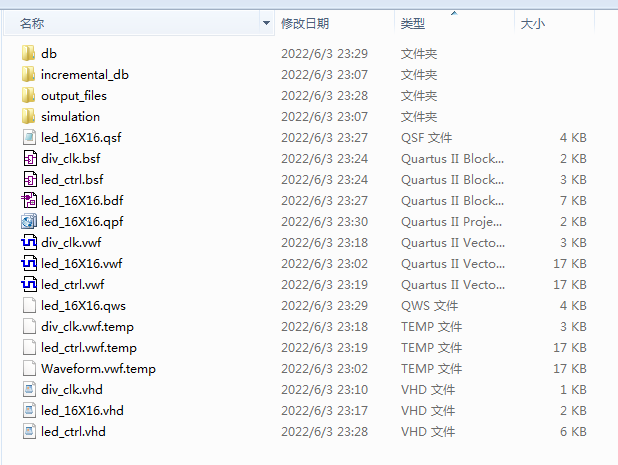

1. 工程文件

2. 程序文件

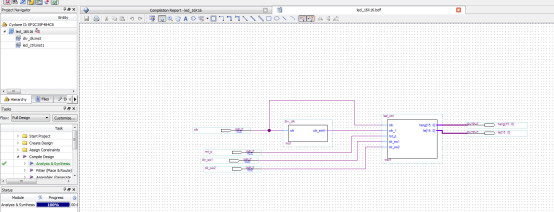

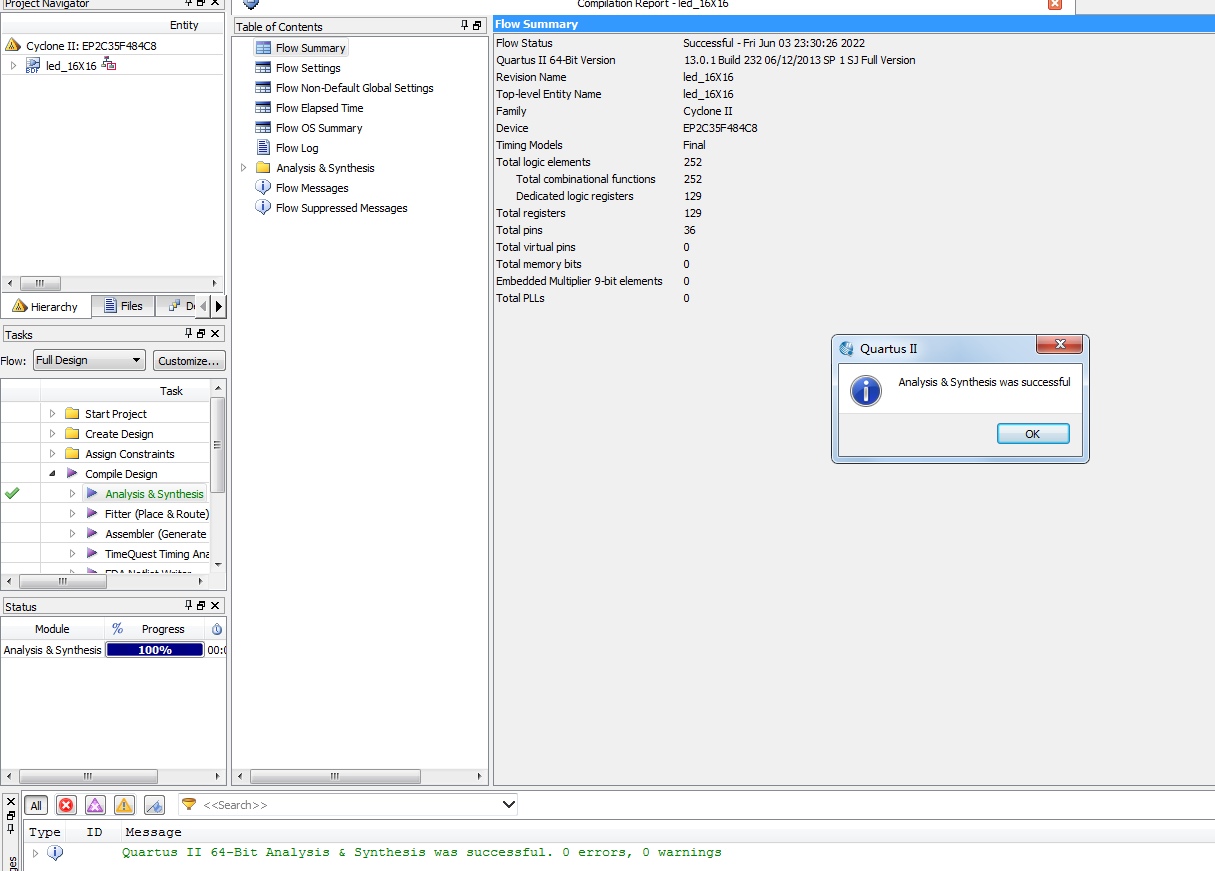

3. 程序编译

4. 仿真图

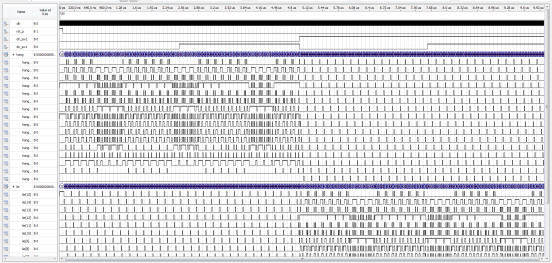

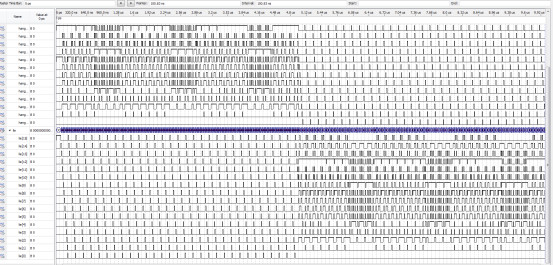

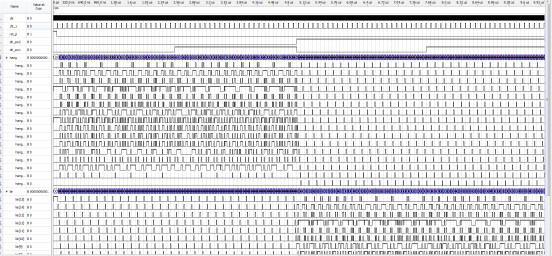

整体仿真图

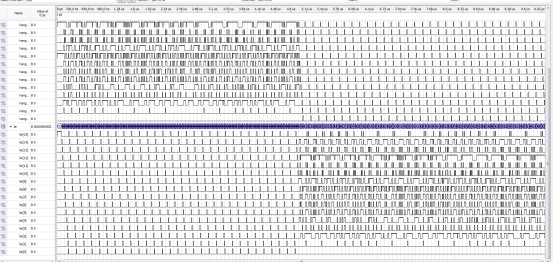

局部放大

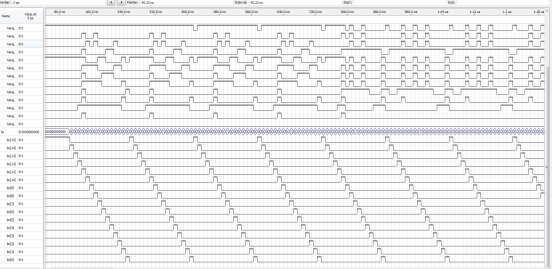

局部放大

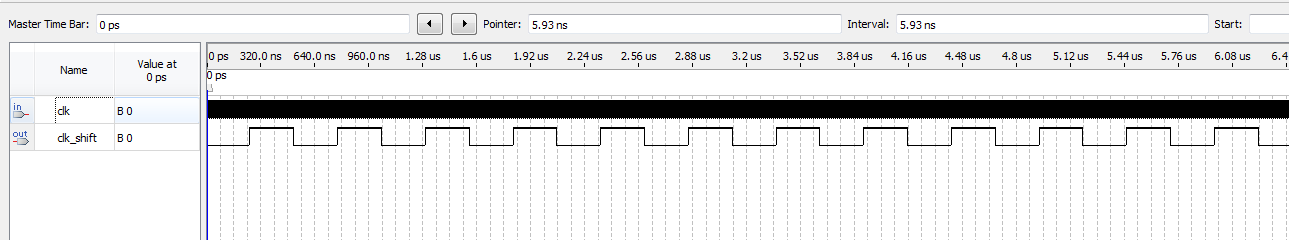

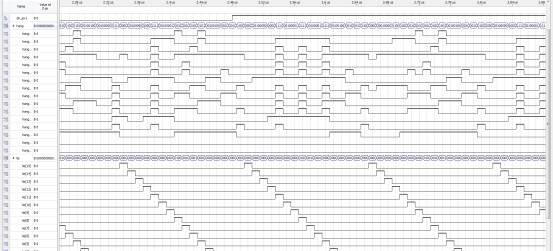

分频模块仿真图

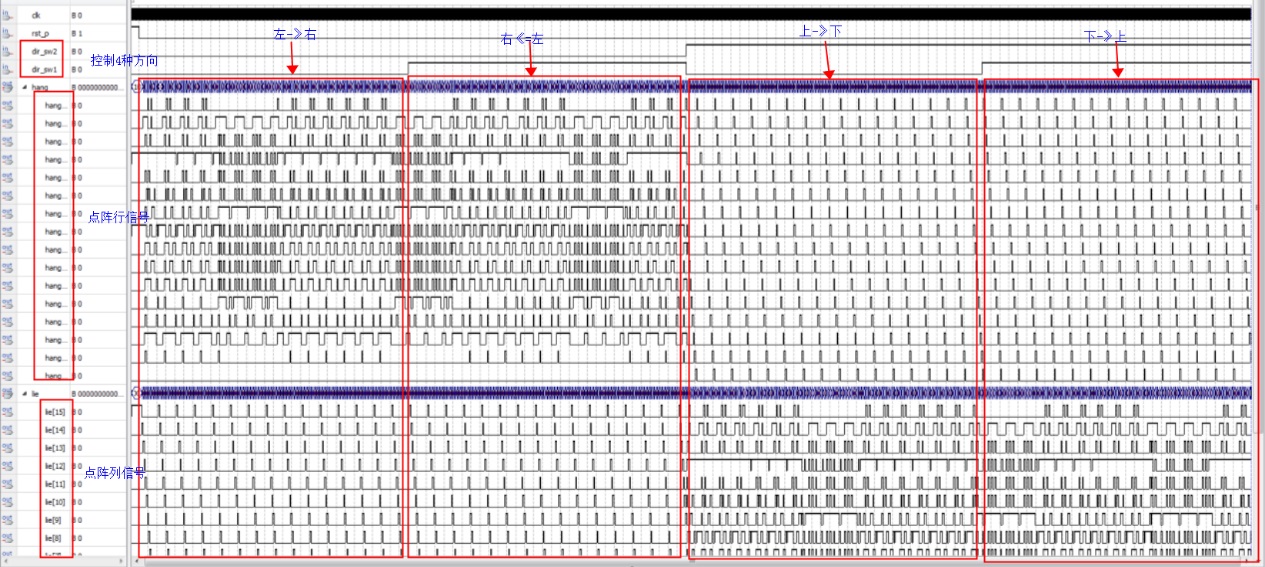

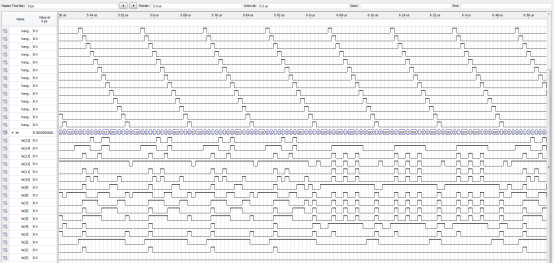

控制模块仿真图

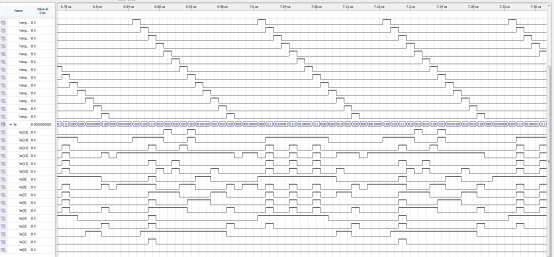

局部放大

局部放大

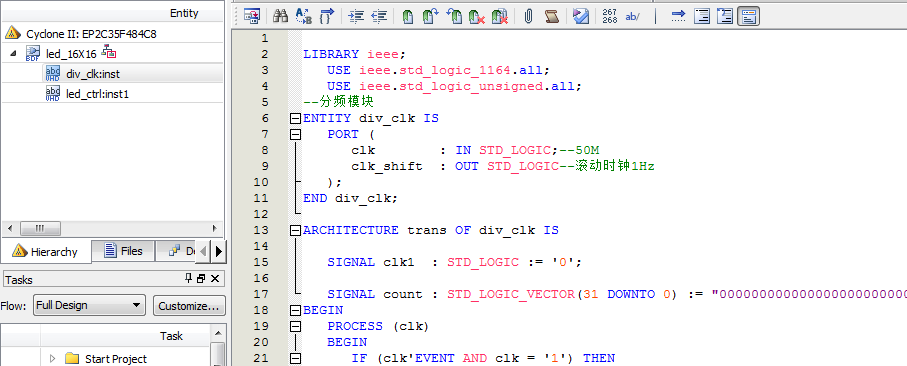

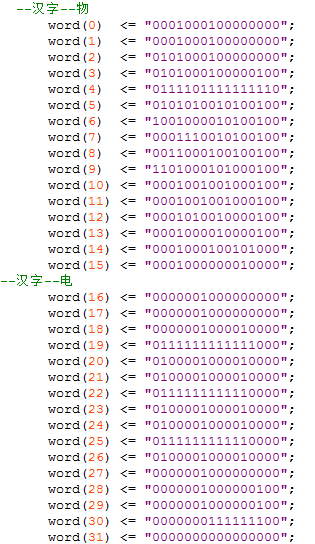

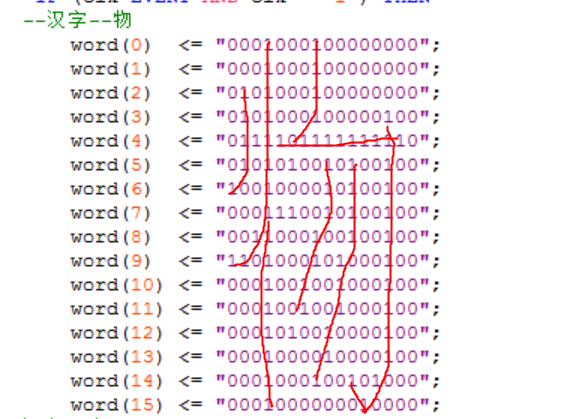

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --16*16点阵 ENTITY led_16X16 IS PORT ( clk : IN STD_LOGIC;--时钟 rst_p : IN STD_LOGIC;--复位 dir_sw1 : IN STD_LOGIC;--方向(同方向的正反切换) dir_sw2 : IN STD_LOGIC;--方向(左右和上下切换) hang : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--行 lie : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)--列 ); END led_16X16; ARCHITECTURE trans OF led_16X16 IS COMPONENT led_ctrl IS PORT ( clk : IN STD_LOGIC; clk_1 : IN STD_LOGIC; rst_p : IN STD_LOGIC; dir_sw1 : IN STD_LOGIC; dir_sw2 : IN STD_LOGIC; hang : OUT STD_LOGIC_VECTOR(15 DOWNTO 0); lie : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) ); END COMPONENT; COMPONENT div_clk IS PORT ( clk : IN STD_LOGIC; clk_shift : OUT STD_LOGIC ); END COMPONENT; SIGNAL clk_shift : STD_LOGIC;--滚动时钟1Hz BEGIN --分频模块 i_div_clk : div_clk PORT MAP ( clk => clk,--50M clk_shift => clk_shift--1Hz ); --控制模块 i_led_ctrl : led_ctrl PORT MAP ( clk => clk,--50M clk_1 => clk_shift, rst_p => rst_p, dir_sw1 => dir_sw1,--方向(同方向的正反切换) dir_sw2 => dir_sw2,--方向(左右和上下切换) hang => hang,--行 lie => lie--列 ); END trans;

源代码

扫描文章末尾的公众号二维码

327

327

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?