名称:正数倒数计时器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

从5开始,拨动开关1,开始倒计时543210—秒一变拔动开关2,开始正向增加5.6.7.8.9.10—秒一变

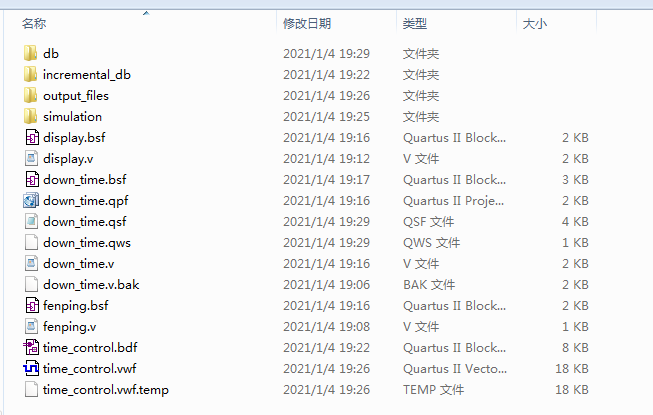

1. 工程文件

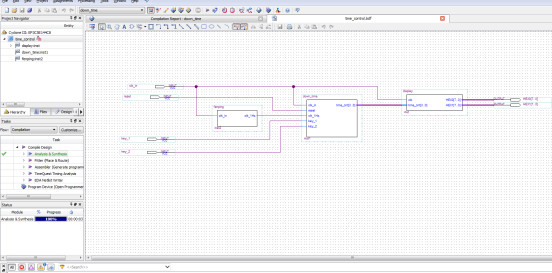

2. 顶层block图

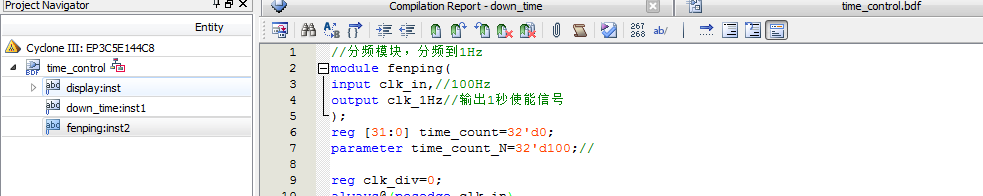

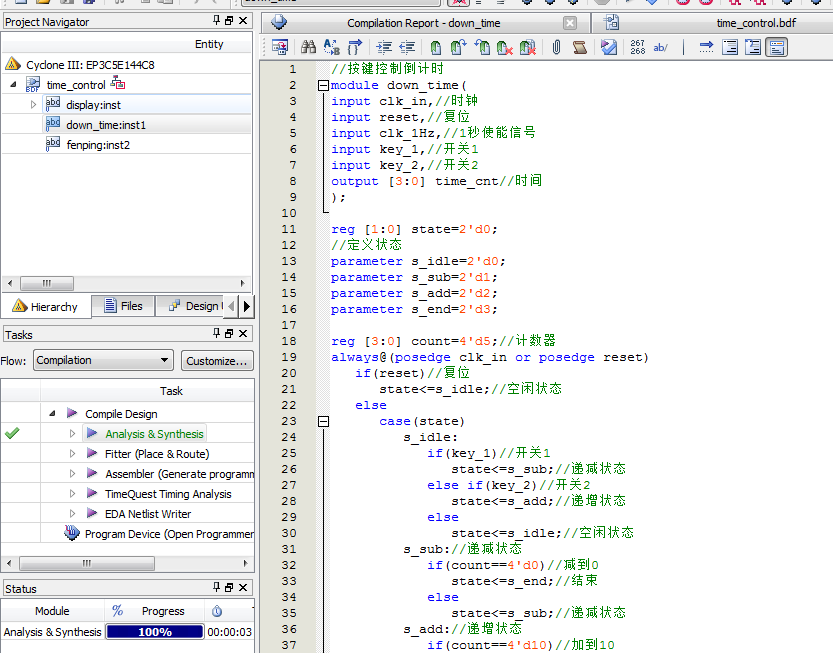

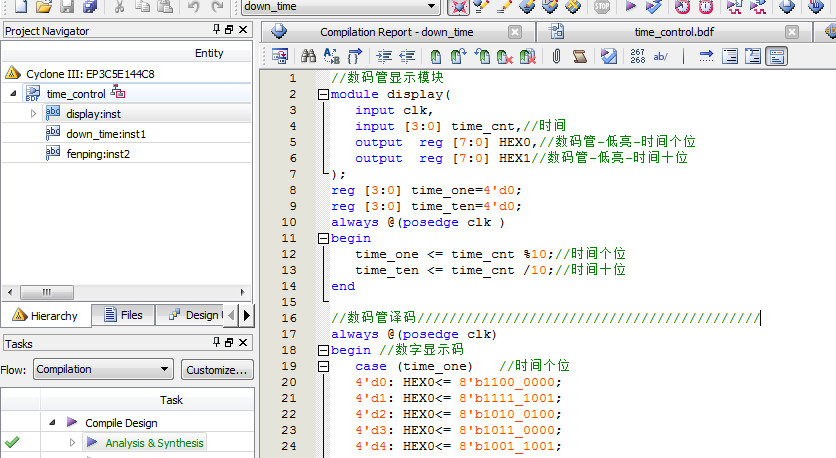

3. 模块代码

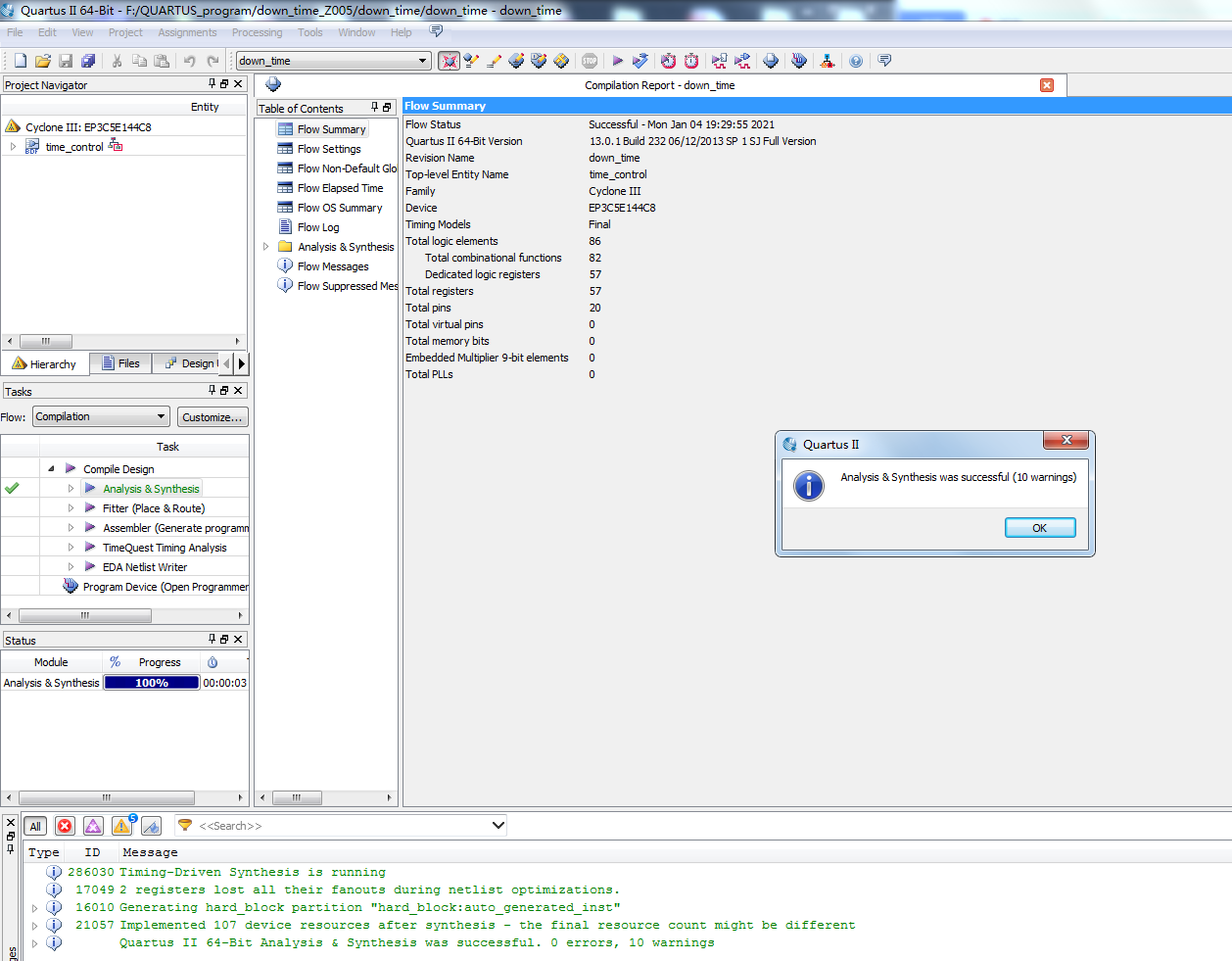

4. 程序编译

5. 仿真图

部分代码展示:

//按键控制倒计时 module down_time( input clk_in,//时钟 input reset,//复位 input clk_1Hz,//1秒使能信号 input key_1,//开关1 input key_2,//开关2 output [3:0] time_cnt//时间 ); reg [1:0] state=2'd0; //定义状态 parameter s_idle=2'd0; parameter s_sub=2'd1; parameter s_add=2'd2; parameter s_end=2'd3; reg [3:0] count=4'd5;//计数器 always@(posedge clk_in or posedge reset) if(reset)//复位 state<=s_idle;//空闲状态 else case(state) s_idle: if(key_1)//开关1 state<=s_sub;//递减状态 else if(key_2)//开关2 state<=s_add;//递增状态 else state<=s_idle;//空闲状态 s_sub://递减状态 if(count==4'd0)//减到0 state<=s_end;//结束 else state<=s_sub;//递减状态 s_add://递增状态 if(count==4'd10)//加到10 state<=s_end;//结束 else state<=s_add;//递增状态 s_end://结束 state<=s_idle;//空闲状态 default:; endcase always@(posedge clk_in or posedge reset) if(reset)//复位 count<=4'd5;//起始值为5 else if(state==s_sub && clk_1Hz)//递减状态/1秒使能信号 count<=count-1;//递减 else if(state==s_add && clk_1Hz)//递增状态/1秒使能信号 count<=count+1;//递增 else ; assign time_cnt=count;//时间 endmodule

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?