名称:DPSK调制解调器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

DPSK调制解调器

1、输入调制信号,进行差分编码

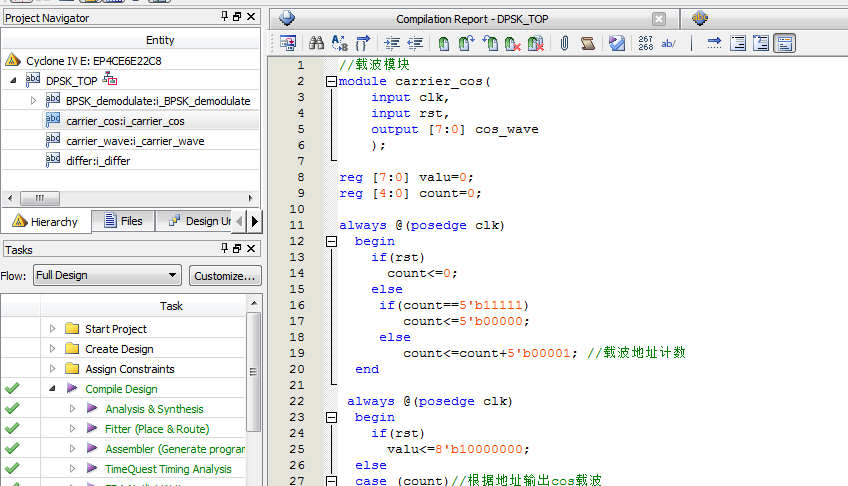

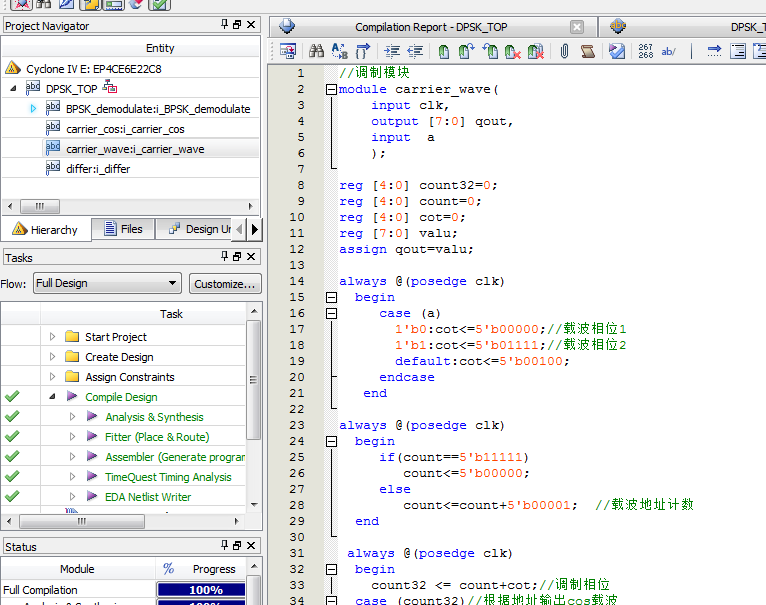

2、产生本地载波,进行DPSK调制

3、对DPSK调制信号进行解调,输出调制后信号

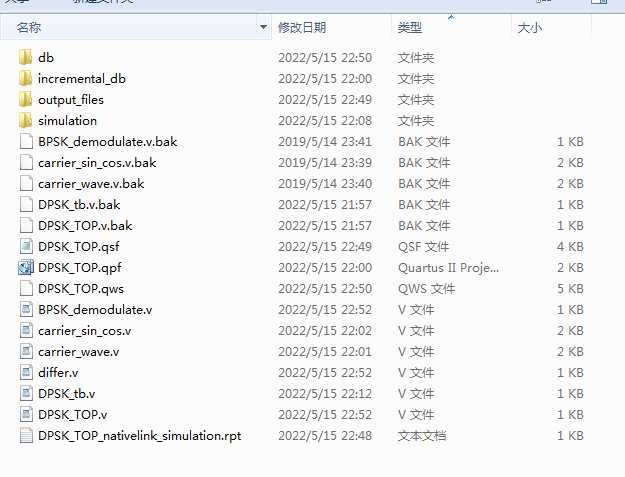

1. 工程文件

2. 程序文件

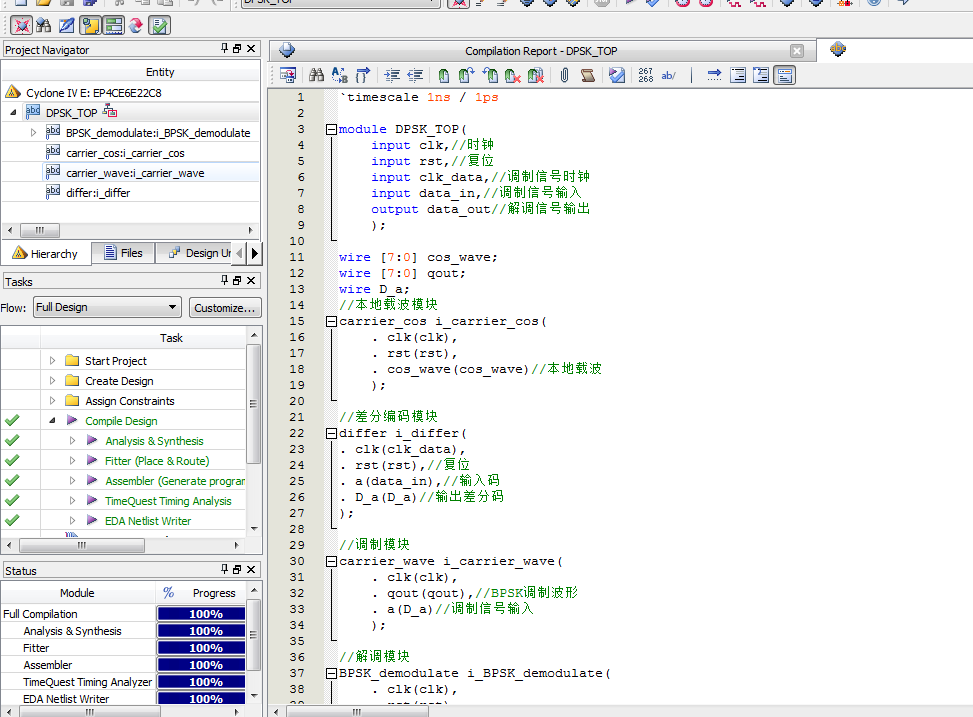

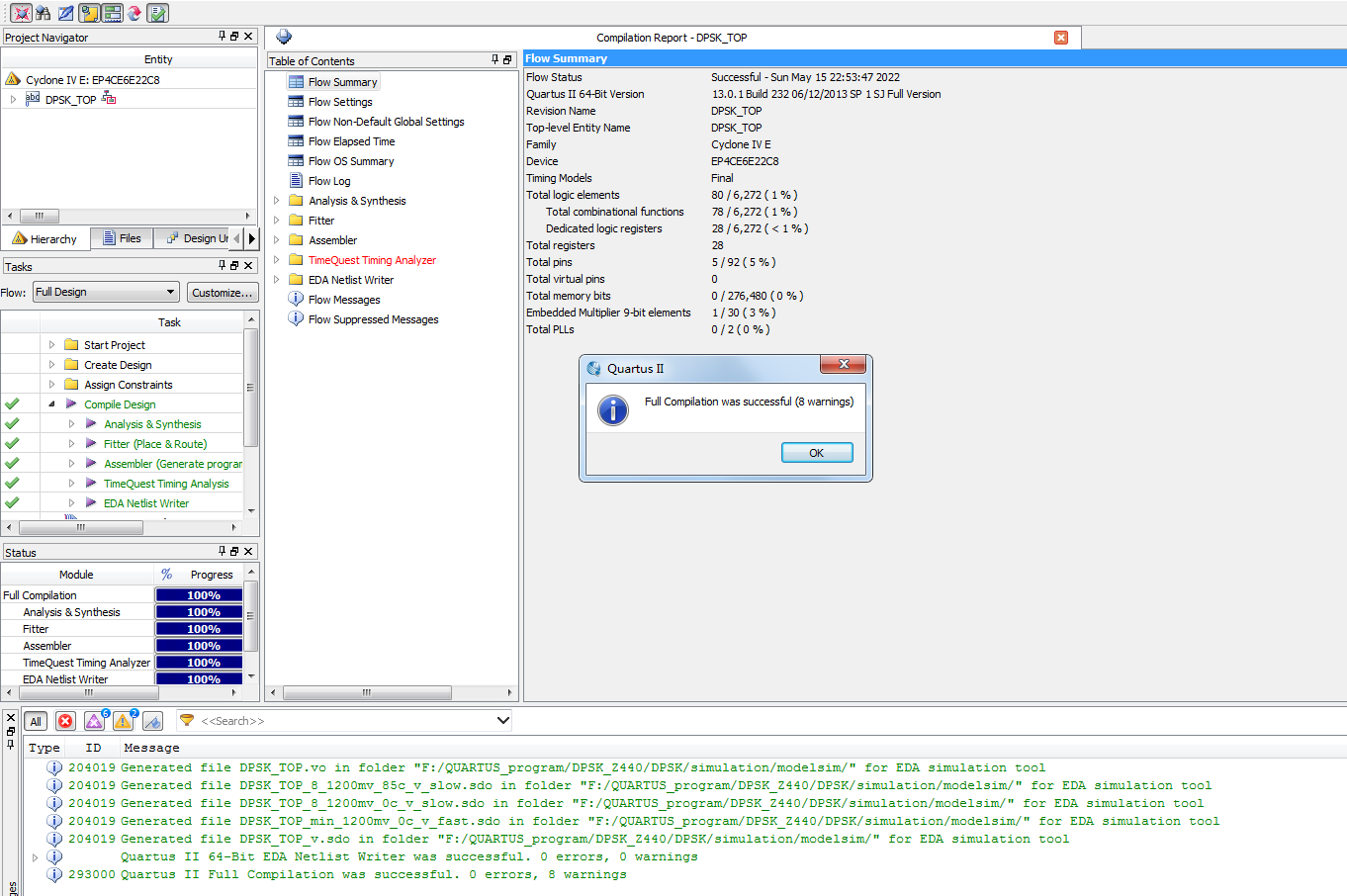

3. 程序编译

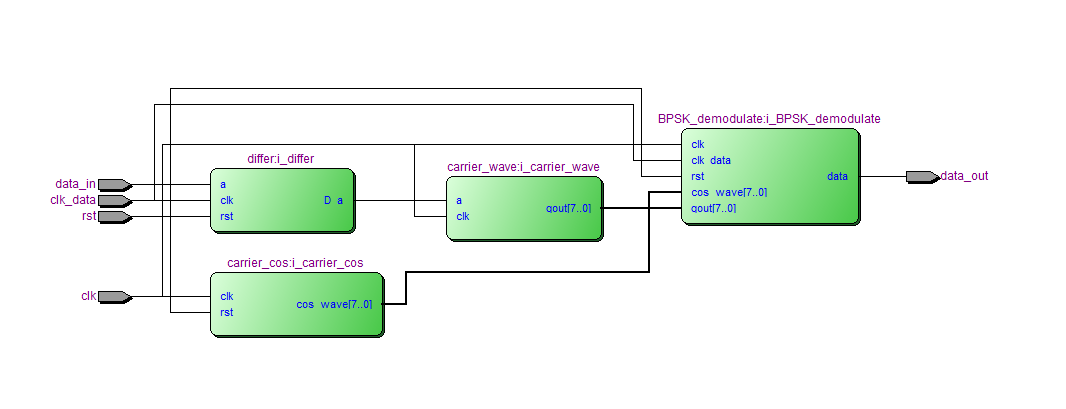

4. RTL图

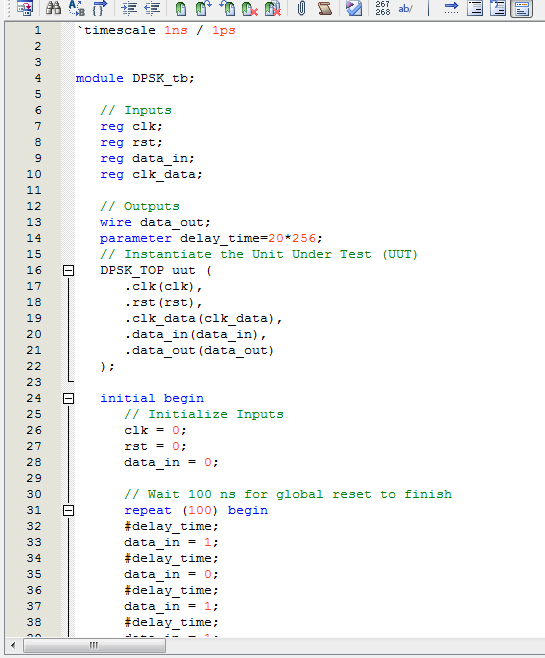

5. Testbench

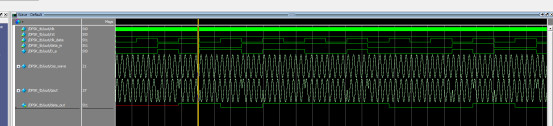

6. 仿真图

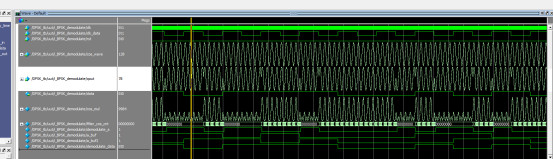

6.1 顶层模块仿真

最终解调输出波形与调制输入有一点延迟,但是波形一致,解调正确。

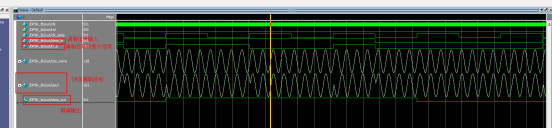

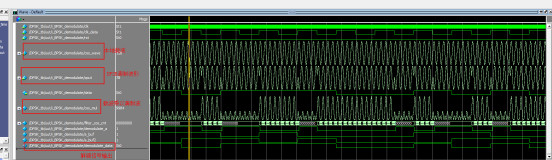

6.2 本地载波模块

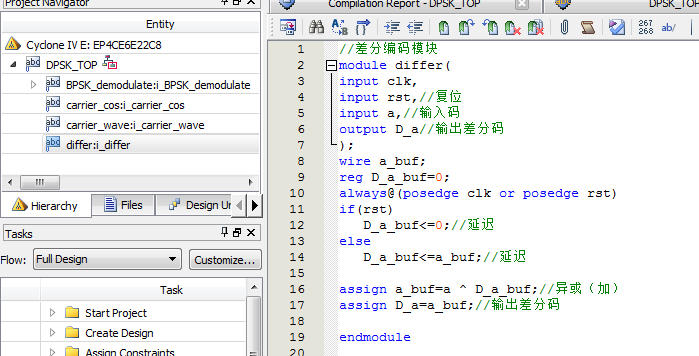

6.3 差分编码模块

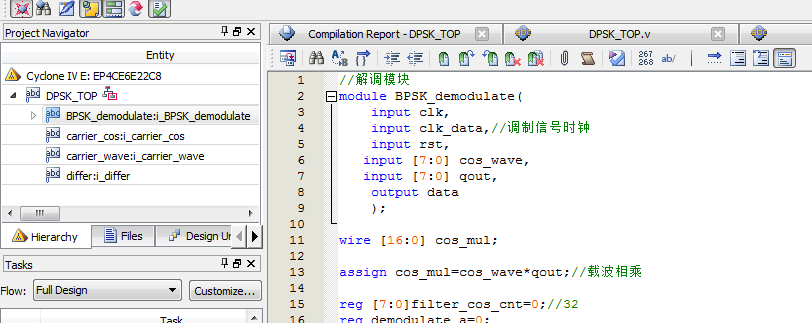

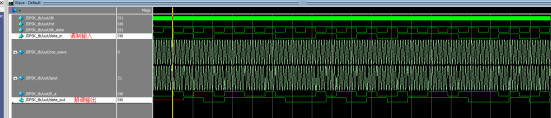

6.4 调制模块

6.5 解调模块

部分代码展示:

`timescale 1ns / 1ps module DPSK_tb; // Inputs reg clk; reg rst; reg data_in; reg clk_data; // Outputs wire data_out; parameter delay_time=20*256; // Instantiate the Unit Under Test (UUT) DPSK_TOP uut ( .clk(clk), .rst(rst), .clk_data(clk_data), .data_in(data_in), .data_out(data_out) ); initial begin // Initialize Inputs clk = 0; rst = 0; data_in = 0; // Wait 100 ns for global reset to finish repeat (100) begin #delay_time; data_in = 1; #delay_time; data_in = 0; #delay_time; data_in = 1; #delay_time; data_in = 1; #delay_time; data_in = 1; #delay_time; data_in = 0; #delay_time; data_in = 0; #delay_time; data_in = 1; #delay_time; data_in = 0; // Add stimulus here end end always begin clk_data = 0; #2560; clk_data = 1; #2560; end always begin clk = 0; #10; clk = 1; #10; end endmodule

源代码

点击下方的公众号卡片获取

111

111

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?