名称:按键和数码管测试设计Verilog代码VIVADO ARTIX-7开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

按键和数码管测试

按下按键,则8位数码管显示对应的按键值,本试验用来验证8位数码管和5个按键,按下按键,则8位数码管显示对应的按键值。

本代码已在ARTIX-7开发板验证,ARTIX-7开发板如下,其他开发板可以修改管脚适配:

1实验简介

本试验用来验证8位数码管和5个按键,按下按键,则8位数码管显示对应的按键值。

2实验原理

先来了解一下数码管的工作原理,7段数码管(即便有小数点,我们也习惯的称呼为7段数码管)是指着 7个发光二极管而言的。任意一个 0-9 的阿拉伯数字的显示,只要通过这 7个发光二极管进行亮或灭的组合都可以实现。例如,我们要显示数字 0, 那么只要让发光二极管 a、b、c、d、e、f 点亮(g 和 dot 熄灭)就可以了。

我们开发板上采用了8位7段数码管,即可以通过FPGA控制输出8个7段数码管。我们通过按键来控制数码管的显示,即8位数码管显示对应的按键值。

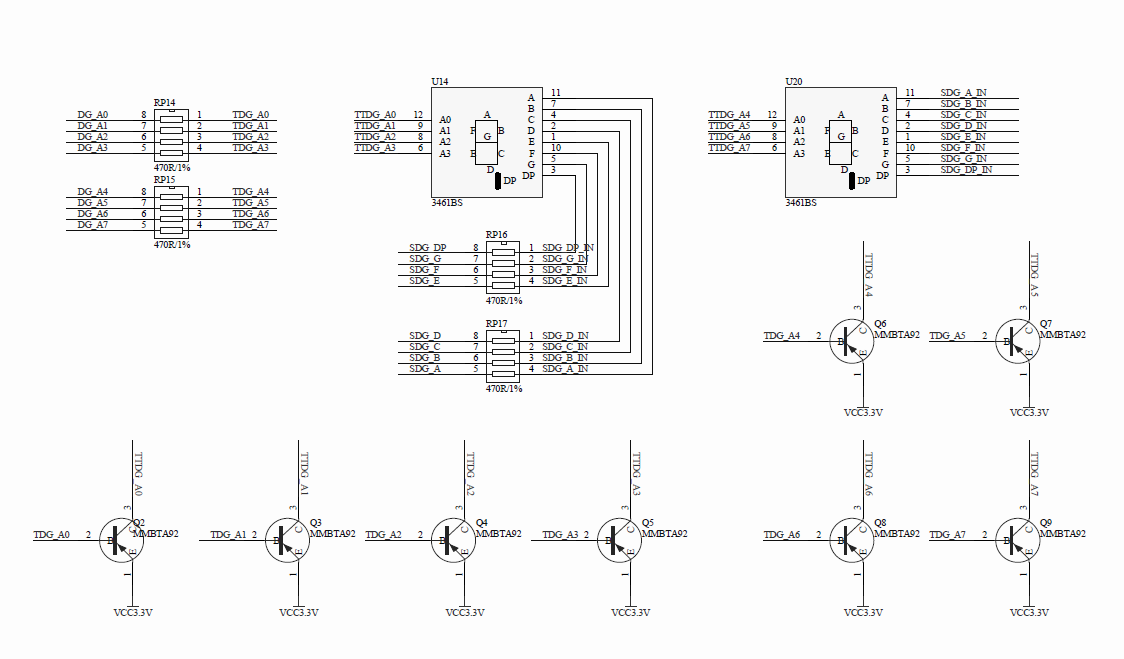

开发板数码管原理图设计如下,数码管一共是8个引脚,然后加上8个控制信号引脚,一共是16个引脚,如图16.2所示,其中SDG_DP、SDG_G、SDG_F、SDG_E、SDG_D、SDG_C、SDG_B、SDG_A是对应数码管的A,B,C,D,E,F,G,H(即点DP);DG_A0、DG_A1、DG_A2、DG_A3、DG_A4、DG_A5、DG_A6、DG_A7是八个数码管的八个控制引脚,也是低电平有效,当控制引脚为低电平时,对应的数码管有了供电电压,这样数码管才能点亮,否则无论数码管的段如何变化,也不能点亮对应的数码管。

3程序设计

数码管试验的FPGA管脚如下:

| 信号名 | 方向 | 管脚 | BANK | 端口说明 |

| DG_A0 | output | H1 | BANK35 | 第1个数码管位选信号 |

| DG_A1 | output | K3 | BANK34 | 第2个数码管位选信号 |

| DG_A2 | output | K2 | BANK35 | 第3个数码管位选信号 |

| DG_A3 | output | L3 | BANK34 | 第4个数码管位选信号 |

| DG_A4 | output | H5 | BANK35 | 第5个数码管位选信号 |

| DG_A5 | output | J5 | BANK35 | 第6个数码管位选信号 |

| DG_A6 | output | F4 | BANK35 | 第7个数码管位选信号 |

| DG_A7 | output | A9 | BANK16 | 第8个数码管位选信号 |

| SDG_A | output | J2 | BANK35 | 数码管段选A |

| SDG_B | output | G3 | BANK35 | 数码管段选B |

| SDG_C | output | H4 | BANK35 | 数码管段选C |

| SDG_D | output | G4 | BANK35 | 数码管段选D |

| SDG_E | output | M4 | BANK34 | 数码管段选E |

| SDG_F | output | L4 | BANK34 | 数码管段选F |

| SDG_G | output | L5 | BANK34 | 数码管段选G |

| SDG_DP | output | K5 | BANK34 | 数码管段选DP |

按键的FPGA管脚如下:

| 信号名 | 方向 | 管脚 | BANK | 端口说明 |

| S1 | input | E15 | BANK15 | 按下低电平有效 |

| S2 | input | D14 | BANK15 | 按下低电平有效 |

| S3 | input | C14 | BANK15 | 按下低电平有效 |

| S4 | input | B16 | BANK15 | 按下低电平有效 |

| S5 | input | B13 | BANK15 | 按下低电平有效 |

程序主要包括主程序、PLL时钟产生模块以及数码管显示模块,工程代码较简单,注释详细,具体内容可打开工程代码查看。

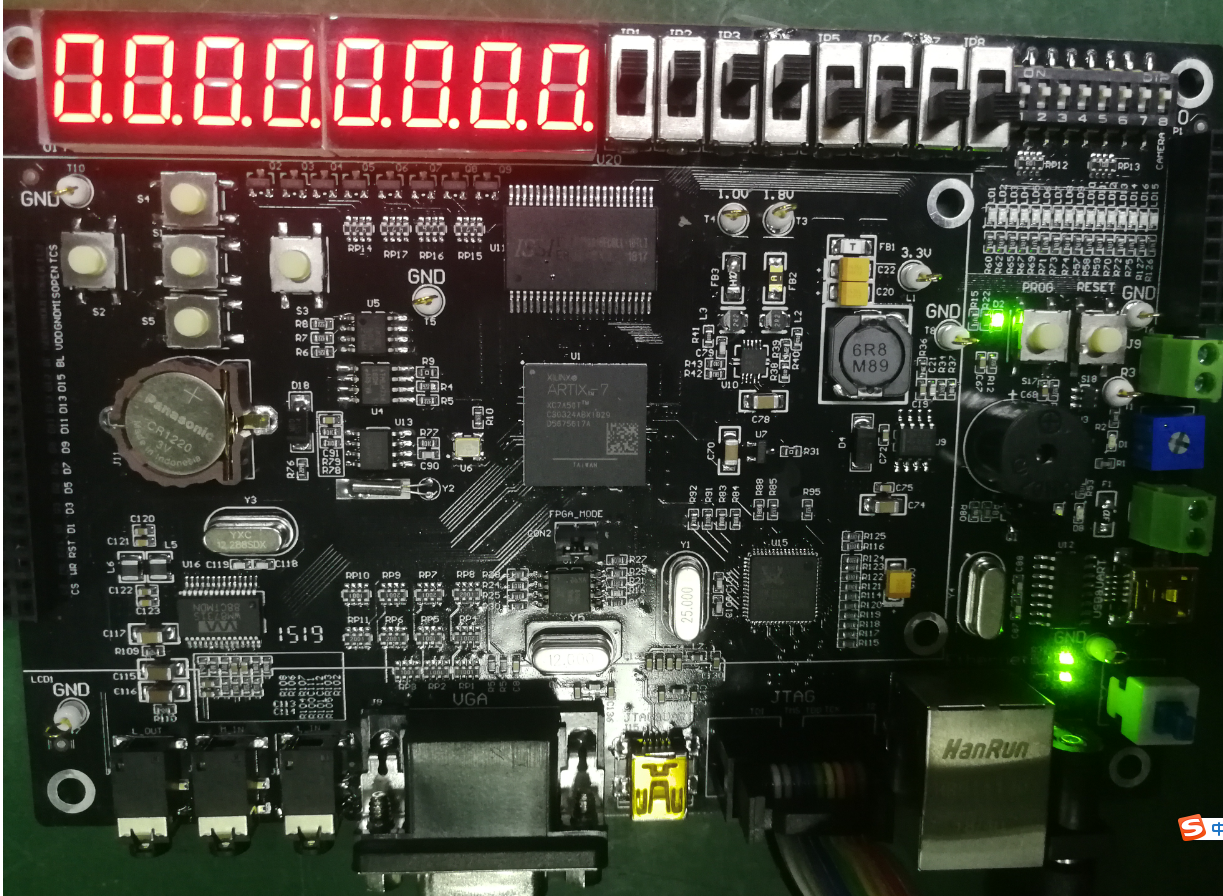

4.实验现象

将目录“... \at7_prj_06\at7_prj\at7_prj.runs\impl_1”文件夹下的 at7_prj.bit 文件下载到开发

板上,分别按住按键,则数码管显示相应的按键值。

部分代码展示:

/ module arykeyscan( input clk,//外部输入25MHz时钟信号 input rst_n,//外部输入复位信号,低电平有效 input[3:0] key_h,//4个行按键输入,未按下为高电平,按下后为低电平 output reg[3:0] key_v,//4个列按键输出 output reg[15:0] display_num//数码管显示数据,[15:12]--数码管千位,[11:8]--数码管百位,[7:4]--数码管十位,[3:0]--数码管个位 ); //------------------------------------- //列按键键值采样 wire[3:0] keyh_value;//列按键按下键值,高电平有效 sigkeyscanuut_sigkeyscan( .clk(clk),//外部输入25MHz时钟信号 .rst_n(rst_n),//外部输入复位信号,低电平有效 .key_h(key_h),//4个独立按键输入,未按下为高电平,按下后为低电平 .keyh_value(keyh_value)//行按键键值,高电平有效 ); //------------------------------------- //状态机采样键值 reg[3:0] nstate,cstate; parameter K_IDLE = 4'd0;//空闲状态,等待 parameter K_H1OL = 4'd1;//key_v[0]拉低 parameter K_H2OL = 4'd2;//key_v[1]拉低 parameter K_H3OL = 4'd3;//key_v[2]拉低 parameter K_H4OL = 4'd4;//key_v[3]拉低 parameter K_CHCK = 4'd5;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?