最近在使用ddr,开发的过程中出现了好多问题,特别是在仿真这一块,现在把遇到的问题记录一下。

在vivado中仿真DDR的时候,有一个关键的地方,就是添加DDR模型和参数。

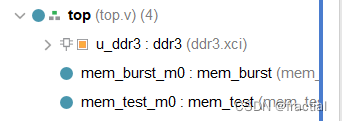

本文以黑金的开发例程来举例,程序主要包括三个部分:

DDR测试程序、DDR控制程序、DDR IP核。这个时候直接点仿真,得不到任何结果,还需要添加DDR模型。

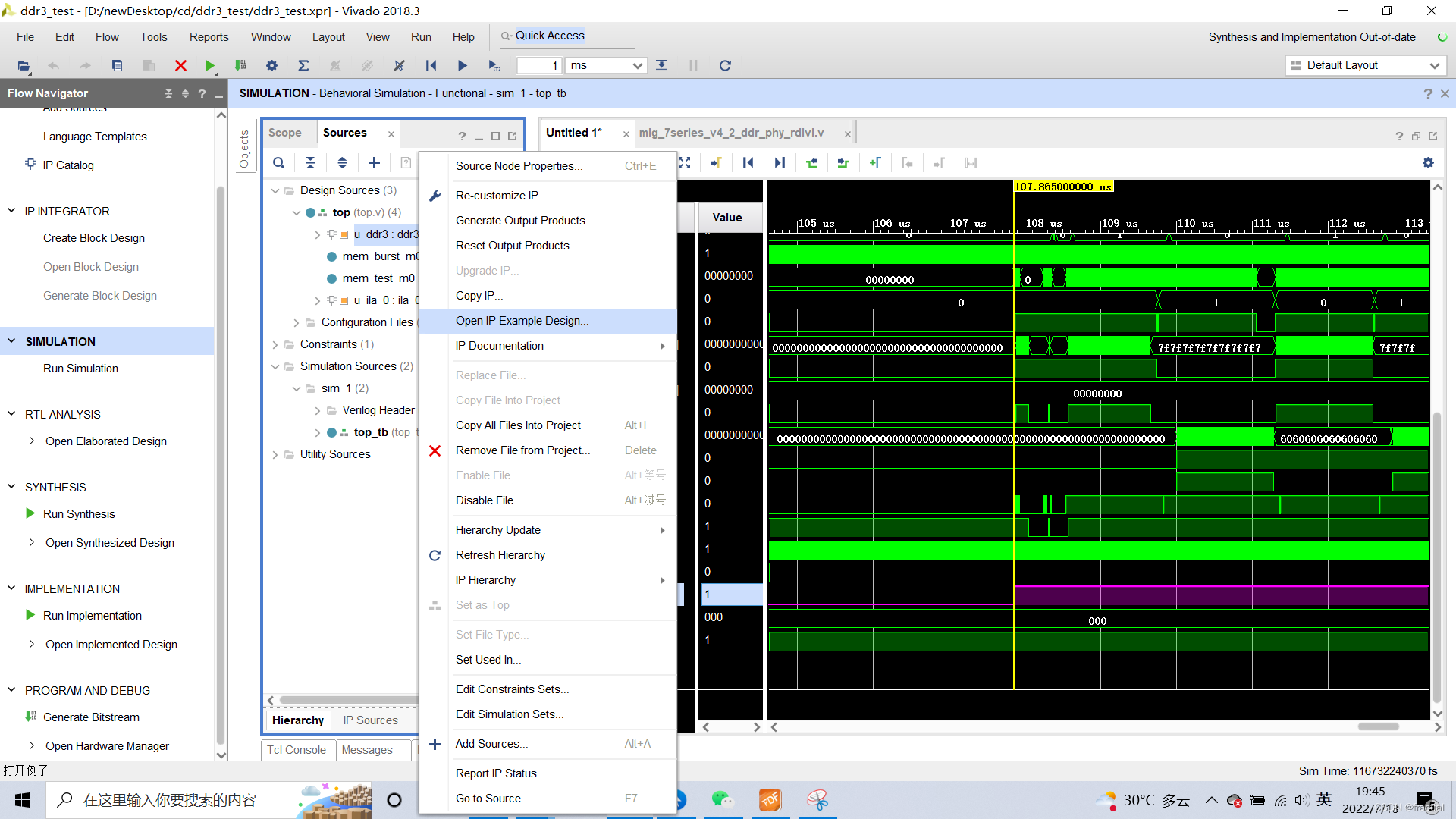

在设置好DDR mig ip核后,点击open example,即可得到以该IP核设置的DDR模型和参数。

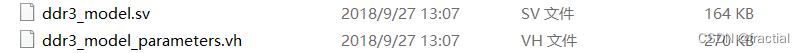

在example工程文件中搜索得到ddr3_model.sv,ddr3_model_parameter.vh两个文件。

把这两个文件加入到原工程的仿真文件里面,再编写一个testbench,即可开始仿真。

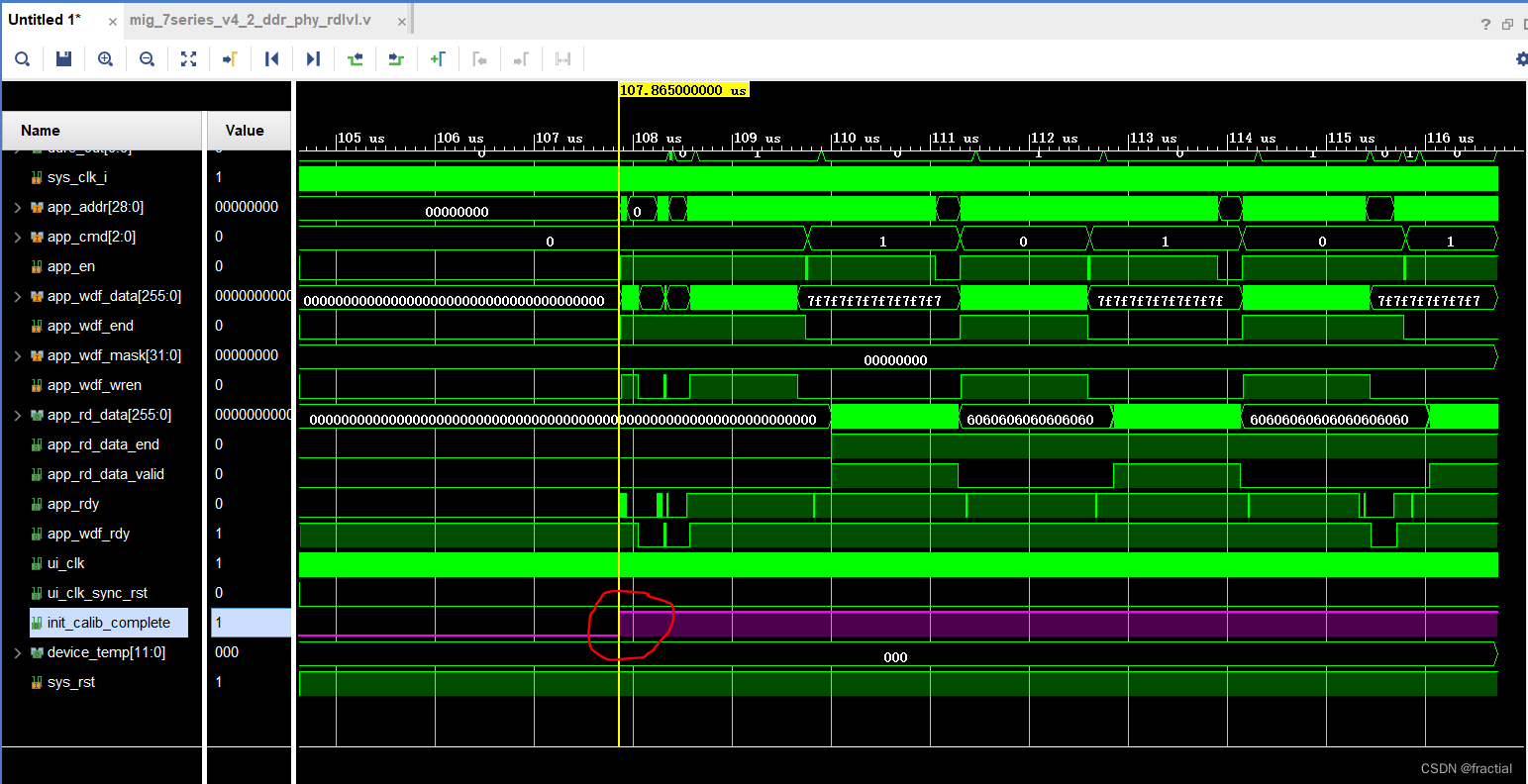

仿真结果如下:

最终init_calib_complete在107.865us的时候开始拉高,完成初始化。

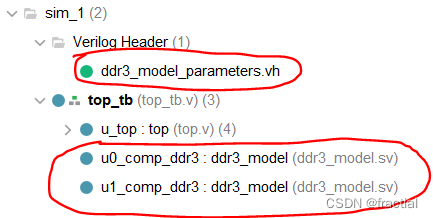

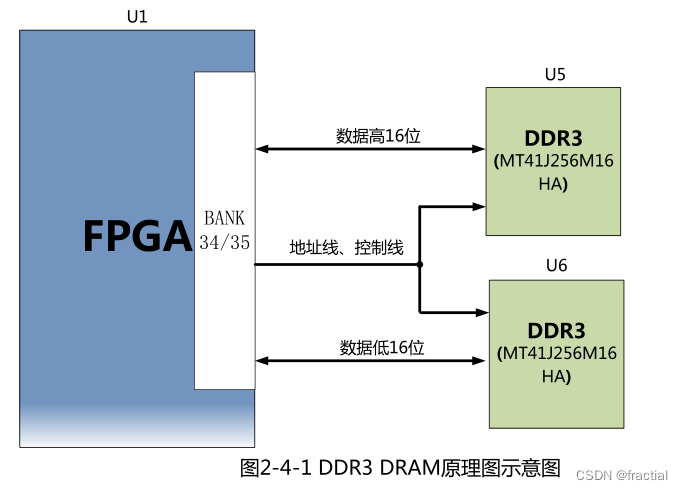

但在此过程中有一个要注意的地方,那就是如果DDR IP核里设置的位宽是32位,由于一个ddr model对应的位宽是16位,所以需要例化两个ddr model,否则init_calib_complete这个信号将会一直拉低,我刚开始仿真的时候就犯了这个错误,找了好久才找到原因。

上图即为黑金的连线,所以实际使用的时候要根据自身的情况来改变。所以testbench需要按照下面的方式来例化ddr model。

`timescale 1ps / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/13 18:58:51

// Design Name:

// Module Name: top_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module top_tb(

);

//

// Inouts

wire [31:0] ddr3_dq;

wire [3:0] ddr3_dqs_n;

wire [3:0] ddr3_dqs_p;

// Outputs

wire [14:0] ddr3_addr;

wire [2:0] ddr3_ba;

wire ddr3_ras_n;

wire ddr3_cas_n;

wire ddr3_we_n;

wire ddr3_reset_n;

wire [0:0] ddr3_ck_p;

wire [0:0] ddr3_ck_n;

wire [0:0] ddr3_cke;

wire [0:0] ddr3_cs_n;

wire [3:0] ddr3_dm;

wire [0:0] ddr3_odt;

//Differential system clocks

reg sys_clk_p;

reg sys_clk_n;

wire error;

reg rst_n;

//

initial

begin

rst_n = 1'b0;

#1000000

rst_n = 1'b1;

end

initial

begin

sys_clk_n = 1'b0;

sys_clk_p = 1'b1;

end

always sys_clk_n = #2500 ~sys_clk_n;

always sys_clk_p = #2500 ~sys_clk_p;

//

top u_top

(

// Inouts

.ddr3_dq (ddr3_dq[31:0] ), // (inout )

.ddr3_dqs_n (ddr3_dqs_n[3:0] ), // (inout )

.ddr3_dqs_p (ddr3_dqs_p[3:0] ), // (inout )

// Outputs

.ddr3_addr (ddr3_addr[14:0] ), // (output)

.ddr3_ba (ddr3_ba[2:0] ), // (output)

.ddr3_ras_n (ddr3_ras_n ), // (output)

.ddr3_cas_n (ddr3_cas_n ), // (output)

.ddr3_we_n (ddr3_we_n ), // (output)

.ddr3_reset_n (ddr3_reset_n ), // (output)

.ddr3_ck_p (ddr3_ck_p[0:0] ), // (output)

.ddr3_ck_n (ddr3_ck_n[0:0] ), // (output)

.ddr3_cke (ddr3_cke[0:0] ), // (output)

.ddr3_cs_n (ddr3_cs_n[0:0] ), // (output)

.ddr3_dm (ddr3_dm[3:0] ), // (output)

.ddr3_odt (ddr3_odt[0:0] ), // (output)

//Differential system clocks

.sys_clk_p (sys_clk_p ), // (input )

.sys_clk_n (sys_clk_n ), // (input )

.error (error ), // (output)

.rst_n (rst_n ) // (input )

);

//两个ddr model

ddr3_model u0_comp_ddr3

(

.rst_n (rst_n ),

.ck (ddr3_ck_p ),

.ck_n (ddr3_ck_n ),

.cke (ddr3_cke ),

.cs_n (ddr3_cs_n ),

.ras_n (ddr3_ras_n ),

.cas_n (ddr3_cas_n ),

.we_n (ddr3_we_n ),

.dm_tdqs (ddr3_dm[3:2] ),

.ba (ddr3_ba ),

.addr (ddr3_addr ),

.dq (ddr3_dq[31:16] ),

.dqs (ddr3_dqs_p[3:2] ),

.dqs_n (ddr3_dqs_n[3:2] ),

.tdqs_n ( ),

.odt (ddr3_odt )

);

ddr3_model u1_comp_ddr3

(

.rst_n (rst_n ),

.ck (ddr3_ck_p ),

.ck_n (ddr3_ck_n ),

.cke (ddr3_cke ),

.cs_n (ddr3_cs_n ),

.ras_n (ddr3_ras_n ),

.cas_n (ddr3_cas_n ),

.we_n (ddr3_we_n ),

.dm_tdqs (ddr3_dm[1:0] ),

.ba (ddr3_ba ),

.addr (ddr3_addr ),

.dq (ddr3_dq[15:0] ),

.dqs (ddr3_dqs_p[1:0] ),

.dqs_n (ddr3_dqs_n[1:0] ),

.tdqs_n ( ),

.odt (ddr3_odt )

);

endmodule

5939

5939

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?