文章目录

①参考文献

②直接截位误差

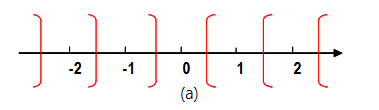

其实直接截位之所以出现直流分量可以这样直观的来认识:从matlab程序中也可以看出,对于FPGA信号截位来说,实际上就是向下取整;对于有符号数来讲,正数向下取整在数轴上是向原点零靠近,然后负数向下取整则是远离原点零了,这是因为负数以补码形式表示,它的补码所对应的无符号数经截位后向原点零靠近了,换算成有符号的负数时,则是远离原点零了。因此截位实际造成的效果是信号整体向负无穷方向平移了,即对于一个白噪声序列来讲,原本均值为零,截位后均值变为了负数。

③常见的几种截位方式

1、Truncate:直接截位,就是正数取floor,负数按绝对值取ceil(常用但有直流分量)

最简单,容易产生直流偏置,因为是向下取整,因此整数和负数对零点的偏移量不同,导致信号整体向下平移,在大信号时不明显,但在小信号时非常明显

MATLAB:

'假设我们要截低5位,a是待截数据

floor(32/32) = 1 floor(33/32) = 1 floor(48/32) = 1

floor(63/32) = 1 floor(64/32) = 2

floor(-32/32) = -1 floor(-33/32) = -2

floor(-48/32) = 2 floor(-63/32) = -2 floor(-64/32) = -2

b = floor(a/2^5);

Verilog:

32: 10'b00_0010_0000 33: 10'b00_0010_0001 48: 10'b00_0011_0000

63: 10'b00_0011_1111 64: 10'b00_0100_0000

-32: 10'b11_1110_0000 -33: 10'b11_1101_1111 -48: 10'b11_1101_0000

-63: 10'b11_1100_0001 -64: 10'b11_1100_0001

b = a[9:5]

2、Rounding:舍入截位,就是所有数按绝对值取四舍五入,相当于matlab 的round函数(常用且最精确)

①判断数据的符号;② 如果符号为正,则将数据加上2^ (n-1);③ 如果符号为负,则将数据加上2^(n-1)-1;④ 截掉数据的低n 位。

MATLAB:

'假设我们要截低5位,a是待截数据

round(32/32) = 1 round(33/32) = 1 round(48/32) = 2

round(63/32) = 2 round(64/32) = 2

round(-32/32) = -1 round(-33/32) = -1

round(-48/32) = -2 round(-63/32) = -2 round(-64/32) = -2

b = round(a/2^5);

Verilog:

32: 10'b00_0010_0000 33: 10'b00_0010_0001 48: 10'b00_0011_0000

63: 10'b00_0011_1111 64: 10'b00_0100_0000

-32: 10'b11_1110_0000 -33: 10'b11_1101_1111 -48: 10'b11_1101_0000

-63: 10'b11_1100_0001 -64: 10'b11_1100_0001

if(a >= 0)

b1 = a + 10'b00_0001_0000

b = b1[9:5]

else if(a < 0)

b1 = a + 10'b00_0000_1111

b = b1[9:5]

3、负数直接截位后+1,就是所有数都按绝对值取floor(常用且较精确)

MATLAB:

if a<0

b=floor(a/2^5)+1;%截去低5位后加1

else

b=floor(a/2^5);%直接截位

end

//即在直接截位的基础上修正了一下负数,直接截位导致信号整体向下偏移以1,现在给负数加上1,则无任何偏移

Verilog:

32: 10'b00_0010_0000 33: 10'b00_0010_0001 48: 10'b00_0011_0000

63: 10'b00_0011_1111 64: 10'b00_0100_0000

-32: 10'b11_1110_0000 -33: 10'b11_1101_1111 -48: 10'b11_1101_0000

-63: 10'b11_1100_0001 -64: 10'b11_1100_0001

if(a >= 0)

b = a[9:5];

else

b = a[9:5] +1'b1;

end

4、负数取绝对值后再截位

if a<0

b=-floor(-a/2^5);%负数取绝对值后截去低5位再变回原来符号

else

b=floor(a/2^5);%直接截位

end

后三种方式都是对称截位,即正负数距零点的位置相同,因此都不会出现直流分量,其中舍入截位的精度最高。

④FPGA里的几种截位方式

Truncation:直接截位

Non-symmetric Rounding to Positive:先把数据加上0.5,然后舍弃数据的低位。相当于matlab的floor(x+0.5)

Non-symmetric Rounding to Negative:先把数据加上0.4999999…,然后舍弃数据的低位.。相当于matlab的ceil(x-0.5)

Symmetric Rounding to Highest Magnitude:相当于matlab 的round函数,取整的时候按小数位四舍五入

Symmetric Rounding to Zero:这种截位方式不会发生溢出,取整的时候按小数位四舍五不入,前面是五入

Convergent Rounding to even 和Convergent Rounding to odd:收敛舍入选择中点的舍入方向为奇数或偶数,而不是正数或负数。 这可能是有利的,因为中点舍入方向决策的平衡基于奇数或偶数出现的概率,即使在输入信号的均值远离零时,在大多数情况下这通常是相等的。 该功能是通过添加舍入常数来实现的,就像在其他模式中一样,然后检查 LSB 上的特定模式以检测中点并强制 LSB 为零(舍入到偶数)或 1(舍入到奇数) ) 当出现中点时。

⑤ MATLAB的几种取整方式

⑥cic滤波器里的位宽扩展

An Economical Class of Digital Filters for Decimation and Interpolation

高速cic插值滤波器的位宽与优化

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?