一.问题

最近项目遇到一个问题,用了一片XC7Z7020,由于功能简单没有外扩DDR,导致自动生成的fsbl.elf文件无法引到jtag烧写bin文件到flash,修改vitis生成的sdk后解决了此问题,具体方法如下。

二.软件环境

1.软件版本:Vivado Vitis2023.1

三.解决方法

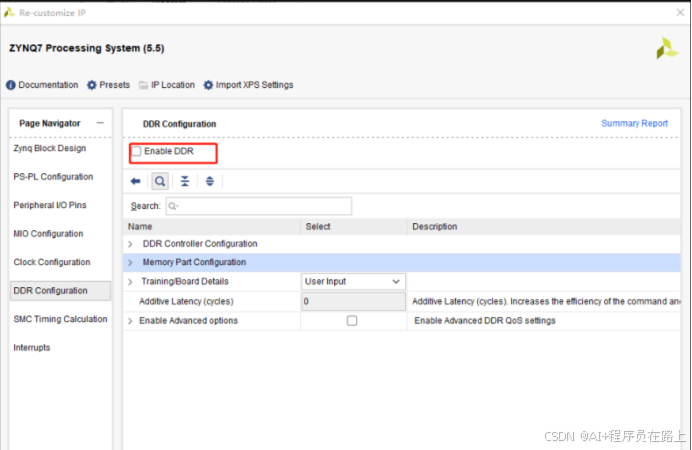

第一步: 在Vivado的ZYNQ Block Design时候不配置DDR

第二步: 在Vitis中:

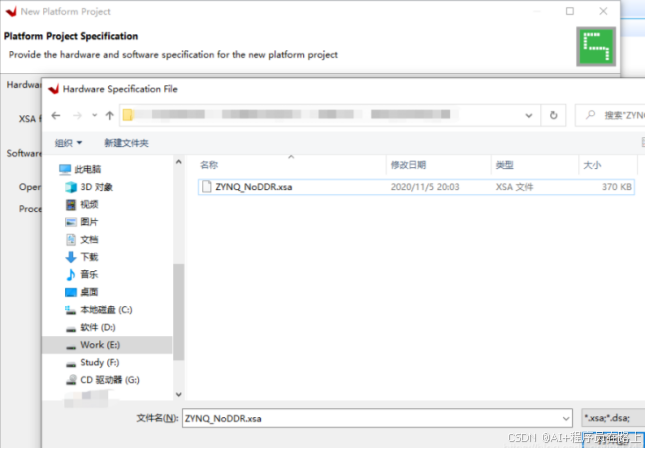

1.在Vitis中新建Platform,选择xsa文件:

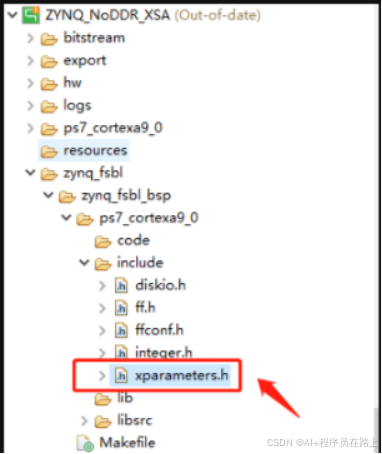

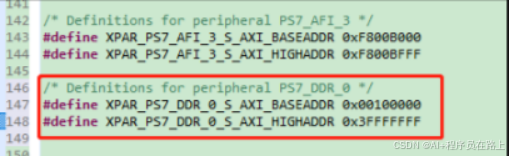

2.在xparameters.h中添加DDR的地址空间定义(更新xsa后需要重新修改),如下:

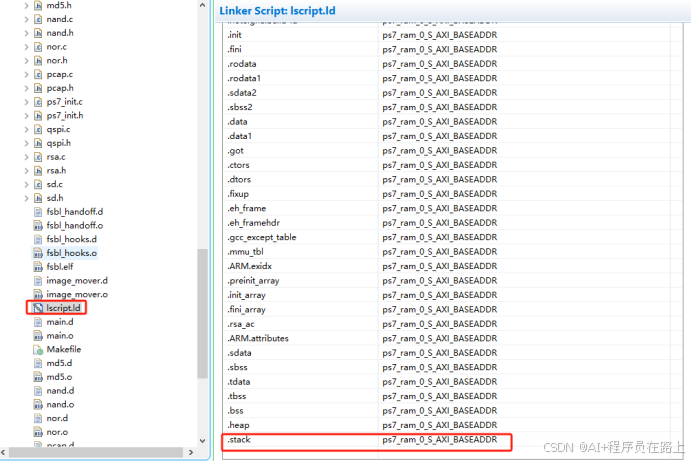

3.修改链接文件,修改每个段都到ram_0,因为ram_1空间全部给到应用程序

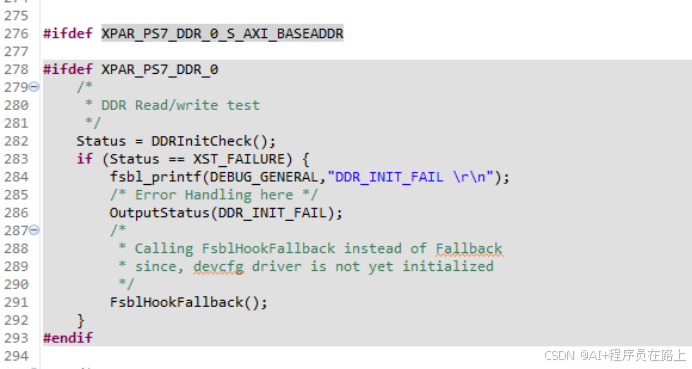

4.修改fsbl工程的main.c,增加XPAR_PS7_DDR_0条件编译

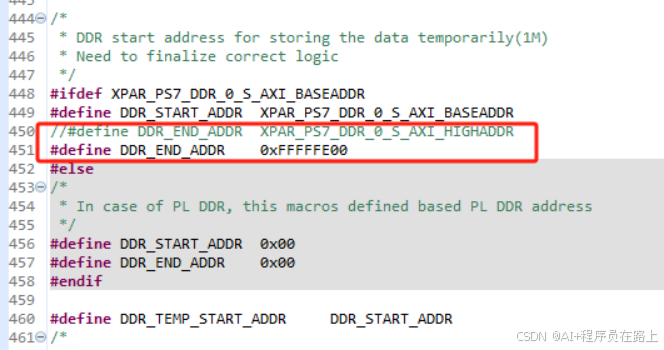

5.修改fsbl.h,重定义DDR_END_ADDR的宏

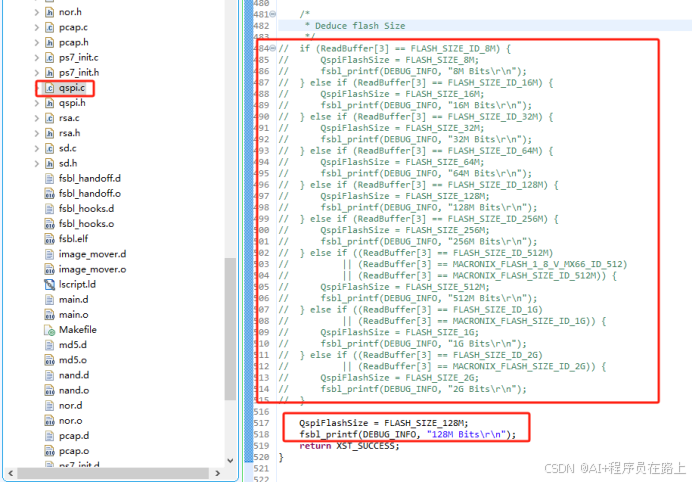

6.修改qspi.c,注释掉FLASH大小选择,写成128M

7.编译修改好的Platform

8.新建Application工程(此处可新建Helloworld工程作为示例)

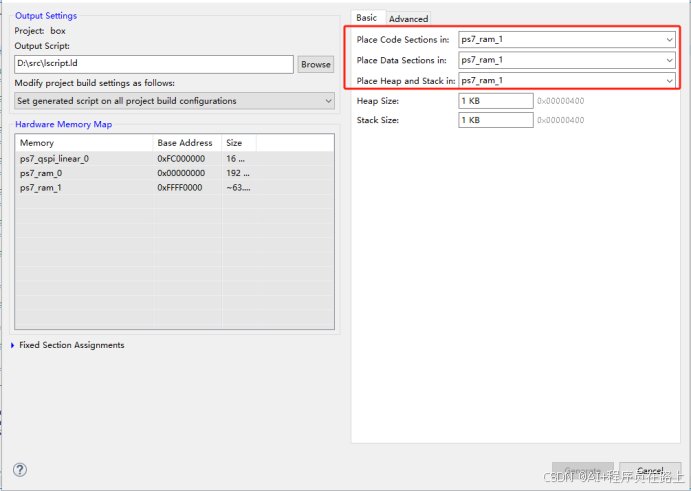

9.修改(或者新建)Application工程的链接脚本,将ram_1空间全部给到应用程序:

11.编译Application工程

12.vitis直接下载程序(用vivado下载也可以)

6163

6163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?