1. 背景资料

Zc706评估板核心是Zynq-7000 XC7Z045-2FFG900C AP SoC,Ax 7Z1000核心为XC7Z100-2FFG900,与xc7z045只有频率的不同,因此在核心板相同的情况下可使用同一版本的uboot。对于Zynq-7000系列的板子来说,其核心板配置基本相同 ,主要差别在扩展板上的外设不同,这就导致我们在使用其他板子时可能需要根据自己的需求定制设备树(DTS)文件,然后使用Petalinux来简化编译生成启动镜像的过程。

2. Qemu for Xilinx编译

参考文献: Qemu-Xilinx编译 Qemu-Zynq7000

2.1 源码下载

git clone git://github.com/Xilinx/qemu.git

2.2 编译安装

cd qemu

./configure --target-list="aarch64-softmmu,microblazeel-softmmu" --enable-fdt --disable-kvm

make -j4

#编译成功会在qemu/aarch64-softmmu下会生成qemu-system-aarch64

2.3 运行

本部分以qemu模拟运行zc706为例:

下载地址:zc706镜像

#解压zc706.tar.gz到zc706文件夹

tar xvf zc706.tar.gz -C zc706

#在qemu目录下

./aarch64-softmmu/qemu-system-aarch64 -M arm-generic-fdt-7series -machine linux=on -serial /dev/null -serial mon:stdio -display none -kernel ../zc706/uImage -dtb ../zc706/devicetree.dtb --initrd ../zc706/uramdisk.image.gz

#登录---用户名:root 无密码

#结果显示

root@zc706-zynq7:~# cat /proc/cpuinfo

processor : 0

model name : ARMv7 Processor rev 0 (v7l)

BogoMIPS : 1640.03

Features : half thumb fastmult vfp edsp neon vfpv3 tls vfpd32

CPU implementer : 0x41

CPU architecture: 7

CPU variant : 0x0

CPU part : 0xc09

CPU revision : 0

processor : 1

model name : ARMv7 Processor rev 0 (v7l)

BogoMIPS : 1659.69

Features : half thumb fastmult vfp edsp neon vfpv3 tls vfpd32

CPU implementer : 0x41

CPU architecture: 7

CPU variant : 0x0

CPU part : 0xc09

CPU revision : 0

Hardware : Xilinx Zynq Platform

Revision : 0000

Serial : 0000000000000000

#退出QEMU,先按Ctrl+A,然后按X

3. Xilinx板子的启动流程:

参考:FSBL简介

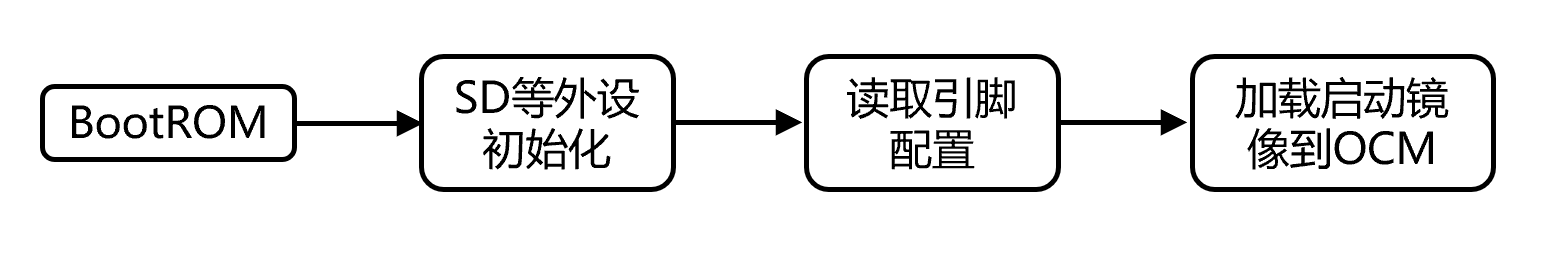

3.1 阶段0----BootRom:

阶段0,又称为 BootROM 阶段。BootRom就是一块只读内存,有点像主板上的启动芯片。板子上电后第一步就是读取BootRom中的代码,这是由硬件决定的,我们无法修改其代码。那么BootRom中的代码是做什么用的呢?在zynq中,它主要是要从外部存储设备中读取启动镜像。在zynq中,引入了引脚启动的机制。Zynq 拥有5个可以进行配置的 MIO 引脚,是 MIO[6:2],在硬件形式上就表现为5个跳线帽,可以分别接 GND 或 3V3 的高电平。它们的作用如下:

- MIO[2] :选择 JTAG 模式

- MIO[5:3] :选择启动方式,包括 SD 卡,QSPI Flash 等

- MIO[6] : PLL 使能控制

通过不同的引脚作用说明可以发现,当 JTAG 不起作用是,就需要通过改变 MIO[5:3] 的连接来实现从 SD 卡等不同的存储介质启动。

而 BootROM 最重要的作用就是通过读取 MIO[6:2] 的引脚配置情况,决定从何种介质中加载阶段1需要使用的启动镜像。当然在加载之前,BootROM 会先完成对 SD 卡,NAND,NOR,QSPI Flash 等的初始化,从而使得ARM 核能够成功访问并使用这些外设。BootROM 在完成以上任务的同时,也会对安全模式等运行模式进行配置,

BootROM 在从外部存储设备读取了启动镜像后,通常会把它进行加载到 OCM 中。OCM,On Chip Memory,是Zynq 中 ARM 内核的片上存储器,也叫片上内存。自此之后,BootROM 阶段的启动任务就算是圆满结束了,接下来 BootROM 阶段就把控制权转移到了阶段1手中。

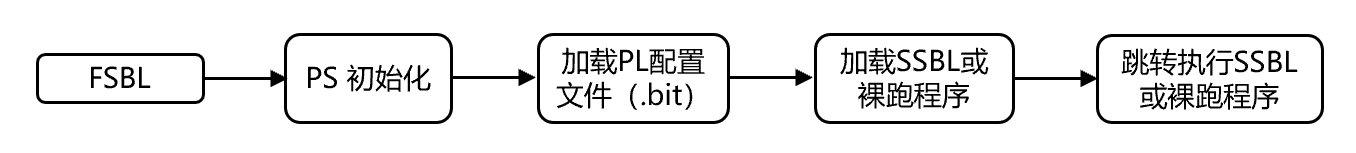

3.2 阶段1:FSBL

FSBL,(First Stage Boot Loader),就是 BootROM 加载到 OCM 中的启动镜像(BOOT.BIN)。FSBL 完成的任务是 Zynq 启动过程中的关键一环,可以分为以下4项:

- 完成 PS 的初始化

- 加载 PL 的bit流文件,完成 PL 配置

- 加载 SSBL 引导程序或是ARM的裸跑程序到 DDR

- 跳转执行 SSBL 或裸跑程序

FSBL 的任务如上所示,整个思路还是非常清晰的。第1步就是对 PS 端初始化,包括 DDR,MIO 等。第2步就是PL的配置,也就是传统的 FPGA 下载 bit 流的过程,但要注意的是, Zynq 的非 JTAG 模式下,PL 是无法直接自行配置的。第3步是加载 SSBL 或裸跑程序到 DDR 内存中,其中 SSBL,Second Stage Boot Loader,是在 Zynq 需要运行操作系统时才进行加载。而像我们入门学习时做的点亮 LED 灯实验,就只是属于裸跑程序。最后第4步,ARM 会跳转到 DDR 中执行所加载的程序。所以 FSBL 阶段的运行思路是很好理解的。

有个疑问:既然fsbl已经将u-boot加载到了DDR内存中,那么uboot中的第一阶段代码也就是将uboot从flash加载到RAM中,以及初始化DDR的这几步还有必要吗?

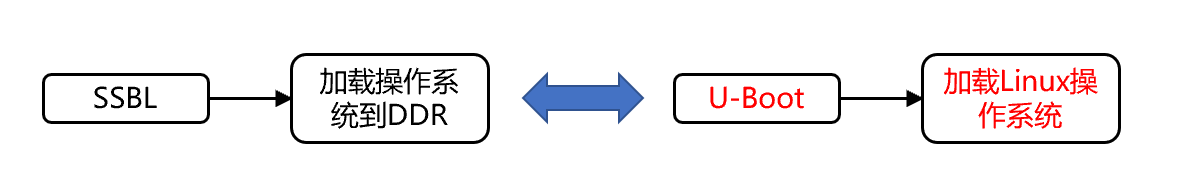

3.3 阶段2:SSBL

SSBL 在 Zynq 的启动过程中是可选的一个阶段,就像所提到的点亮 LED 实验,包括一些其他的比较小型的程序,如果不需要用到操作系统的话,那么 Zynq 的启动流程到 FSBL 阶段就足够了。因此,SSBL 是面向于需要运行操作系统的应用场合。相信熟悉操作系统启动知识的朋友到这里应该很清楚了,SSBL 就是操作系统在启动过程中的引导程序 boot loader。对于 Linux 而言,Zynq 的 SSBL 阶段和 u-boot 的作用是相同的。具体来说,SSBL 的作用就是将 Zynq 所需要的操作系统加载到 DDR 内存之中

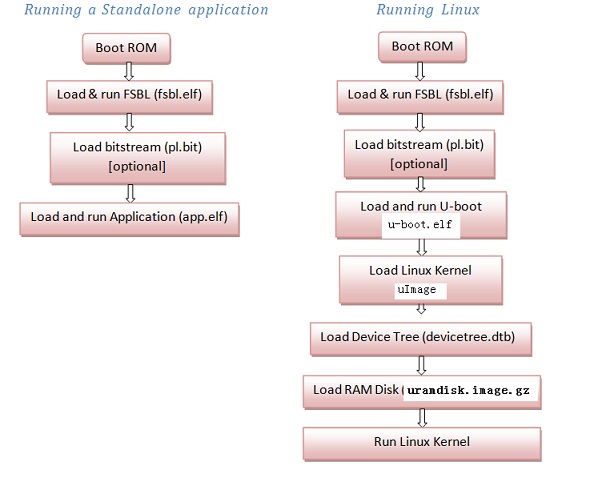

Xilinx的boot分区文件解析:

Xilinx zynq采用SD卡启动,sd卡需要分为两个分区:boot分区和根文件系统分区,其中boot分区需要格式化为FAT16/32的格式的,根文件系统分区设置成为ext4的即可。

boot分区中需要的文件:

-

BOOT.BIN: 该文件需要使用Vivado的SDK工具生成,它一般由fsbl.elf, u-boot.elf组成,fsbl.elf是硬件相关的,与开发板的管脚连线以及IP设计有关,也是由Vivdo生成的。u-boot.elf可以通过u-boot的源码编译而来。

-

devicetree.dtb: 设备树文件

-

uImage: 编译生成的内核文件

-

uramdisk.image.gz: 根文件系统,有个疑问,它和根文件系统分区什么关系?

-

uEnv.txt: 可选,主要描述了boot的配置信息,内容格式如下:

uenvcmd=run linaro_sdboot linaro_sdboot=echo Copying Linux from SD to RAM... && \ fatload mmc 0 0x3000000 ${kernel_image} && \ fatload mmc 0 0x2A00000 ${devicetree_image} && \ if fatload mmc 0 0x2000000 ${ramdisk_image}; \ then bootm 0x3000000 0x2000000 0x2A00000; \ else bootm 0x3000000 - 0x2A00000; fi bootargs=console=ttyPS0,115200 root=/dev/mmcblk0p2 rw earlyprintk rootfstype=ext4 rootwait

4. AX7021的BOOT.BIN文件的制作:

-

首先是fsbl.elf的制作

由于这部分是硬件相关的,所以它和开发板的电路设计以及处理器引脚的连接相关,不同的开发板需要借助Vivado来生成不同的fsbl.elf文件。

具体步骤参考黑金官方教程

-

u-boot.elf的制作

这个可以直接从源码编译而来,因为黑金的ax7021开发板采用了与Xilinx的zc706官方开发板相同架构的zynq7000芯片,所以理论上二者的uboot是可以共用的。所以我直接以zc706为原型,编译出u-boot.elf文件。

-

现在两个文件都有了,接下来要做的就是利用Xilinx的SDK工具生成BOOT.BIN文件,具体参见:如何制作BOOT.BIN文件

5. U-Boot for Xilinx编译

参考文献: UBoot编译指南

5.1 u-boot源码下载

#xilinx自己维护了一个u-boot的源码仓库,里面加入了很多xilinx板子的配置文件

git clone https://github.com/Xilinx/u-boot-xlnx.git

5.2 编译

#zynq

export CROSS_COMPILE=arm-linux-gnueabihf-

export ARCH=arm

cd u-boot-xlnx

make distclean

make xilinx_zynq_virt_defconfig

export DEVICE_TREE="zynq-zc706"

make

5.3 运行(暂不成功)

#在qemu目录下

./aarch64-softmmu/qemu-system-aarch64 -M arm-generic-fdt-7series -nographic -m 512M -kernel ../u-boot-xlnx/u-boot

6. PetaLinux使用

PetaLinux 是构建于Yocto Linux 发行版的一组高级命令。PetaLinux 工具让您能够为赛灵思处理器系统定制、构建和部署嵌入式 Linux 解决方案/Linux 镜像。此工具专为提高设计效率而量身定制,并可与赛灵思硬件设计工具(如 Vivado)一起使用,以便于轻松地开发面向 Zynq® UltraScale+™ MPSoC、Zynq®-7000 SoC 和 MicroBlaze™ 的 Linux 系统。

简单说来,它是一组简化的命令,可用于快速轻松地为赛灵思开发板制作定制的 Linux 系统/镜像!

注意:参考Xilinx官方PetaLinux用户手册(UG1144),最好使用最新的官方操作手册(v2020.2)

petalinux生成启动镜像的基本步骤:

#同make mrproper,清除所有文件

$ petalinux-build -x mrproper

#创建工程

$ petalinux-create --type project --template zynq --name

<PROJECT_NAME>

#导入硬件配置文件,这里是.xsa文件

$ petalinux-config --get-hw-description design_1_wrapper.xsa

#编译工程

$ petalinux-build

#生成.BIN格式的启动镜像

$ petalinux-package --boot --fsbl <FSBL image> --fpga <FPGA bitstream> --u-boot

2145

2145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?