目录

1.前言

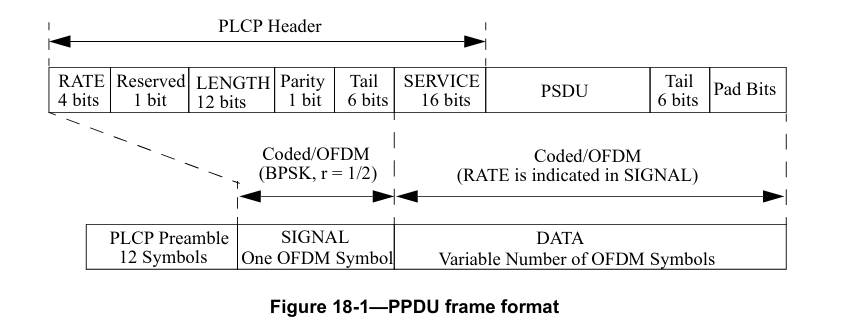

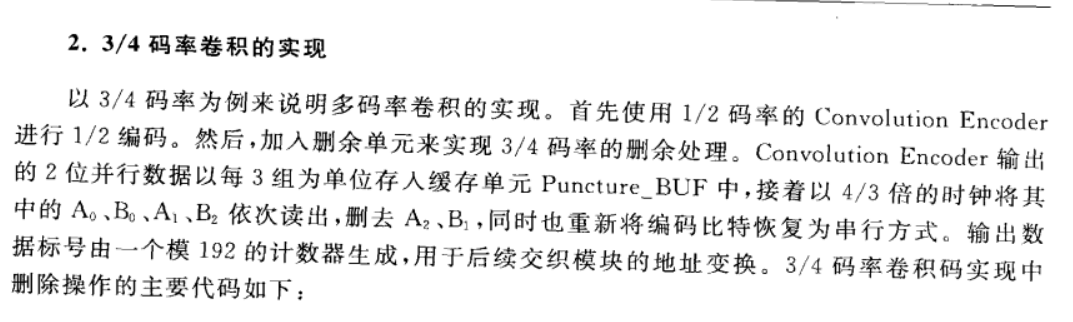

至此,通过前面的文章讲解,对于OFDM 802.11a的发射基带的一个完整的PPDU帧的所有处理已经全部完成,其结构如下图所示:

PPDU帧结构

PPDU帧结构

接下来还需要完成两个最为核心的模块,一是主控模块,负责与MAC进行数据交互、控制数据流按照上图所示的帧结构进行输出;二是在处理数据时,我们采用的是125M的时钟,而DAC的时钟是20M的,我们需要对数据流进行降频处理,使125M的突发式数据流变为20M的连续数据流。

2.AXI-Stream FIFO时序

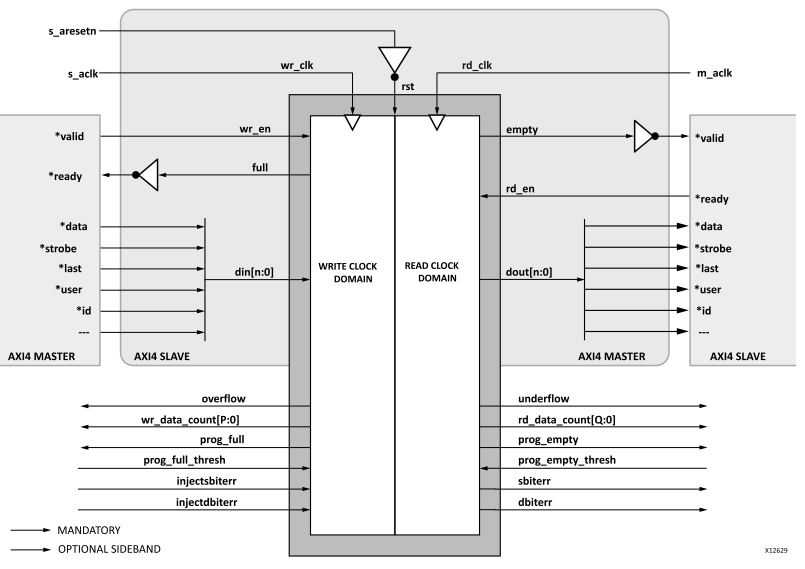

我们在数据处理时,一直使用的都是AXI-Stream协议,所以使用AXI-Stream FIFO进行跨时钟域都不需要再进行额外的操作,直接连上就能用。但是为了让大家对AXI-Stream协议有更深的理解,以及掌握AXI-Stream FIFO的使用方法,接下来还是详细讲讲AXI-Stream FIFO这个IP核。其输入输出形式如下:

AXI-Stream FIFO

在AXI协议中,数据通过写通道实现master到slave的传输,读通道实现slave到master的传输。因此,在FIFO IP核中,接收数据的端口S_AXIS用来将数据写入IP核,而发送数据的端口M_AXIS用来将数据读出IP核。

举个生活中的例子来让大家便于理解FIFO:在数据的传输中当读速率慢于写速率时,FIFO便可被用作系统中的缓冲元件或队列,类似于水流经过一个缓冲区,上游水流速度快,下游水流速度慢,部分水就可以被缓存在中间的缓冲区。

流水类比FIFO

AXI接口协议使用双向valid和ready握手机制。数据源使用valid信号来显示何时在信道上可获得有效数据或控制数据。数据目的地使用ready信号来显示何时可以接受数据。

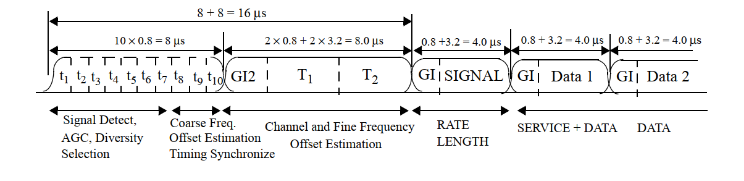

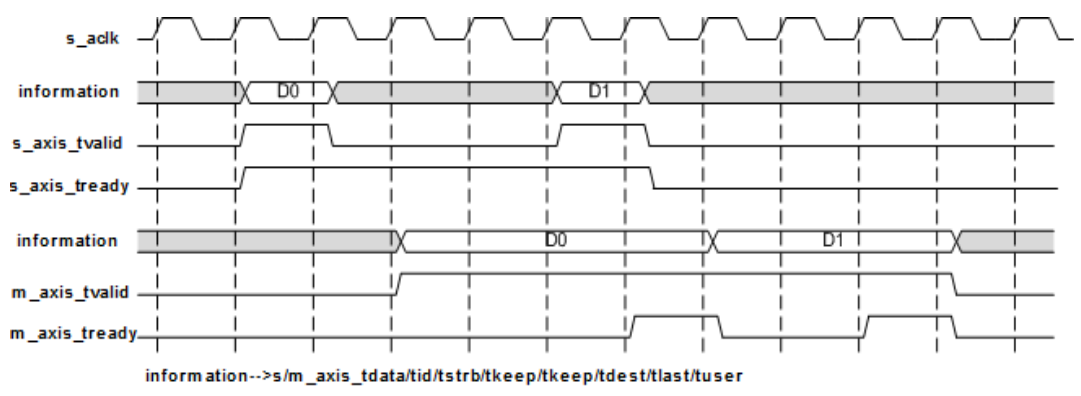

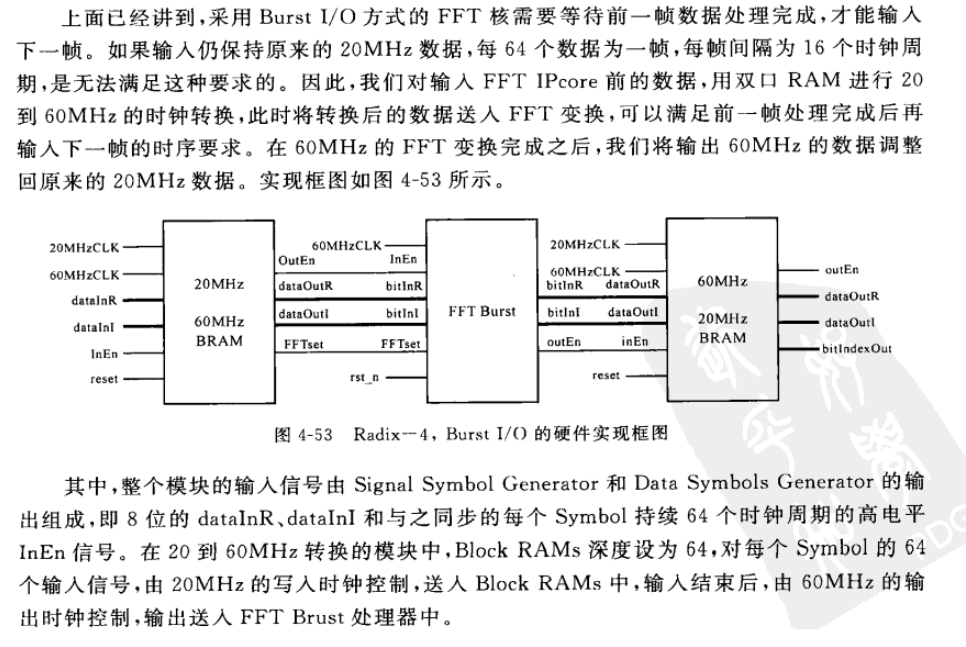

下图显示了AXI4-Stream FIFO的写入和读取操作的示例时序图:

AXI-Stream FIFO时序图

在上图中,数据源生成valid信号以指示数据何时可用。目的地生成ready信号以指示其可以接受数据,并且仅当有效信号和就绪信号均为高时才发生传输。

AXI FIFO是普通FIFO的应用,它们之间的许多行为是相同的。ready信号是根据 FIFO 中的空间可用性生成的,并保持在高电平以允许写入FIFO。仅当FIFO中没有空间可供执行额外写入时,ready信号才会拉低。 valid信号是根据FIFO中数据的可用性生成的,并保持为高电平以允许从FIFO执行读取。仅当没有数据可供从FIFO读取时,valid信号才会拉低。数据信号被映射到本机接口 FIFO 的 din 和 doout 总线。AXI FIFO 的宽度是通过连接 AXI 接口的所有数据信号来确定的。 数据信号包括除有效和就绪握手信号之外的所有 AXI 信号。

AXI FIFO Derivation

3.AXI-Stream FIFO配置信息

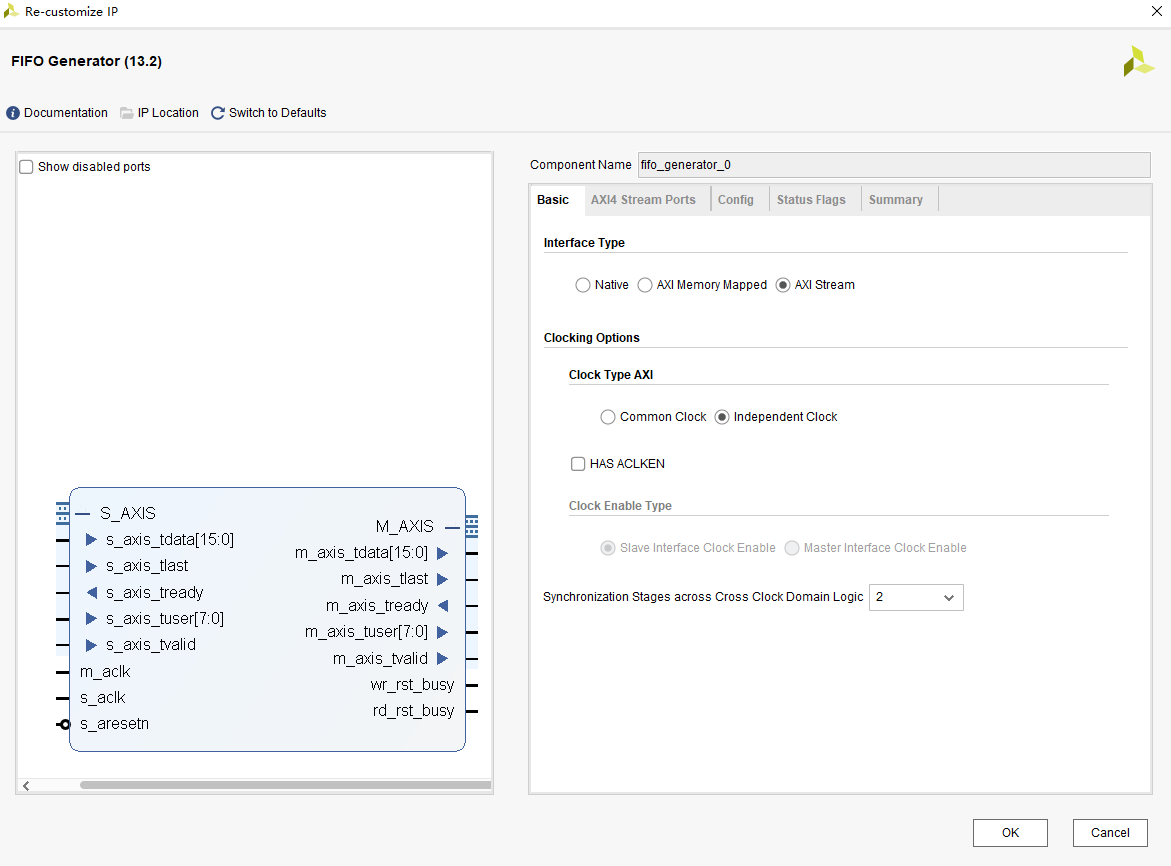

如下图所示,是IP核的配置界面:

FIFO配置界面

关于IP核中各个信号的详解,可翻阅官方手册,以下对该实验中所需信号进行解释:

Basic:

Interface Type : FIFO的模式,选择AXI-Stream;

Independent clocks:独立时钟设置,该实验需要使用异步时钟;

其余保持默认即可。

AXI-Stream Ports:

TDATA NUM BYTES:选择两个字节,因为IFFT输出是16bit;

TUSER WIDTH:设置为8;

TLAST:勾选;

其余保持默认即可。

Config:

FIFO depth:FIFO深度,可选范围16-32768,必须为2的整数次幂,根据需要设定为512,因为125/20 * 80=500;

其余保持默认即可。

配置好,接口如下所示:

AXI-Stream FIFO

4.时钟控制模块MMCM

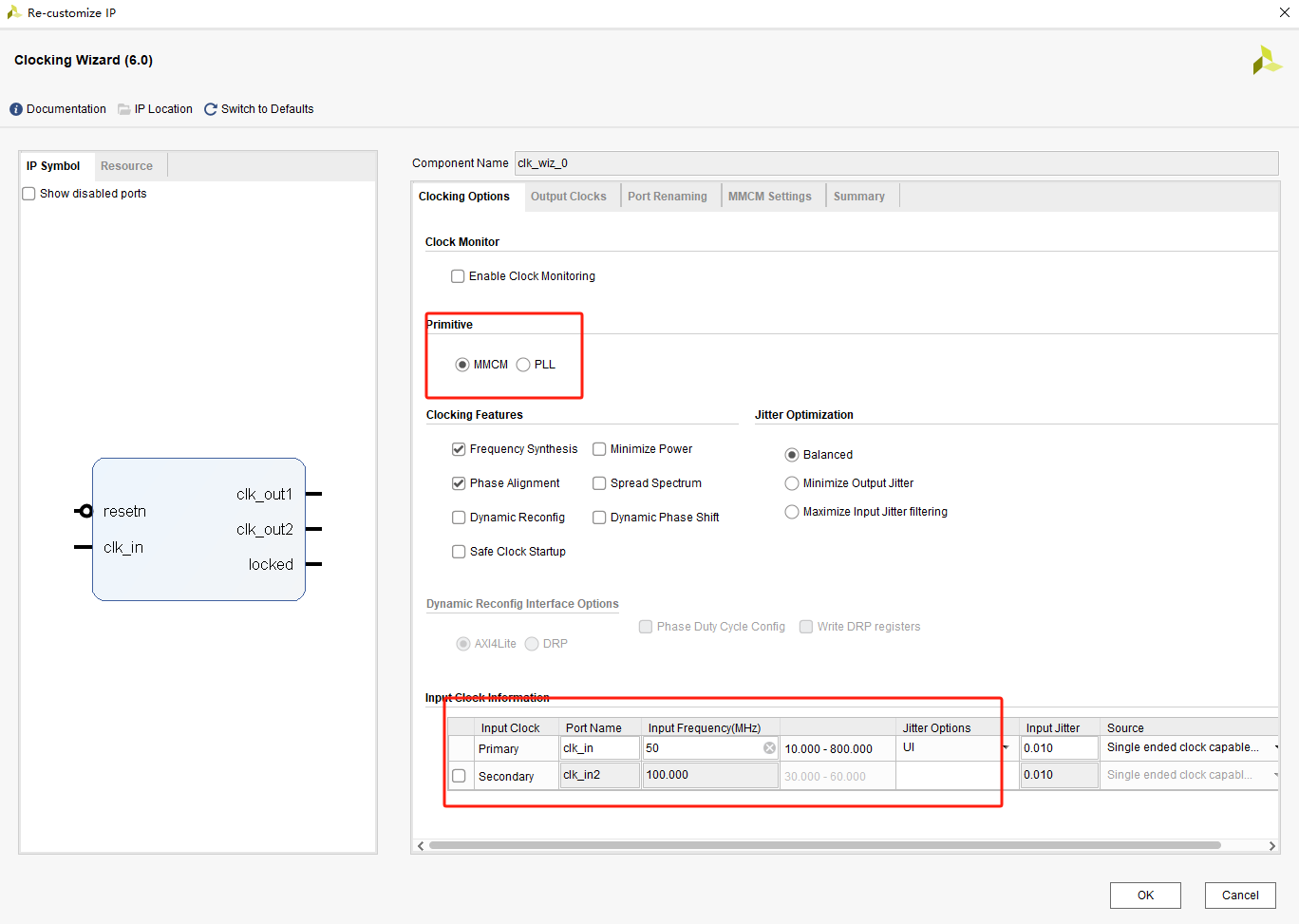

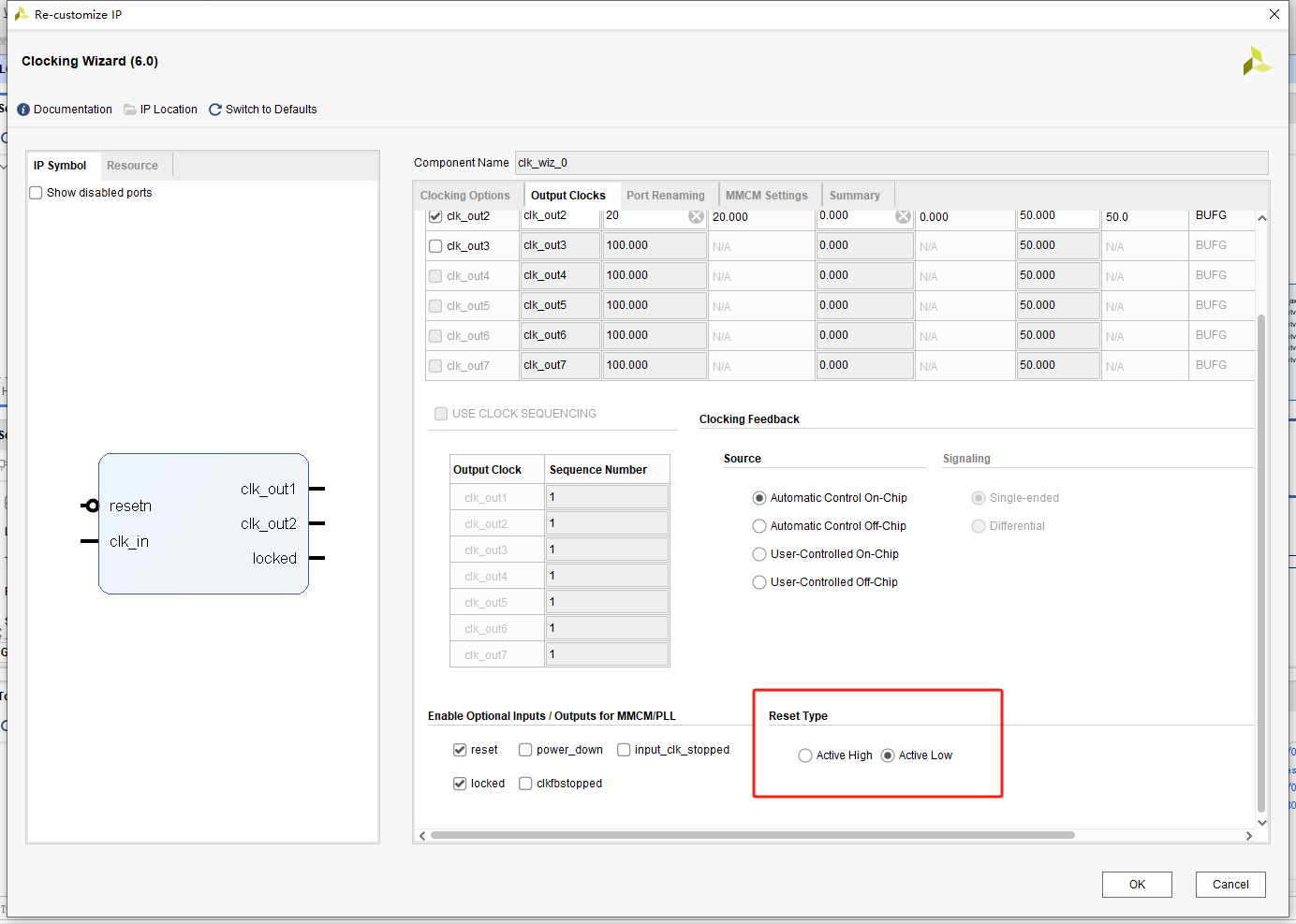

设计采用的开发板为ZYNQ7020,芯片是xc7z020clg400-1,板载时钟为50M,需要通过锁相环得到125M和20M的时钟。Clocking Wizard IP核的配置界面如下:

Clocking Options

Clocking Options:选择MMCM,输入时钟填写50M。

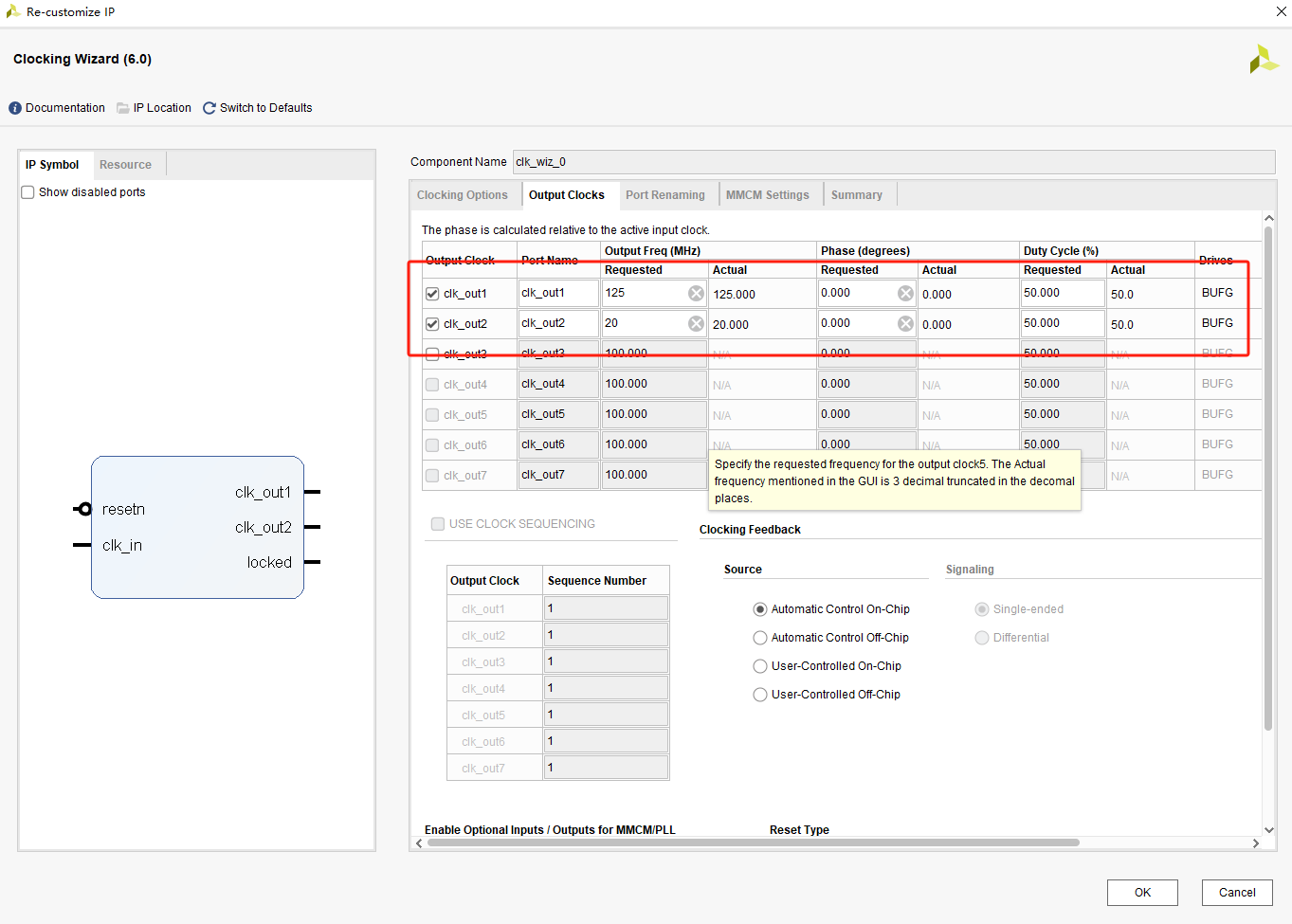

clk_out为125M,clk_out2为20M

低电平复位

Output Clocks:填写clk_out为125M,clk_out2为20M。并选择低电平复位。

5.ModelSim仿真

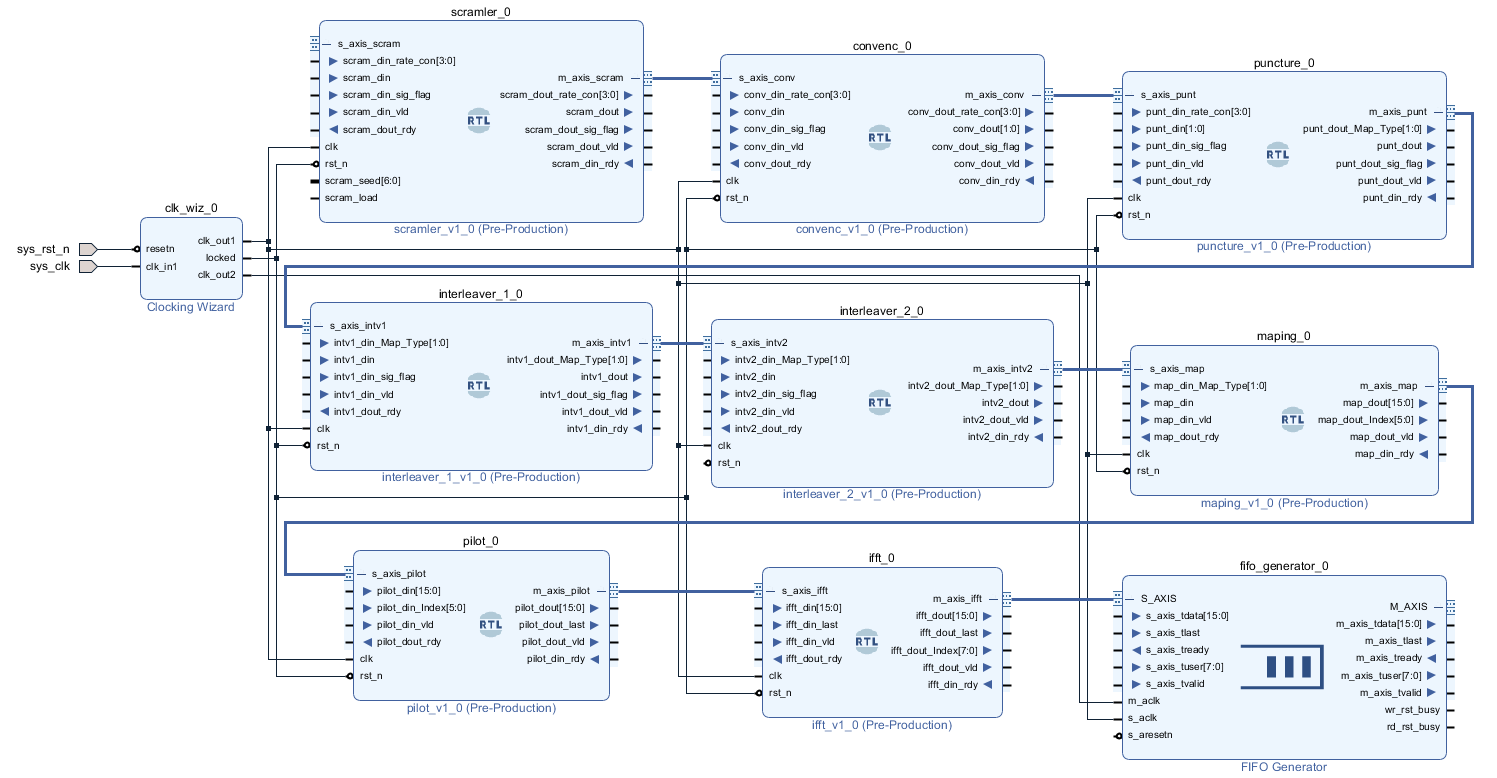

和之前的模块一起,按照如下连接,进行仿真,这里省略了并串转换。

仿真模块连接图

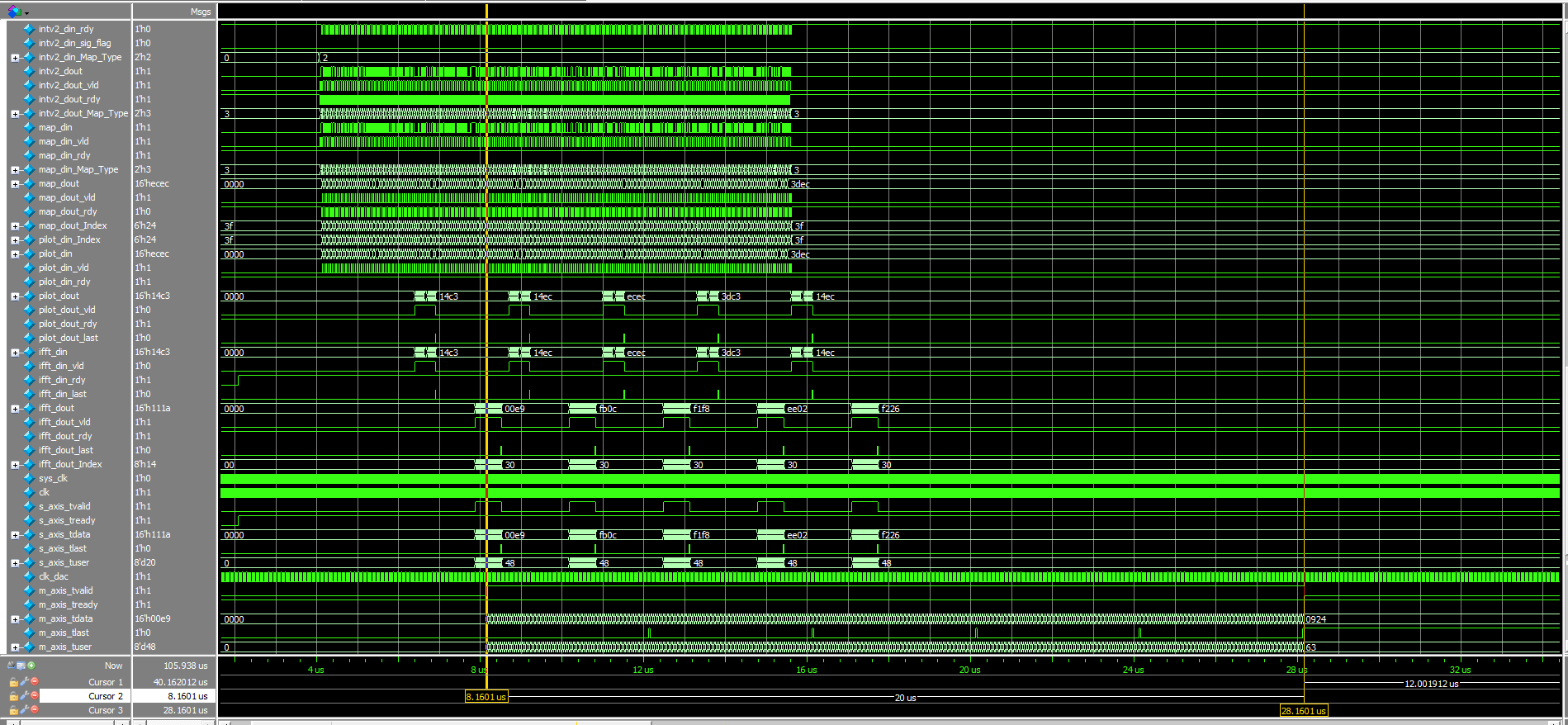

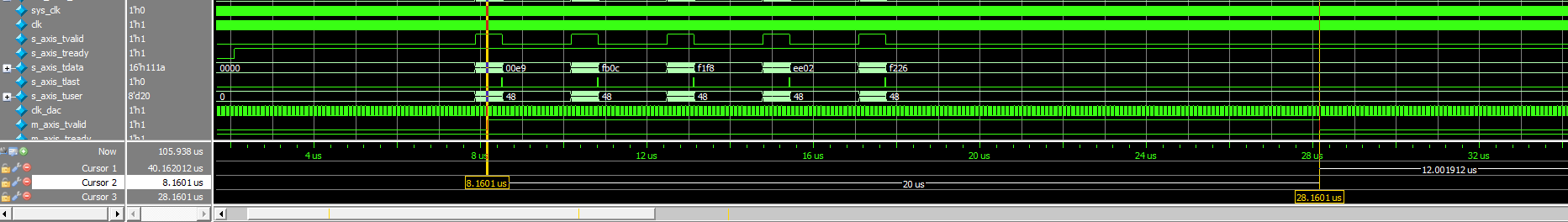

测试数据选择5个OFDM符号,使用16-QAM调制,编码效率为3/4,一共720个bit。仿真结果如下:

仿真全局截图

仿真局部截图

5个OFDM符号输出的时间刚好为20us,说明是连续输出的,即满足了协议中符号之间不留间隙。

6.总结

使用AXI-Stream协议处理数据流,下游模块数据没处理好会对上游进行反压,上游数据没处理完,不会往下游传输,可以很方便且高效的对数据进行流水线处理。个人认为相比于书籍《基于XILINX FPGA的OFDM通信系统基带设计》中方法要可靠得多。

![]()

书中的实现方法

网上大多数博客都是根据书中的这种,不断变换时钟进行跨时钟域处理来做这个项目,个人认为不是很可靠,所以从头开始采用了AXI-Stream协议处理数据流的方式来写。如果有什么不正确的地方,或者不理解的欢迎和我讨论。

原文链接(相关文章合集):OFDM 802.11a的xilinx FPGA实现

6155

6155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?