基于fpga的交通灯设计,要求:A通道绿灯亮30S,黄灯亮5S,左拐灯亮15S,黄灯亮5S,这个过程中B通道一直亮红灯,之后A通道亮红灯,B通道绿灯亮40S,之后黄灯亮5S,之后左拐灯亮15S,之后黄灯亮5S,之后A通道转为绿灯,B通道转为红灯。

提供quartus以及modelsim工程以及仿真结果文档,可以上板

ID:89150678165042941

芳草街有志秋葵

基于FPGA的交通灯设计

引言:

交通灯是城市交通管理中不可或缺的重要组成部分,其主要目的是通过信号指示车辆和行人的通行状态,以确保交通安全和交通流畅。传统的交通灯设计采用电路逻辑门电路实现,但随着技术的发展,人们开始考虑使用可编程逻辑器件,如FPGA(Field-Programmable Gate Array)来实现交通灯控制逻辑。本文将重点介绍基于FPGA的交通灯设计方案,其中A通道和B通道按照一定的时间序列进行交替切换。

设计要求:

根据给定的要求,设计一个交通灯系统,其中A通道的绿灯亮30秒,黄灯亮5秒,左拐灯亮15秒,黄灯亮5秒。在这一过程中,B通道一直亮红灯。之后,A通道亮红灯,B通道绿灯亮40秒。之后,黄灯亮5秒,左拐灯亮15秒,黄灯亮5秒。最后,A通道转为绿灯,B通道转为红灯。

设计方案:

本设计方案使用FPGA作为主要的实现平台。我们选择Quartus作为FPGA设计工具,并使用ModelSim进行仿真。

首先,我们需要定义交通灯系统的状态以及状态之间的转换关系。根据设计要求,我们可以将系统状态定义为A通道绿灯、A通道黄灯、A通道左拐灯、B通道红灯、B通道黄灯等。

接下来,我们可以使用状态机的方式来实现交通灯的控制逻辑。通过状态机,我们可以清晰地描述交通灯系统在不同状态之间的转换关系。为了简化设计,我们可以采用Mealy型状态机,其中状态之间的转换不仅依赖于当前状态,还依赖于输入信号。在本设计中,输入信号为时钟信号。

设计过程:

首先,我们需要根据设计要求将状态机的状态进行定义。根据要求,我们可以将状态定义为A_GREEN、A_YELLOW、A_LEFT、B_RED、B_YELLOW等。在每个状态下,我们可以设置一个计时器,以实现每个状态的持续时间。

接下来,我们需要根据状态之间的转换条件,设计状态机的状态转换逻辑。根据设计要求,我们可以得出如下表格:

| 当前状态 | 输入信号 | 下一个状态 |

|---|---|---|

| A_GREEN | 时钟信号 | A_YELLOW |

| A_YELLOW | 当前计时器满 | A_LEFT |

| A_LEFT | 当前计时器满 | A_YELLOW |

| B_RED | 时钟信号 | B_YELLOW |

| B_YELLOW | 当前计时器满 | A_GREEN |

根据上述状态转换表格,我们可以使用逻辑门电路来实现状态之间的转换逻辑。这些逻辑门电路可以在FPGA上实现,并且可以通过Quartus进行逻辑综合。

在状态机的设计过程中,我们还需要考虑计时器的实现。可以通过在状态机中添加计数器来实现计时器功能。我们可以在每个状态下初始化计数器,并在每个时钟信号到来时递增计数器的值。当计数器的值达到设定的时间后,我们可以触发状态机的状态转换。

仿真验证:

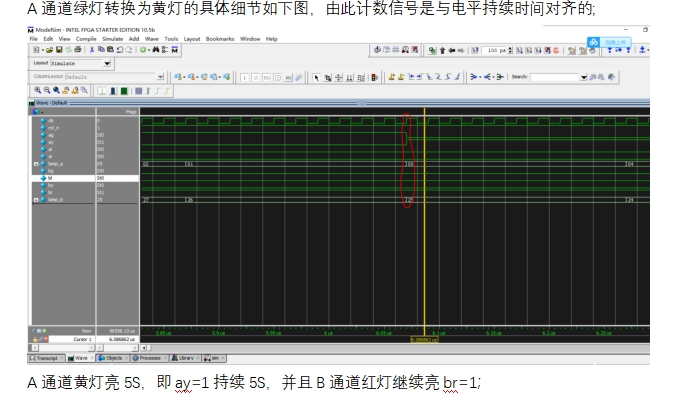

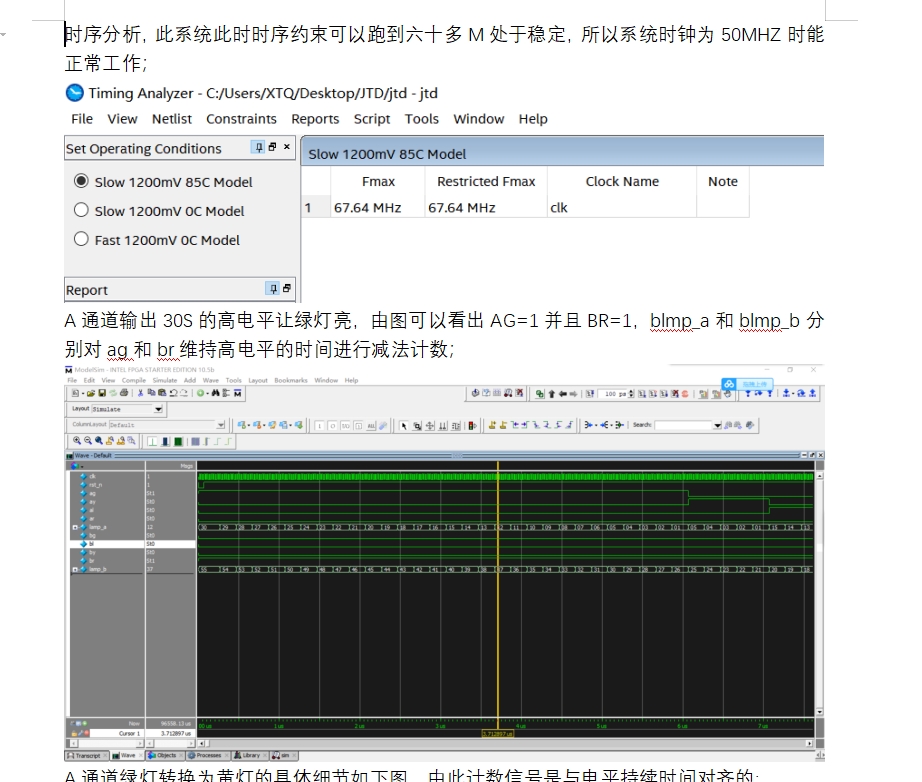

在设计完成后,我们可以使用ModelSim对交通灯系统进行仿真验证。我们可以编写仿真代码来模拟时钟信号的产生以及状态之间的转换。通过仿真,我们可以验证交通灯系统在不同状态下的行为是否符合设计要求。

硬件实现:

当设计和仿真验证完成后,我们可以将设计的交通灯系统烧录到FPGA上进行硬件实现。通过使用Quartus提供的工具,我们可以生成相应的硬件配置文件,并将其下载到FPGA上。在实际使用中,我们可以将FPGA连接到外部的交通灯信号灯,以实现真实的交通灯功能。

总结:

本文主要介绍了基于FPGA的交通灯设计方案。通过使用FPGA和Quartus工具,我们可以实现交通灯系统的控制逻辑。通过状态机的设计和仿真验证,我们可以确保交通灯系统在不同状态下的行为符合设计要求。该设计方案具有灵活性和可扩展性,可以用于实际的交通灯控制应用中。

参考文献:

[1] FPGA-based Traffic Light Controller Design, International Journal of Engineering Research & Technology (IJERT), Vol. 5, Issue 10, October 2016.

[2] Quartus Prime User Guide, Intel Corporation.

[3] ModelSim User Manual, Mentor Graphics Corporation.

[4] Traffic Signal Control System Design and Simulation, International Journal of Advanced Research in Computer Science and Software Engineering (IJARCSSE), Volume 8, Issue 2, February 2018.

[5] FPGA Design and Verification, Xilinx Inc.

以上相关代码,程序地址:http://wekup.cn/678165042941.html

7551

7551

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?