参考

数字IC前端设计流程及工具【RTL设计+功能仿真】【综合】【DFT】【形式验证】【STA静态时序分析】

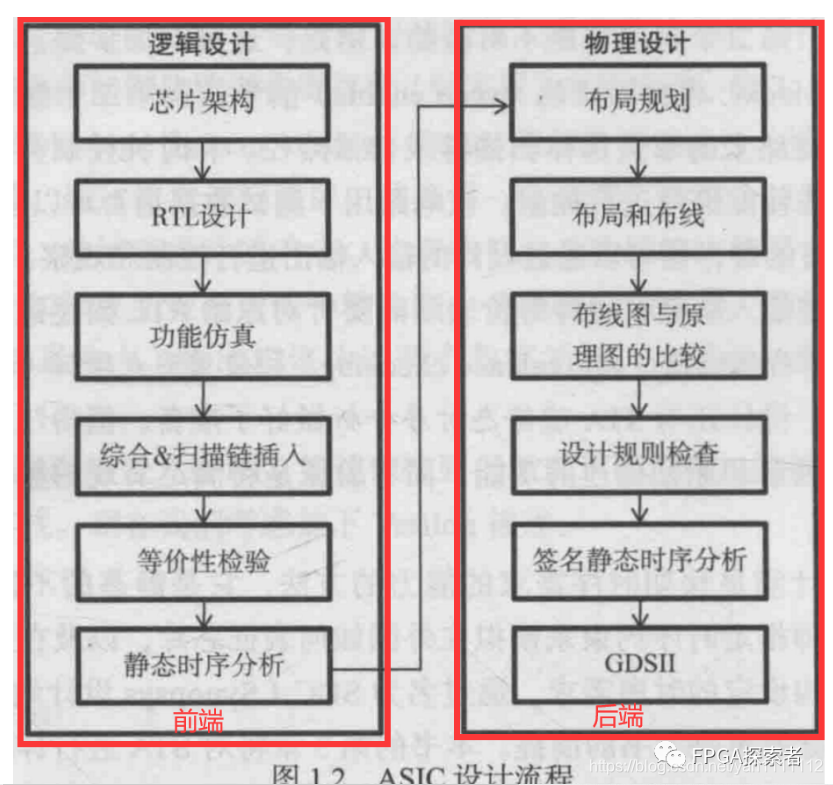

前端和后端的区分:

以门级网表(Netlist)生成为分界线,之前称为前端,之后称为后端。

布局布线之前可以认为是前端,布局布线到流片是后端。

Synthesis:综合,主要任务是将 RTL 代码 转成 门级网表;

典型的网表文件由单元(Cell)、引脚(Pin)、端口(Port)、网络(Net)组成。

功能仿真:

验证 RTL 代码设计的功能正确性,没有加入延时信息,又叫前仿真,工具有 Mentor 的 Modelsim,Synopsys 的 VCS,Candence 的 NC-Verilog。 在综合、布局布线以后,有加入延时的后仿真(时序仿真)。

Synthesis 综合

逻辑综合的结果(目的)是把 HDL 代码翻译成门级网表 netlist,工具有 Synopsys 的 Design Compiler(简称 DC),门级网表拿去布局布线。

本文介绍了数字IC前端设计流程,包括功能仿真、Synthesis综合、DFT可测性设计和STA静态时序分析。功能仿真用于验证RTL代码功能正确性;Synthesis将RTL代码转化为门级网表;DFT涉及Scan Chain、MBIST和Boundary Scan等测试技术;形式验证则通过等价性检验确保综合后网表与原始设计功能一致;STA用于检查电路时序违例。

本文介绍了数字IC前端设计流程,包括功能仿真、Synthesis综合、DFT可测性设计和STA静态时序分析。功能仿真用于验证RTL代码功能正确性;Synthesis将RTL代码转化为门级网表;DFT涉及Scan Chain、MBIST和Boundary Scan等测试技术;形式验证则通过等价性检验确保综合后网表与原始设计功能一致;STA用于检查电路时序违例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

879

879

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?