结论

先得出结论,一般情况下ADC、DAC等混合信号器件的AGND和DGND要连接在一起接入低阻抗模拟地。芯片的DGND表示此引脚连接芯片内部的数字地,并不意味着它必须要连接到系统的数字地。

原因

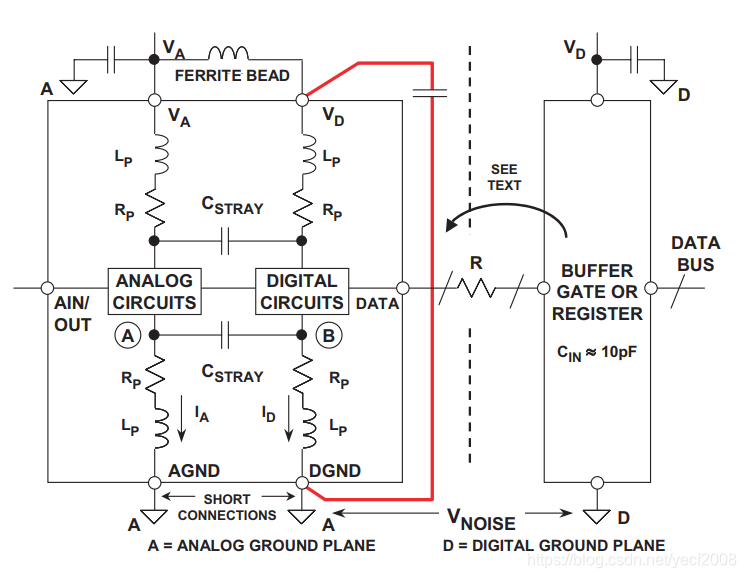

下图简单描述了混合信号芯片内部结构和部分外部连接

混合信号芯片内部一般会将数字电源和模拟电源分开,减小数字噪声耦合到模拟部分。但是内部的引线、封装引脚难免会有电感LP和电阻RP,它们之间又无法避免存在寄生电容CSTRAY,快速变化的数字电流会在B点产生电压,然后通过CSTRAY耦合至A点。

但是这不需要我们考虑,因为IC工程师在设计芯片的时候肯定考虑了它们的影响,保证芯片能够正常工作并且性能符合数据手册的指标(插一句话,经验告诉我当电路指标没有达到我们设计预期的时候,不要去怀疑芯片的数值虚表,一般都是我们电路布局问题或者一些设计问题)。而我们的工作是设计能让这个芯片发挥它性能的环境。

假设我们将芯片的AGND连接至我们系统的模拟地,DGND连接至系统的数字地,由于数字地存在比较丰富的噪声VNOISE,那么这个VNOISE就会在B点出现,并且经过寄生电容CSTRAY耦合至A点,从而影响模拟部分。

正确且简单的做法是如图中的连接方式,将AGND和DGND都连接至模拟地,并且保证它们之间的低阻抗,这样可以减少AGND和DGND的噪声通过寄生电容CSTRAY耦合,外部电路建议芯片的供电引脚VA和VD之间添加磁珠,靠近电源引脚放置去耦电容,根据实际分析有必要的话与缓冲器之间增加电阻可以减少数字电路产生的瞬间电流从而减小B点产生的电压等。

更好的连接方式

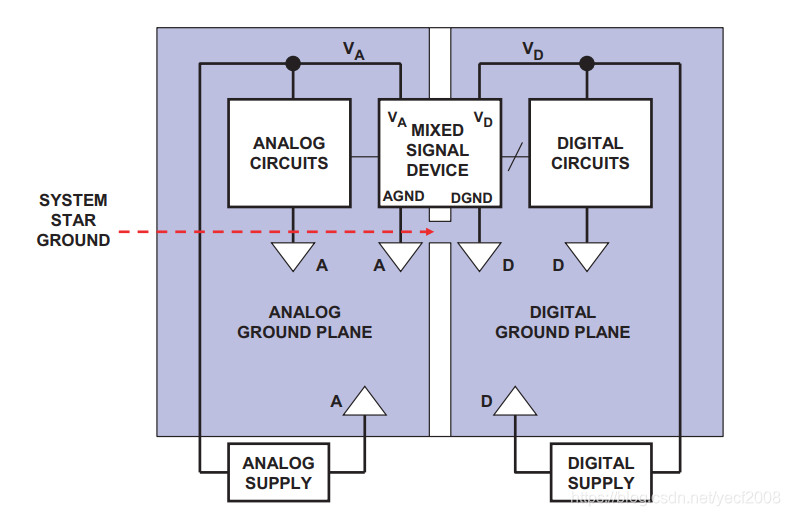

当然存在更好的布局方式,如下图

如图中将数字部分和模拟部分分开,并在混合信号的附近单点连接,这样可以更好的减少数字部分和模拟部分的耦合。

但是在实际设计电路中这种方法往往是难以实现的,因为实际项目往往需要多个混合信号芯片,如ADC、DAC、DDS等,多个混合信号芯片只有单点连接的话可能会造成更差的表现。所以对于一般设计或者经验较少的设计师,我建议不要区分模拟地和数字地,而是将模拟芯片和数字芯片分区域排列,模拟电源和数字电源放在相应的区域或者靠近的位置,不要交叉排布,保证有一层或两层完整的地层,这样的设计往往layout更简单并且不易出问题。不要把数字噪声当成洪水猛兽,电路设计往往是平衡的艺术。

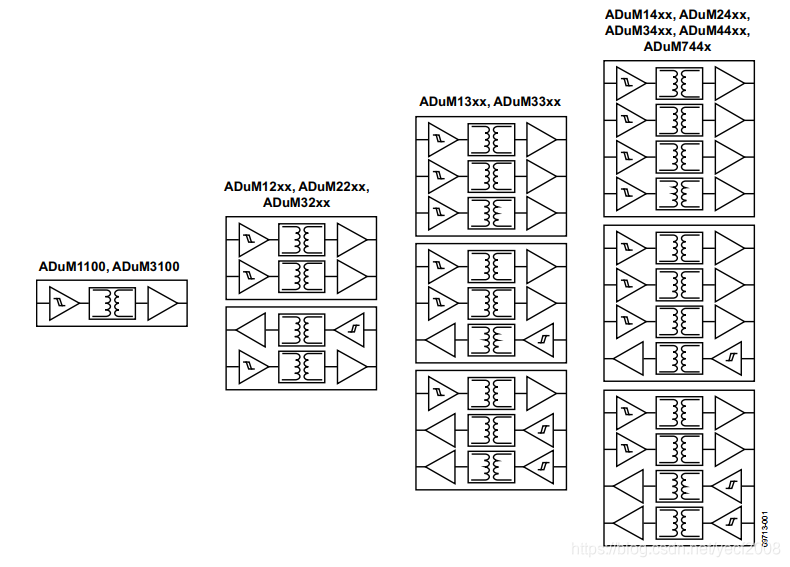

对于数字电路存在较大噪声的情况,如复杂的工业环境,建议将数字电路和模拟电路完全隔离,混合信号芯片一般归为模拟电路部分,模拟电路和数字电路的通信使用数字隔离器件,如ADI的iCoupler器件

这类器件的发射和接收是隔离的,类似光耦,只不过光耦是通过光耦合,它是通过变压器耦合,但是这类器件相对光耦有更小的体积、更高的速率、更好的时序等优势。

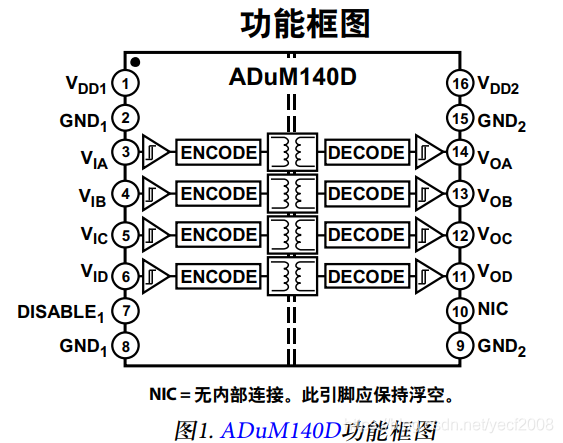

上图是ADuM140D的内部结构,如果我们系统是一个ADC的采集系统,就可以将VDD1和GND1连接至隔离的模拟部分,VDD2和GND2连接至数字部分,VI引脚连接ADC的数字输出,VO引脚连接至数字部分的接收,如MCU的IO口。保证数字部分和模拟部分是完全没有电气连接的,这样可以大幅度减小数字部分的恶劣噪声对模拟采集的影响。

当然使用这种器件的缺点在于会占用更多的PCB空间、更高的BOM成本,I2C、SPI之类的串行总线接口的芯片还好,如果是并行接口的ADC或DAC将会需要很多片数字隔离芯片。

所以具体情况需要具体分析,一般不存在完美的方案,电路设计往往是根据需求取折中而已。

参考文献:ADI MT-031 指南 作者 : Walt Kester、 James Bryant、 Mike Byrne

3491

3491

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?