FPGA调试过程中,不可避免的是需要进行程序调试,有的时候不调试,很难把代码中的问题找出来。signalTap作为quartus自带的调试工具,对FPGA的代码调试能起到很大的作用。那么此工具如何使用,对于很多初学者来讲,可能会呈现出一头雾水的感觉。此文便粗略的讲述了其使用方法。

一、首先你得有个相对完善的工程

这一步是写FPGA的最基本的,在此不做阐述,或许你认为是废话,但我觉得还是有必要提醒一下。

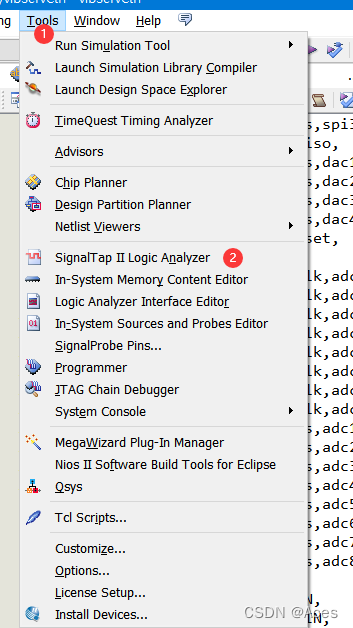

二、打开signalTap的方式

在“Tools”菜单下找到“SignalTap II logic Analyzer”,点击打开。

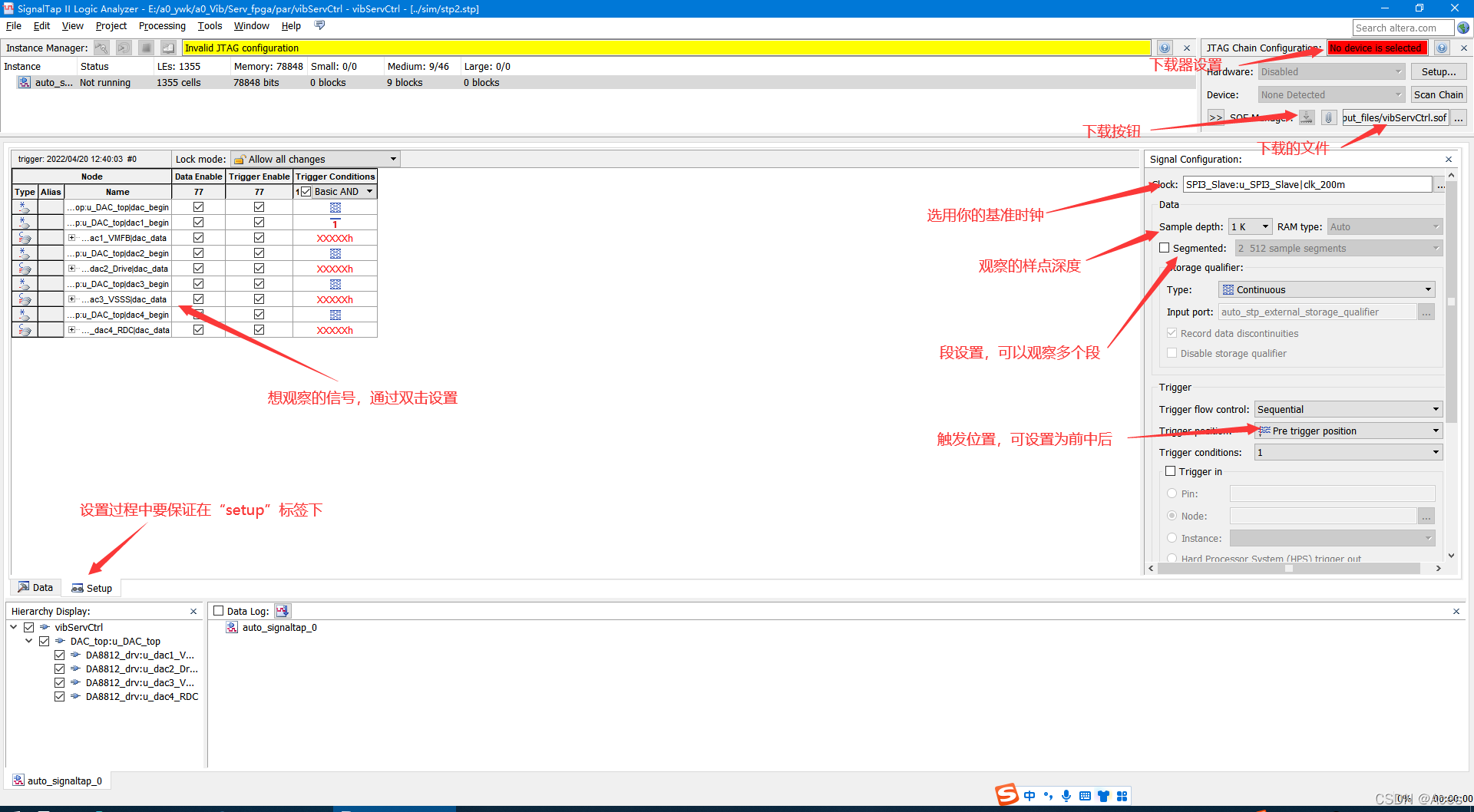

打开后界面如下所示

在上图,已经在相关地方做了标记,在signalTap的页面下,也可以将程序下载到你的硬件中,图右上角区域便是下载相关的设置,根据你的需要选择设置。

三、相关设置

![]()

时钟设置,对于你想观察的信号,你要提供一个时钟信号,此时钟是用于采样你信号的,一般情况下,可选择你时序模块中的clk信号。

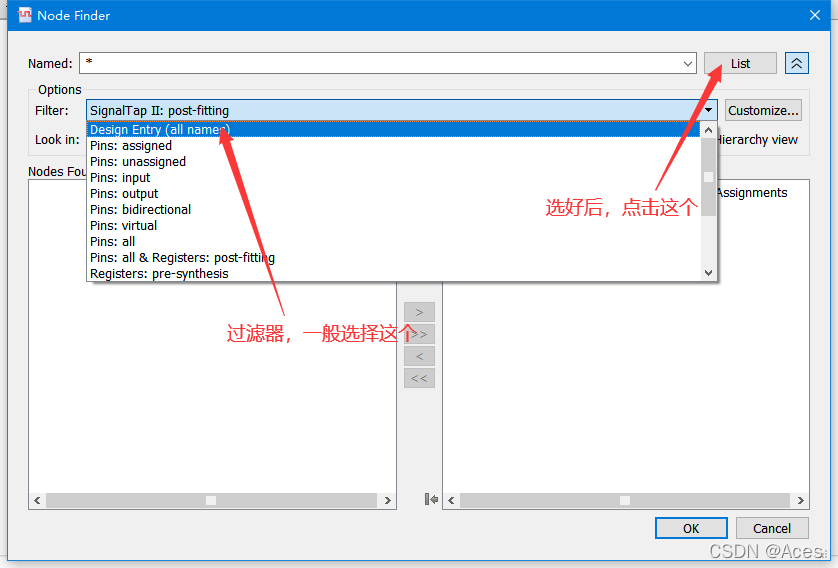

时钟设置界面,按上图指示选择操作,点击“list”后,在左边会列出过滤的信号,根据实际选择你的时钟。

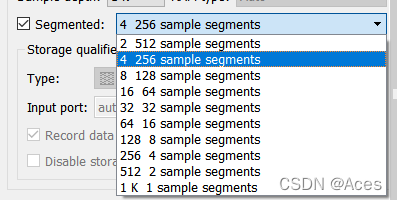

采样深度也有多种值可选,选得越大,暂用FPGA资源就会越多,根据实际需要选择合适的深度。段设置同理。

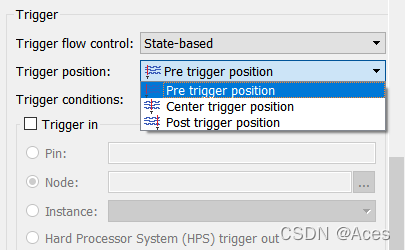

触发设置,根据需要选择触发点在采样数据区域的位置,有前中后三种位置可选。另触发条件也可以设置多个。

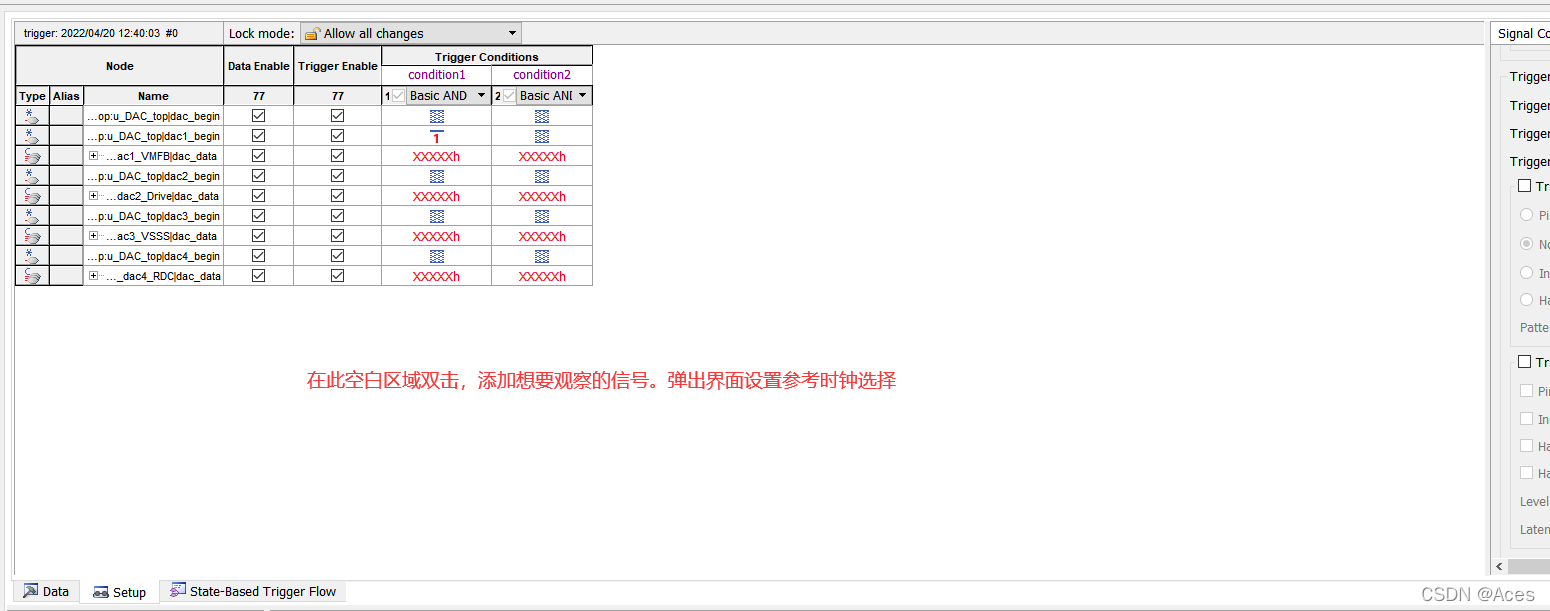

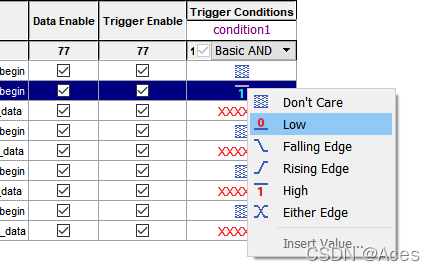

观察的信号选择,触发条件设置,一般情况下选择一个触发条件即可,如果选择多个,有可能触发不了观测,如有需要时例外。

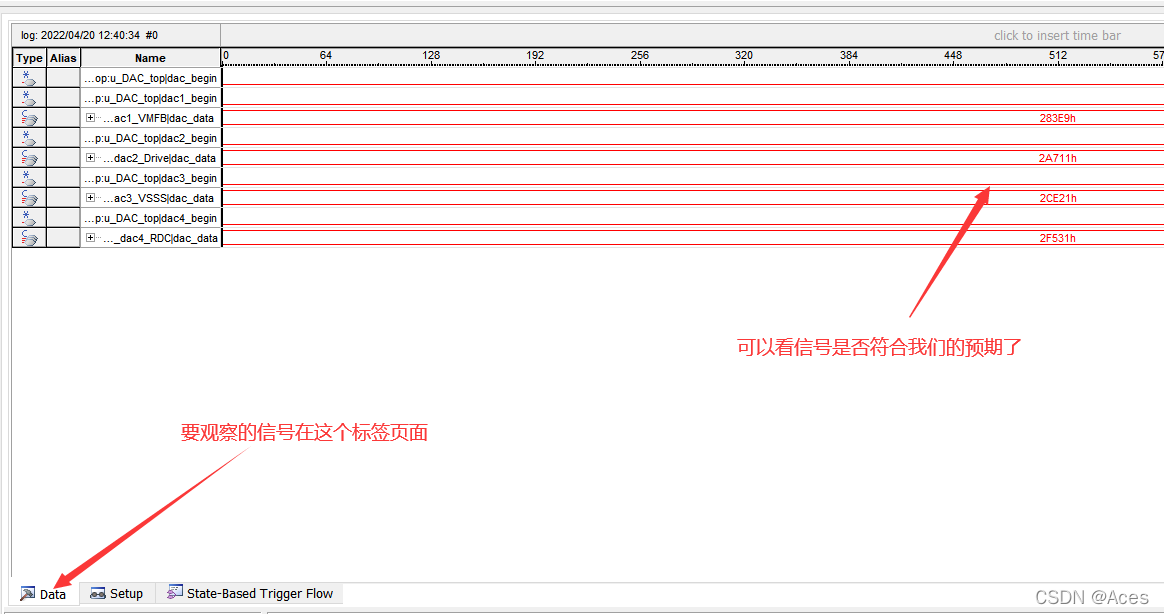

四、开始分析

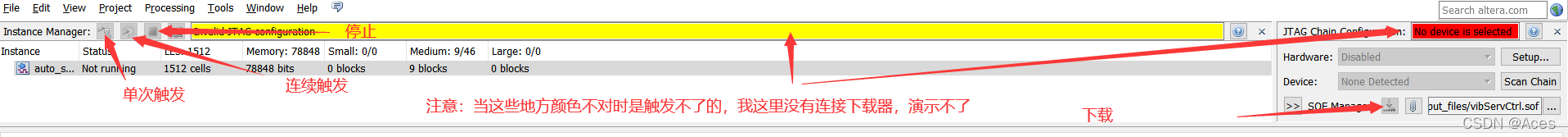

再所有的参数都设置好后,接下来就可以进入运行分析环节。在运行之前要回到代码编辑窗口,保存signalTap文件,并进行综合编译,完成后再回到signalTap窗口。

“下载”->“触发”

以上便是使用signalTap的基本方法了,在你用熟悉了之后,或许会发现更多强大的功能,自己再慢慢探索吧。写FPGA或许可以不要仿真(有时仿真结果对,但执行结果不一定,或者执行不稳定,一会对,一会不对),但是逻辑分析一定是需要的,如果没有,仅仅凭借总体运行结果观察调试,很费脑,还不一定有效果,既然有此现成工具,我们就要好好利用起来。

1022

1022

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?