参考:

1.正点原子

2.https://openatomworkshop.csdn.net/6673ddaba1e8811a9781de12.html

3.https://devpress.csdn.net/hefei/6462fb143399b617f0c02487.html (暂时未看)

1.ADC简述

ADC 即模拟数字转换器,英文详称 Analog-to-digital converter,可以将外部的模拟信号转换为数字信号。

STM32F4xx 系列芯片拥有 3 个 ADC,这些 ADC 可以独立使用,其中 ADC1 和 ADC2 还可以组成双重模式(同步或者协同采样)。STM32 的 ADC 是 12 位逐次逼近型的模拟数字转换器。它有 19 个通道,可测量 16 个外部和 2 个内部信号源和 Vbat 通道的信号, ADC 中的各个通道的A/D 转换可以单次、连续、扫描或间断模式执行。ADC 的结果可以以左对齐或者右对齐存储在16 位数据寄存器中。ADC 具有模拟看门狗的特性,允许应用检测输入电压是否超过了用户自定义的阈值上限或下限。

STM32F407 的 ADC 主要特性可以总结为以下几条:

1、可配置 12 位、10 位、8 位或 6 位分辨率;

2、转换结束、注入转换结束和发生模拟看门狗事件时产生中断

3、单次和连续转换模式

4、自校准

5、带内嵌数据一致性的数据对齐

6、采样间隔可以按通道分别编程

7、规则转换和注入转换均有外部触发选项

8、间断模式

9、双重模式(带 2 个或以上 ADC 的器件)

10、ADC 转换时间:最大转换速率为 2.4MHz,转换时间为 0.41us

11、ADC 供电要求:2.4V 到 3.6V

12、ADC 输入范围:VREF–≤VIN≤VREF+

13、规则通道转换期间有 DMA 请求产生

2.ADC原理

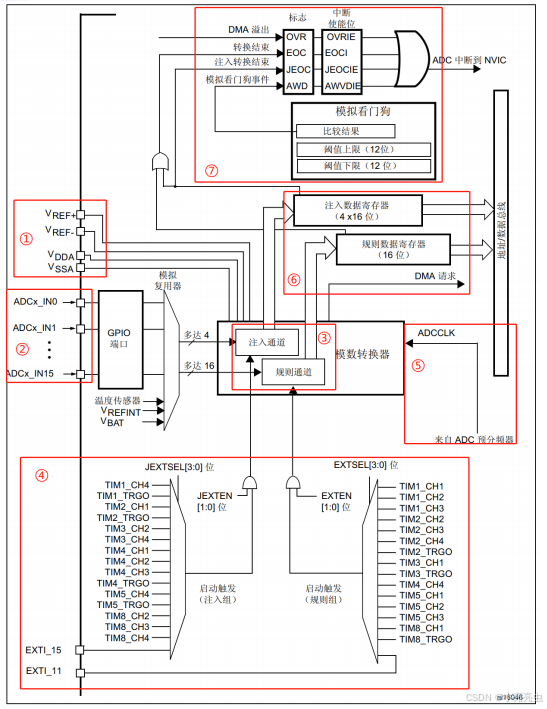

下面来介绍 ADC 的框图:

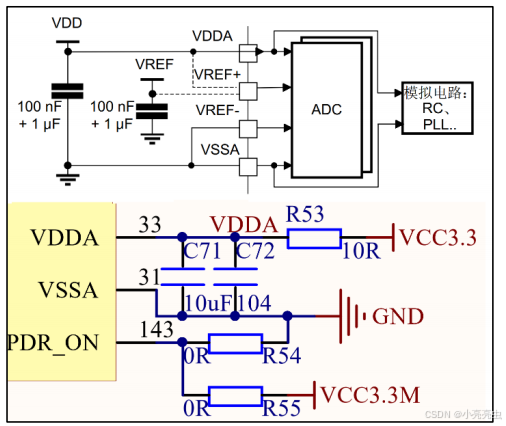

① 输入电压

在前面 ADC 的主要特性也对输入电压有所提及,ADC 输入范围 VREF–≤VIN≤VREF+,最终还是由 VREF–、VREF+、VDDA和 VSSA决定的。这几个参数的关系,如图所示:

从上图可以知道,VDDA 和 VREF+接 VCC3.3,而 VSSA和 VREF-是接地,所以 ADC 的输入范围即 0~3.3V。R55 默认焊接,R54 默认不焊接。

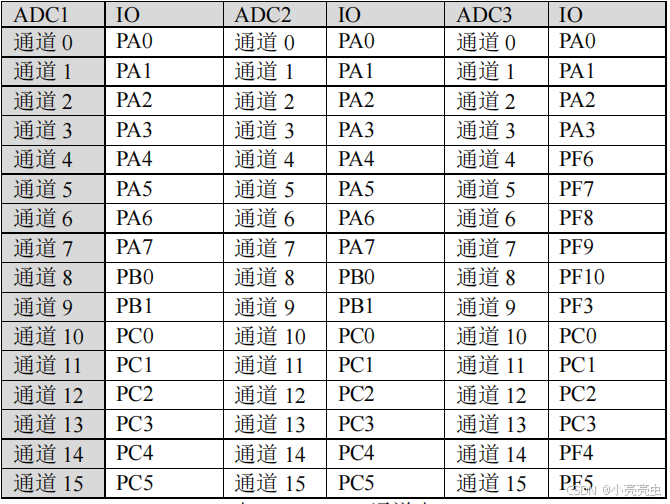

② 输入通道

在确定好了 ADC 输入电压后,如何把外部输入的电压输送到 ADC 转换器中呢,在这里引入了 ADC 的输入通道,在前面也提及到了 ADC1 有 16 个外部通道和 3 个内部通道,而 ADC2和 ADC3 只有 16 个外部通道。ADC1 的外部通道是通道 17、通道 18 和通道 19,分别连接到内部温度传感器、内部Vrefint和Vbat。外部通道对应的是图中的ADCx_IN0、ADCx_IN1…ADCx_IN15(下图没有描述内部通道)。 ADC 通道表见表所示:

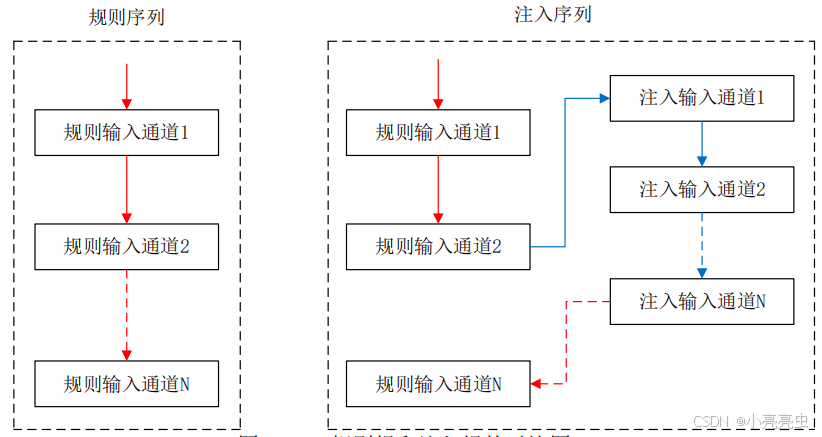

③ 转换顺序

当任意 ADCx 多个通道以任意顺序进行一系列转换就诞生了成组转换(也就是多个通道的序列),这里就有两种成组转换类型:规则组和注入组。规则组就是图上的规则通道,注入组也就是图上的注入通道。为了避免大家对输入通道加上规则通道和注入通道理解有所模糊,后面规则通道以规则组来代称,注入通道以注入组来代称。规则组允许最多 16 个输入通道进行转换,而注入组允许最多 4 个输入通道进行转换。这里讲解一下规则组和注入组。

规则组(规则通道)

规则组,按字面理解,“规则”就是按照一定的顺序,相当于正常运行的程序,平常用到最多也是规则组。

注入组(注入通道)

注入组,按字面理解,“注入”就是打破原来的状态,相当于中断。当程序执行的时候,中断是可以打断程序的执行。同这个类似,注入组转换可以打断规则组的转换。假如在规则组转换过程中,注入组启动,那么注入组被转换完成之后,规则组才得以继续转换。

便于理解,下面看一下规则组和注入组的对比图,如图所示:

在了解了规则组和注入组后,现在了解一下它们两者的转换顺序。

规则序列

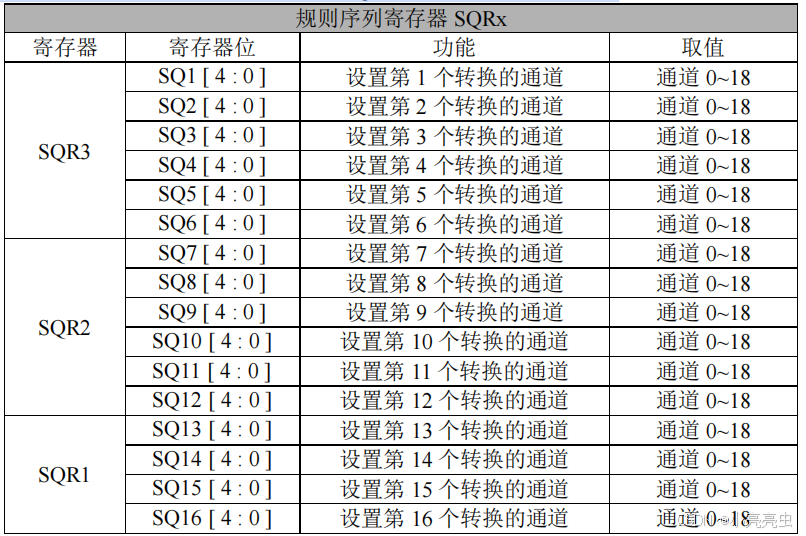

规则组是允许 16 个通道进行转换的,那么就需要安排通道转换的次序即 规则序列。规则序列寄存器有 3 个,分别为 SQR1、SQR2 和 SQR3。SQR3 控制规则序列中的第 1 个到第 6 个转换的通道;SQR2 控制规则序列中第 7 个到第 12 个转换的通道;SQR1 控制规则序列中第 13 个到第 16 个转换的通道。规则序列寄存器 SQRx 详表如表所示:

从上表可以知道,当我们想把 ADC 的输入通道 1 安排到第 1 个转换,那么只需要在 SQR3寄存器中的 SQ1[4:0]位写入该 ADC 输入通道 即写 1 处理即可。SQR1 的 SQL[3:0]决定了具体使用多少个通道。

注入序列

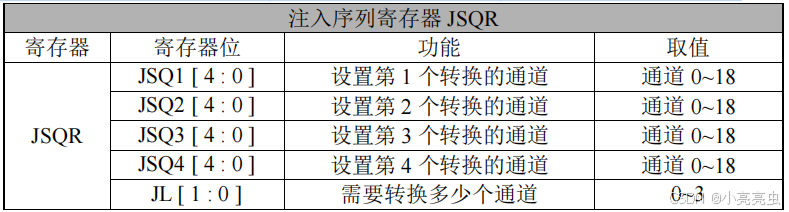

注入序列,跟规则序列差不多,都是有顺序的安排。由于注入组最大允许 4 个通道输入,所以这里就使用了一个寄存器 JSQR。注入序列寄存器 JSQR 详表如表所示:

④ 触发源

在配置好输入通道以及转换顺序后,就可以进行触发转换了。ADC 的触发转换有两种方法:

分别是通过软件或外部事件(也就是硬件)触发转换。我们先来看看通过写软件触发转换的方法。方法是:通过写 ADC_CR2 寄存器的 ADON 这个位来控制,写 1 就开始转换,写 0 就停止转换,这个控制 ADC 转换的方式非常简单。另一种就是通过外部事件触发转换的方法,有定时器和输入引脚触发等等。这里区分规则组和注入组。方法是:通过 ADC_CR2 寄存器的 EXTSET[2:0]选择规则组的触发源,JEXTSET[2:0]选择注入组的触发源。通过 ADC_CR2 的 EXTTRIG 和 JEXTTRIG 这两位去激活触发源。ADC3的触发源和 ADC1/2 不同,这里需要注意,那么在框图里已经标记出来了。

⑤ 转换时间

STM32F407 的 ADC 总转换时间的计算公式如下:

TCONV = 采样时间 + 12 个周期

采样时间可通过 ADC_SMPR1 和 ADC_SMPR2 寄存器中的 SMP[2:0]位编程,ADC_SMPR2

控制的是通道 0~9,ADC_SMPR1 控制的是通道 10~18。所有通道都可以通过编程来控制使用不同的采样时间,可选采样时间值如下:

⚫ SMP = 000:3 个 ADC 时钟周期

⚫ SMP = 001:15 个 ADC 时钟周期

⚫ SMP = 010:28 个 ADC 时钟周期

⚫ SMP = 011:56 个 ADC 时钟周期

⚫ SMP = 100:84 个 ADC 时钟周期

⚫ SMP = 101:112 个 ADC 时钟周期

⚫ SMP = 110:144 个 ADC 时钟周期

⚫ SMP = 111:480 个 ADC 时钟周期

12 个周期是 ADC 输入时钟 ADC_CLK 决定的。ADC_CLK 是由 APB2 经过分频产生,分频系数是由 RCC_CFGR 寄存器中的 PPRE2[2:0]进行设置,有 2/4/6/8/16 分频选项。

采样时间最小是 3 个时钟周期,这个采样时间下,我们可以得到最快的采样速度。举个例子,我们采用最高的采样速率,使用采样时间为 3 个 ADC 时钟周期,那么得到:

TCONV = 3 个 ADC 时钟周期 + 12 个 ADC 时钟周期 = 15 个 ADC 时钟周期, 一般 APB2 的时钟是 84MHz,经过 ADC 分频器的 4 分频后,ADC 时钟频率就为 21MHz。

通过换算可得到:

TCONV = 15 个 ADC 时钟周期 = (1/21 000 000) ∗ 15 s = 0.71us

⑥ 数据寄存器

ADC 转换完成后的数据输出寄存器。根据转换组的不同,规则组的完成转换的数据输出到ADC_DR 寄存器,注入组的完成转换的数据输出到 ADC_JDRx 寄存器。假如是使用双重模式,规则组的数据也是存放在 ADC_DR 寄存器。这两个寄存器的讲解将会在后面讲解,这里就不列出来了。

⑦ 中断

规则和注入组转换结束时能产生中断,当模拟看门狗状态位被设置时也能产生中断。它们在 ADC_SR 中都有独立的中断使能位,后面讲解 ADC_SR 寄存器时再进行展开。这里讲解一下,模拟看门狗中断以及 DMA 请求。

模拟看门狗中断

模拟看门狗中断发生条件:首先通过ADC_LTR和ADC_HTR寄存器设置低阈值和高阈值,然后开启了模拟看门狗中断后,当被 ADC 转换的模拟电压低于低阈值或者高于高阈值时,就会产生中断。例如我们设置高阈值是 3.0V,那么模拟电压超过 3.0V 的时候,就会产生模拟看门狗中断,低阈值的情况类似。

DMA 请求

规则组和注入组的转换结束后,除了产生中断外,还可以产生 DMA 请求,把转换好的数据存储在内存里面,防止读取不及时数据被覆盖。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1188

1188

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?