〇、前言

亚稳态是一个数字设计工程师耳熟能详的词汇,但是对于亚稳态发生的机制、处于亚稳态的寄存器的输出特征、为什么打两拍可以避免亚稳态、针对特定信号是否可以不同步直接使用、什么时候需要使用多级寄存器进行同步等等问题,很多工程师心中并没有明确的答案。

在收集比较若干互联网资料的基础上,本文试图回答上述问题,希望可以帮助各位工程师加深对亚稳态现象的理解。

一、亚稳态的发生机制

1.1 寄存器的基本原理

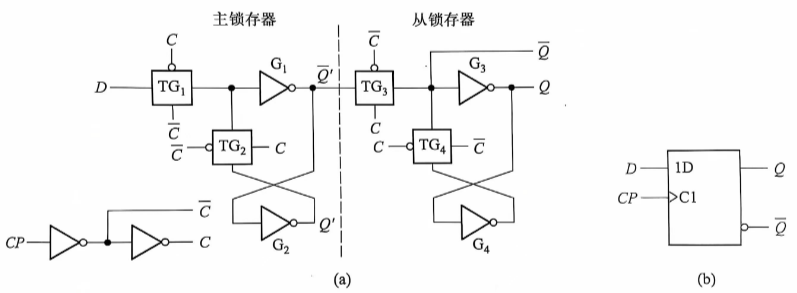

以最常使用的D触发器为例进行解释(通常认为寄存器指由多个触发器组成的储存多位信息的电路,在本文分析的范围内,没有必要区分二者,后文存在混用的情况)。D触发器由两个D锁存器通过级联的方式组成,如下图所示,左边的锁存器称为主锁存器,而右边的锁存器称为从锁存器,两个锁存器之间利用传输门隔开,实现存储和输出的隔离。

当输入时钟CP=0,那么C=0,C非=1,导致传输门TG1、TG4开启,TG2、TG3关闭。此时从锁存器是一个基本双稳态电路,负责储存信息并输出。

当时钟信号CP由0切换为1后,C=1,C非=0,导致传输门TG2、TG3开启、TG1、TG4关闭,此时切断了D端的输入,并且主锁存器变成了基本的双稳态电路,跳变前的信号被锁存到里面,此时主锁存器负责储存信息,从锁存器只有输出的作用。

当时钟信号CP再次由1切换为0后,从锁存器会进入双稳态电路,将主锁存器之前锁好的信号锁存起来,维持输出的稳定,而主锁存器会退出双稳态电路,随着D端输入不断更新电路状态,为下一次锁存做准备。

主、从锁存器接力工作,最后实现我们熟知的D触发器的功能。

1.2 亚稳态发生机制1:输入改变在时钟沿附近

在时钟CP为低时,D端的输入信号发生了电平转换,那么上图中反相器G1的输入与输出都随之发生电平转换,假设G1输出正在转换的过程中时钟CP上升沿到达,那么TG2将打开,G1与G2形成的双稳态电路需要较长时间才能达到稳定状态(由反相器输出特性、双稳态电路特性决定),且最终处于哪一种稳定状态并不确定(应该主要由TG2打开时G1输出端电平高低决定)。对于整个触发器来说,我们认为它进入了亚稳态。

1.3 亚稳态发生机制2:输入为中间电平

试想,如果在采样的时钟沿到达时,D端输入既非低电平,也非高电平,而是一个中间电平,那么在采样的时钟沿到达之后,G1与G2形成的双稳态电路同样需要较长时间才能达到稳定状态,触发器也进入了亚稳态。这种情况发生在前级寄存器发生亚稳态后向后级寄存器的传播。(本段是作者的推断,并没有在参考资料中看到)

1.4 亚稳态发生的其他机制

在一些文献中还提到,时钟毛刺、异步复位信号到达时刻与采样时钟沿达到时刻过于接近等也都可能会导致触发器进入亚稳态。在电路设计中对时钟和复位信号也应特别小心。

从电路的角度粗略来讲,触发器的正确工作依赖于主从锁存器配合依次进入双稳态,实际上信号的传输、双稳态的建立都需要时间,如果在信号传输还未完成、双稳态还未建立就切换电路状态,那么电路将不能正常工作。

二、处于亚稳态的寄存器的输出特征

2.1 输出信号的波形特征

很多资料在描述寄存器发生亚稳态后输出特征时使用的都是模糊的、描述性的语言,使人很难对亚稳态的寄存器输出特征产生直观印象。

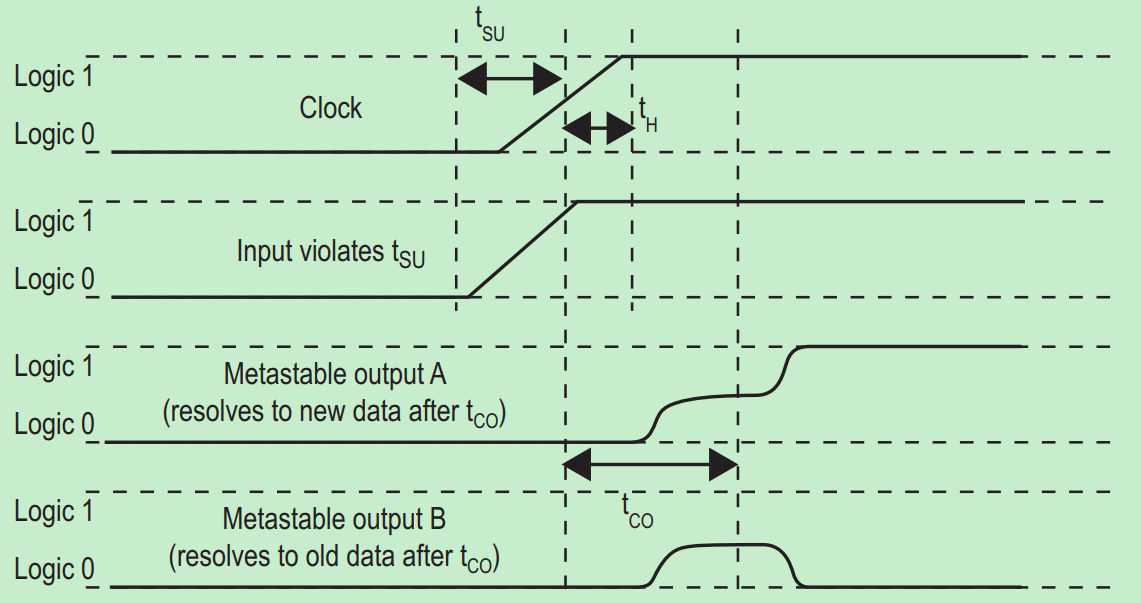

但是仍有一些资料给出了示意的波形,如下图所示。输出会长时间的在中间电平停留(而不是如某些资料中描述的在高低电平之间不断振荡),最后退出到高电平或者低电平。

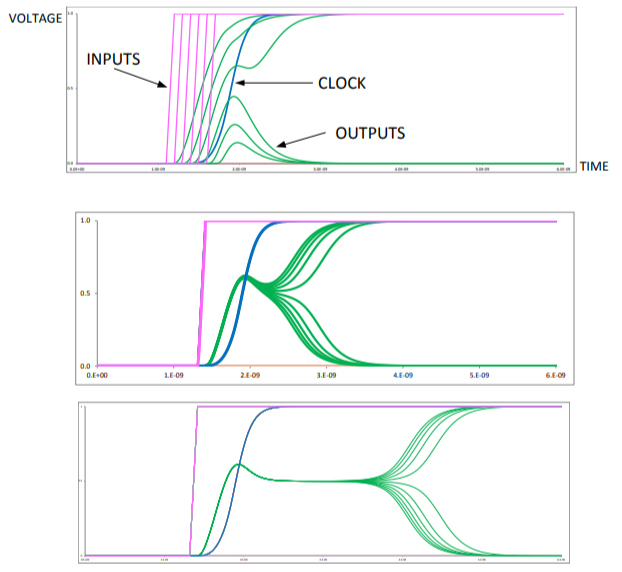

另外一些资料在给寄存器建立数学描述模型的基础上,仿真计算出了亚稳态下寄存器的输出,如下图所示。仿真波形与上面给出的示意图比较一致,即输出可能长时间停留在中间电平,最后在某些微小差异的累加作用下返回高电平或者低电平。

( Empirical circuit simulations of entering metastability in the master latch. Charts show multiple inputs D, internal clock (CLK2) and multiple corresponding outputs Q (voltage vs. time). The input edge is moved in steps of 100 ps, 1 ps, and 0.1 fs in the top, middle, and bottom charts respectively. )

2.2 从亚稳态退出的时间

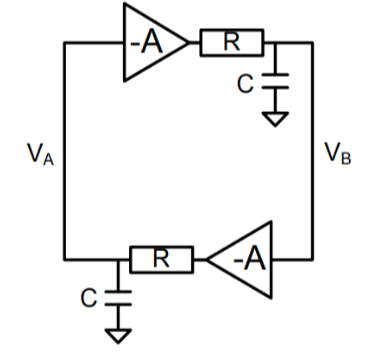

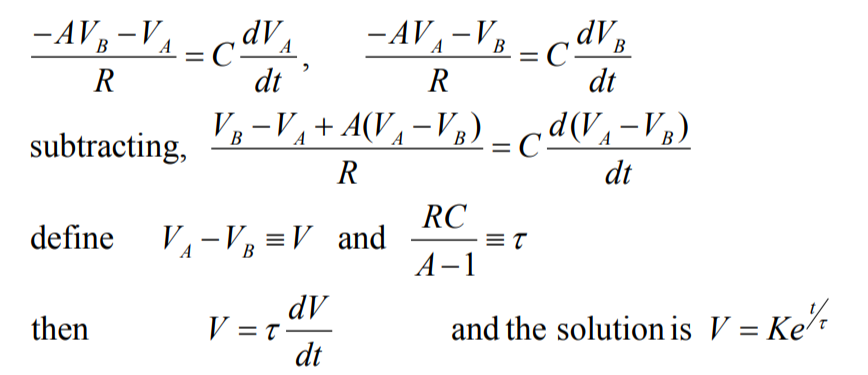

在亚稳态中,两个反相器处于其线性传递函数区域,可以通过小信号模型将其视为放大器。

通过对该简化电路模型的数学描述进行求解,可以得到

由计算结果可知,A、B两点的电压差呈指数增长。K为初始时刻的电压差,时间常数tao与电路参数有关(反相器输出端的电容负载与自身增益)。当V=Vdd时,该电路会退出亚稳态。

由上述结果也可以得到,对于初始电压差K和供电电压Vdd,上述电路到达稳态所需的时间 t=tao*ln(Vdd/K)。这个时间主要是由初始电压差K决定的,当K=0时,理论上需要无限长的时间才能达到稳态,但是在实际中这并不可能出现。

三、平均故障间隔时间(MTBF)

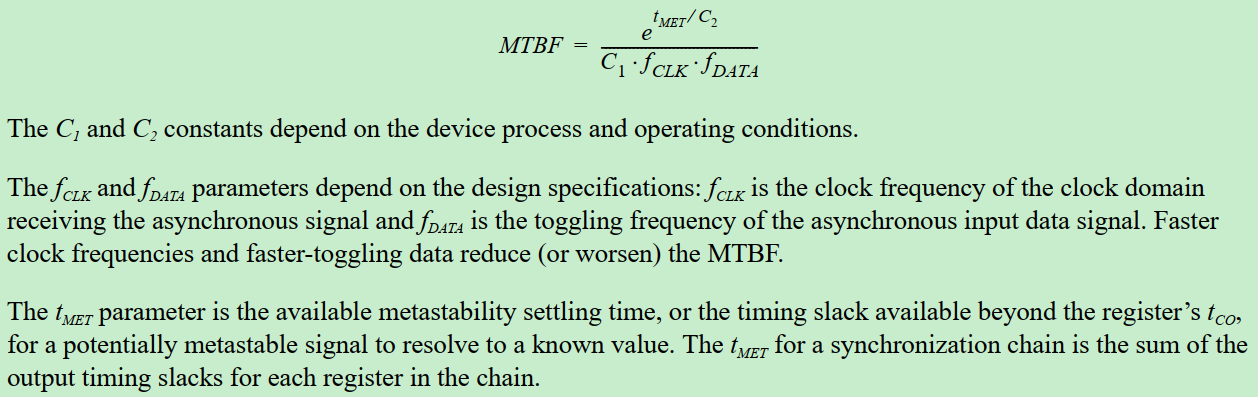

进入亚稳态时主锁存器中两个反相器的初始电压差是随机的,我们无法知道某一次亚稳态会持续多久。但是我们可以通过统计方法,得出在t_MET时间内亚稳态仍未退出的概率(此时亚稳态将传递至后级寄存器,可能引发故障),即MTBF:

式中C1、C2是与工艺、供电电压、温度等相关的参数,f_CLK与f_DATA分别是采样时钟和数据变化的频率,t_MET是采样时钟沿后允许亚稳态存在的时间。

在工艺、电压、采样时钟和数据变化频率无法改变时,设计者可以使用由多级寄存器构成的同步器增大t_MET,从而降低亚稳态导致故障的概率。

四、同步器级数的选择

4.1 两级同步器如何起到保护作用?

由MTBF公式可知(MTBF的倒数即为失效率,其与时间t为负指数关系),亚稳态出现后维持到时间t的概率是随着时间t的增大而呈现指数级下降的。

当系统时钟频率不是特别高时,时钟周期T远大于MTBF公式中的C2,则绝大部分出现的亚稳态都会在一个时钟周期内恢复,并不会传递至第二级寄存器,这些情况下使用第二级寄存器的输出是安全的;在少数情况下亚稳态传递至第二级寄存器,但是第二级寄存器产生的亚稳态较快的恢复,即使考虑了第二级寄存器后组合逻辑的延时也不会传递至后面的寄存器,在这种情况下也不会引起故障;仅当第二级寄存器产生的亚稳态没有及时恢复,传递至后面的寄存器时,则可能引发严重故障。

也可以从MTBF公式的角度理解,增加一级寄存器使t_MET增大了一个时钟周期,由于通常C2很小(有些基于FPGA的测量结果是20ps至50ps),MTBF将增大非常多,亚稳态导致的故障率将降低至完全可以接受的水平。

4.2 一级同步器是不是完全不可用?

作者有时候不禁在想,系统时钟频率差异很大,有的系统使用2M,有的使用20M,有的使用200M,为什么都必须使用两级同步器呢?当系统频率足够低时,是不是使用一级同步器(使用一级寄存器对异步信号采样后直接使用)也是安全的?

作者认为从理论上分析是可以使用一级同步器的,当系统时钟较慢,采样寄存器的输出到下一级寄存器之间的组合逻辑延时又不高,剩余的t_MET可能已经足够大,该部分电路的MTBF已经足够长,此时没有必要再增加一级寄存器。

但是在实际中,fab厂并不会提供特定工艺的下的C1,C2系数,路径上的时序裕量也不易提前知晓,再考虑大部分系统的时钟频率其实都不会特别低,需要同步的异步信号也不是特别多,默认统一采用多级同步器也是可以理解的。

4.3 什么时候用3级及以上的同步器?

当系统时钟频率很高,使用两级同步器已经不能提供足够长的t_MET和MTBF时,需要考虑增加寄存器级数。但是到底需要增加到多少级呢?

如上节所述,由于C1,C2通常是未知的,较难通过计算MTBF来估计所需的寄存器级数。也许,需要根据同工艺下的经验值来指导设计。

对于FPGA芯片有文献使用特定方法测量了这些参数,其测量方法和测量结果可以作为一种参考,但是这些值对其他场景下有多大的参考意义,作者也暂时难以给出比较准确的回答。

后记

作者并非微电子科班出身,搜索的文献暂时局限于中文互联网,文中有不少地方只是个人的思考推论,可能会有很多不准确之处,欢迎讨论。

创作不易,如有转载请注明出处。

参考文献:

[2] 【电路笔记 信号】Metastability & 平均故障间隔时间(MTBF)公式推导:进入亚稳态+退出亚稳态+同步器的可靠性计算_mtbf 同步器-CSDN博客

[3] FPGA的亚稳态跟MTBF_亚稳态mtbf-CSDN博客

[4] 跨时钟域背景下的亚稳态和MTBF 是什么_亚稳态mtbf-CSDN博客

[8] 汽车芯片的可靠性设计:控制亚稳态,提升稳定性- 知乎

[9] Metastability and Synchronizers A Tutorial(主要的计算与仿真结果出处)

[10] Understanding Metastability in FPGAs(出自Altera,下载地址http://www.pldworld.com/_altera/html/tip/wp-01082-quartus-ii-metastability.pdf)

[11] Metastable Recovery in Virtex-II Pro FPGAs (出自Xilinx,下载地址https://gab.wallawalla.edu/~larry.aamodt/engr435/xapp094_metastability_2005.pdf)

[12] Experimenting with Metastability and Multiple Clocks on FPGAs

[13] Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

[14] Mike Stein, Paradigm Works. Crossing the abyss: asynchronous signals in a synchronous world

[15] Clifford E. Cummings. Simulation and Synthesis Techniques for Asynchronous FIFO Design

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?