概要

FPGA基于VHDL语言的十进制计数器设计,包括频率计部分以及数码管显示部分。

整体架构流程

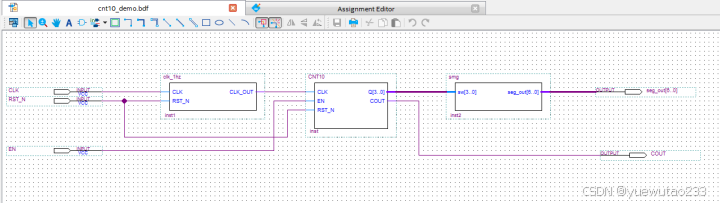

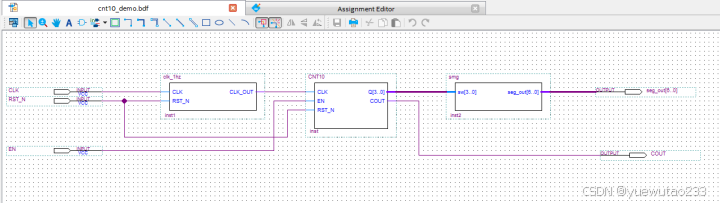

顶层原理图

其中各模块代码如下:

(1)CNT10模块:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT IS

PORT(CLK,EN,RST_N:STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT:OUT STD_LOGIC);

END CNT;

ARCHITECTURE BEHAVE OF CNT IS

SIGNAL CNT : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

Q <= CNT;

PROCESS(CLK,RST_N,EN)

BEGIN

IF RST_N ='0' THEN

CNT <= "0000";

ELSIF RISING_EDGE(CLK) THEN

IF EN='1' THEN

IF CNT = "1001" THEN

CNT <= "0000";

COUT <= '1';

ELSE

CNT <= CNT + 1;

COUT <= '0';

END IF;

END IF;

END IF;

END PROCESS;

END BEHAVE;

clk_1hz模块:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY clk_1hz IS

PORT(CLK,RST_N:STD_LOGIC;

CLK_OUT:OUT STD_LOGIC);

END clk_1hz;

ARCHITECTURE BEHAVE OF clk_1hz IS

SIGNAL CNT : STD_LOGIC_VECTOR(25 DOWNTO 0);

SIGNAL rclk : STD_LOGIC;

BEGIN

CLK_OUT <= rclk;

PROCESS(CLK,RST_N)

BEGIN

IF RST_N ='0' THEN

CNT <= "00000000000000000000000000";

rclk <= '0';

ELSIF RISING_EDGE(CLK) THEN

IF CNT = "01011111010111100001000000" THEN

CNT <= "00000000000000000000000000";

rclk <= NOT(rclk);

ELSE

CNT <= CNT + 1;

END IF;

END IF;

END PROCESS;

END BEHAVE;

smg模块

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY smg IS

PORT (

sw : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

seg_out : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END smg;

ARCHITECTURE trans OF smg IS

SIGNAL seg_in : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS (sw)

BEGIN

CASE sw IS

WHEN "0000" =>

seg_in(7 DOWNTO 0) <= "00111111";

WHEN "0001" =>

seg_in(7 DOWNTO 0) <= "00000110";

WHEN "0010" =>

seg_in(7 DOWNTO 0) <= "01011011";

WHEN "0011" =>

seg_in(7 DOWNTO 0) <= "01001111";

WHEN "0100" =>

seg_in(7 DOWNTO 0) <= "01100110";

WHEN "0101" =>

seg_in(7 DOWNTO 0) <= "01101101";

WHEN "0110" =>

seg_in(7 DOWNTO 0) <= "01111101";

WHEN "0111" =>

seg_in(7 DOWNTO 0) <= "00000111";

WHEN "1000" =>

seg_in(7 DOWNTO 0) <= "01111111";

WHEN "1001" =>

seg_in(7 DOWNTO 0) <= "01100111";

WHEN "1010" =>

seg_in(7 DOWNTO 0) <= "01110111";

WHEN "1011" =>

seg_in(7 DOWNTO 0) <= "01111100";

WHEN "1100" =>

seg_in(7 DOWNTO 0) <= "00111001";

WHEN "1101" =>

seg_in(7 DOWNTO 0) <= "01011110";

WHEN "1110" =>

seg_in(7 DOWNTO 0) <= "01111001";

WHEN OTHERS =>

seg_in(7 DOWNTO 0) <= "01110001";

END CASE;

END PROCESS;

seg_out <= NOT(seg_in(6 DOWNTO 0));

END trans;

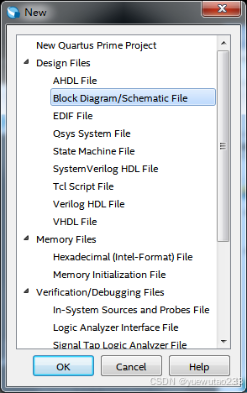

建立原理图文件。如果在建立工程时没有添加设计文件,这时可以新建文件再添加。也可通过选择Project/ Add/Remove Files In Project来添加外部文件。

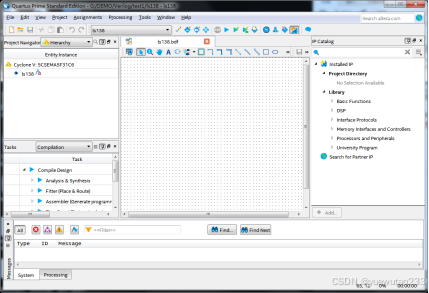

这时,可以开始在原理图上进行设计了。

添加设计。按照电路图添加器件并连线。

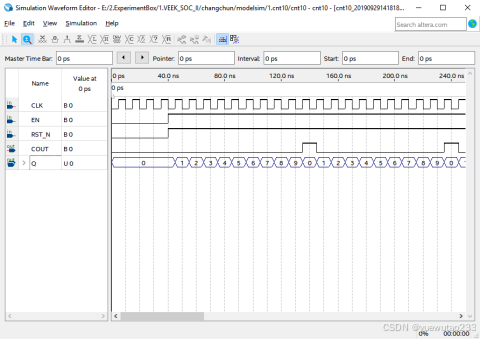

之后进行编译及仿真:

技术细节

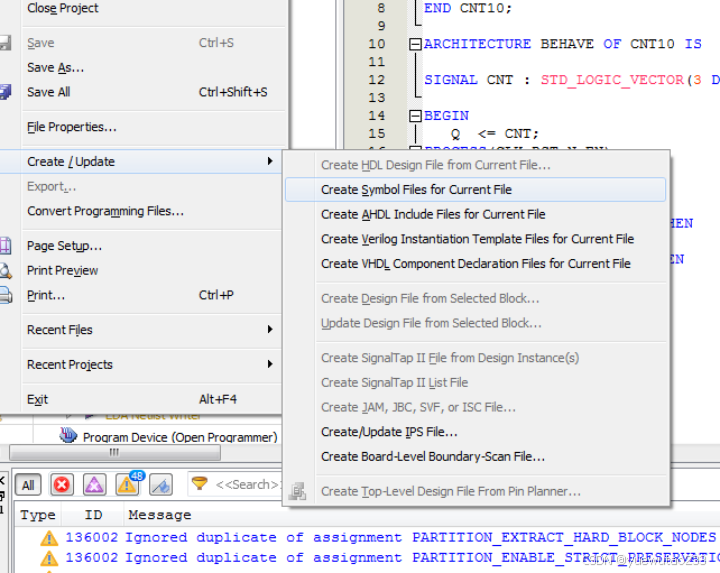

对文件进行create-symbol生成原理图上可视化symbol,在Quartus II软件中选择File->Create/Update->create symbol file for current file

小结

各部分的详细步骤看专栏里其他文章。(更新ing)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?