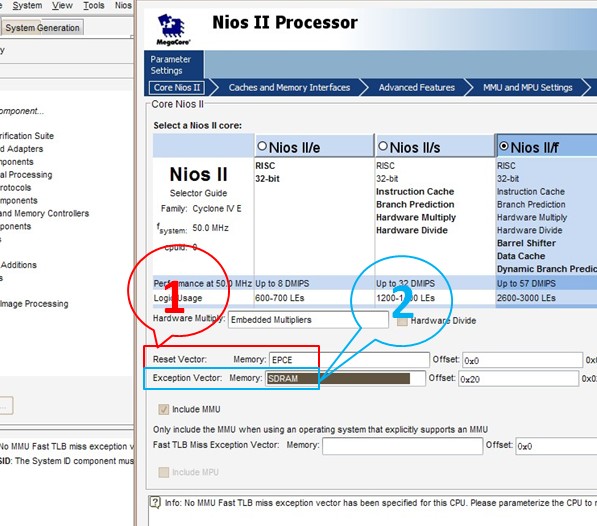

Reset Vector——复位向量

Exception Vector——执行向量

当FPGA进行复位时,FPGA就重新开始执行重新,这是就需要从EPCS中读取程序。由于FPGA的程序存放在EPCS中,所以Reset Vector为EPCS。

Exception Vector——执行向量

在FPGA运行时,首先需要将程序从EPCS中读取,存放在SDRAM中,之后才进行运作。

Exception Vector——执行向量

首先说明两个向量地址都存储着程序。下面分别进行解释。

当FPGA进行复位时,FPGA就重新开始执行重新,这是就需要从EPCS中读取程序。由于FPGA的程序存放在EPCS中,所以Reset Vector为EPCS。

Exception Vector——执行向量

在FPGA运行时,首先需要将程序从EPCS中读取,存放在SDRAM中,之后才进行运作。

以上原理和51单片机执行原理一样。

3384

3384

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?