Flash可以通过四个间接寄存器访问:FLASHCON、FLASHADR、FLASHDAT和FLASHSCL。每个寄存器通过间接读和间接写来访问。

FLASHCON

FLASHCON是一个8-bit寄存器,用于控制FLASH逻辑应答对FLASHDAT寄存器的读和写。FLASHCON寄存器由ReadMode和WriteMode设置组成,具体如下:

| 7:4 | 3:0 |

|---|---|

| WriteMode | ReadMode |

| ReadMode | 描述 |

|---|---|

| 0000 | FLBUSY Polling |

| 0010 | Initiate FLASH read;Increment FLASHADR |

注:未注明的状态都是保留状态

| WriteMode | 描述 |

|---|---|

| 0000 | FLBUSY Polling |

| 0001 | Initiate FLASH Write;Increment FLASHADR |

| 0010 | Initiate page erase on current page if FLASHDAT = 0xA5; Initiate erase of entire FLASH if FLASHDAT = 0xA5 and FLASHADR is set to the address of the FLASH Read Lock Byte or the FLASH Write/Erase Lock Byte. |

注:未注明的状态都是保留状态

FLASHADR

FLASHADR是一个16bit位宽的寄存器,用于指定读操作或写操作的目的地址。FLASHADR在完成一次读操作或写操作后会自动增加。

FLASHDAT

FLASHDAT是一个10-bit位宽的寄存器,包含8bit数据,1bit FLFail和1bit的FLBusy。

| 9:2 | 1 | 0 |

|---|---|---|

| FLData | FLFail | FLBusy |

对FLASHDAT写操作仅仅需要8bit,因为被锁存的最后一位假定是MSB位置。

对FLASHDAT读操作要求11个DR_SHIFT周期,8Cycle用于FLDATA,1个周期用于FLFail,1个周期用于FLBusy,1个周期用于Busy。

FLBusy轮询需要至少两个DR_SHIFT周期,一个周期用于FLBust,另一个周期用于Busy。

FLASHSCL

FLASHSCL是一个8bit寄存器,用于设置FLASH操作时序所需要的预分频值。当工作在内部2MHz系统时钟时,该寄存器应该配置为0x86.

| 7:4 | 3:0 |

|---|---|

| 1000 | 0110 |

FLASH访问流程

在FLASH被编程前,设备需要被复位,看门狗需要被设置为离线模式,否则看门狗可能在FLASH编程过程中发起系统复位,进而导致不确定的行为。

禁用看门狗定时器(WDT)

流程图显示了禁用看门狗定时器的过程,整个过程如下:

- 系统通过加载0x2FFF到指令寄存器迫使系统复位;

- 加载0x1004到指令寄存器读取IDCODE,通过在TDI写入0x0000_0000,从而在接收端TDO获得IDCODE;

- 所有后续的指令地址都需要设置StateCntl为0x4,这样使得CPU核处于SUSPEND状态,使得FLASH处于Off-Line。

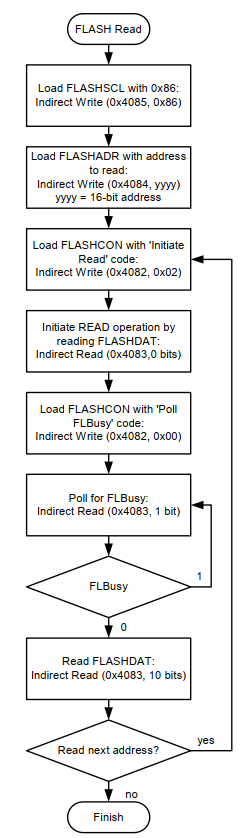

读取FLASH内部的一个字节

具体流程如下:

- 加载0x86到FLASHSCL,使用内部2MHz系统时钟设置合适的FLASH时序。这可以通过一个对FLASHSCL的间接写0x86来实现;

- 将读操作的目标地址加载到FLASHADR;

- 加载0x01到FLASHCON,发起一次读操作;

- 通过读FLASHDAT发起读,这是一次间接读0bit操作;

- 加载0x00到FLASHCON来轮询FLBusy,查看是否处于忙状态;

- 轮询FLBusy直到该信号变低,表示读操作已完成;

- 读FLASHDAT;

4341

4341

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?