前言

从业硬件开发多年,一直有一个难题,就是有些新产品的需要用到老板子的方案,这种情况下就必须保留之前布局的位置号,否则导入新网表后之前的布局就没了,我们layout是外发的,这牵扯到费用到很多的费用不同,之前一直都是在之前的位置号上新增的,导致器件没几个但是位置号到了好几百,改的少还好,改的多了位置号就直接上千了,但是零件其实也就200个左右。之前试过很多办法度不是很好解决这个问题,最近网上研究了一下,找到一个还不错的方法,这个分享给大家。

试验环境

我使用cadence 166版本。wind7 64位,位置号达到1000以上的原理图和pcb源文件,网表是对应的。且layout已完成。

PCB重排前至少保存两个设计文件副本!!! 重排后不能退回。

PCB重排前至少保存两个设计文件副本!!!

PCB重排前至少保存两个设计文件副本!!!

具体操作,

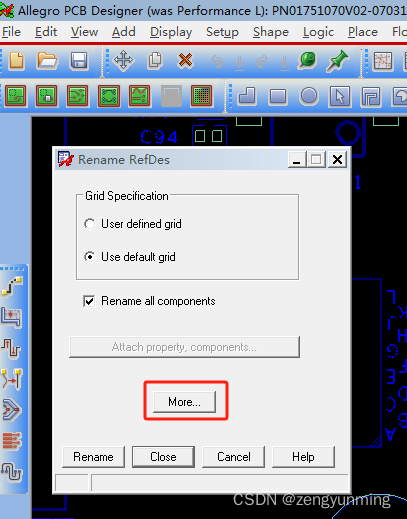

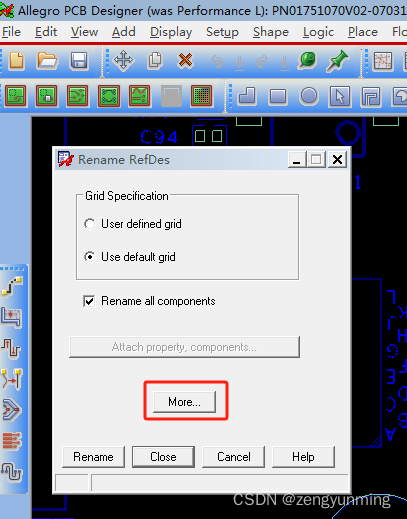

1,打开Logic -> Auto Rename Refdes -> Rename,打开Rename RefDes窗口。

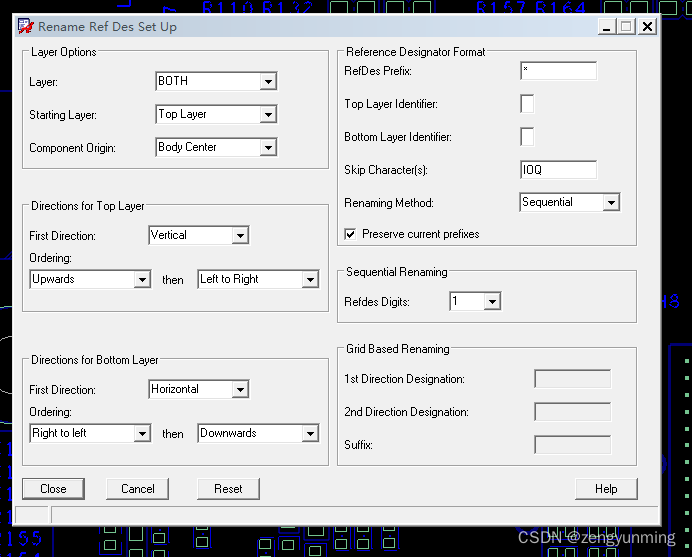

2,点击more,开始按照如下选择配置,熟悉了再慢慢研究。配置完后点击close退出

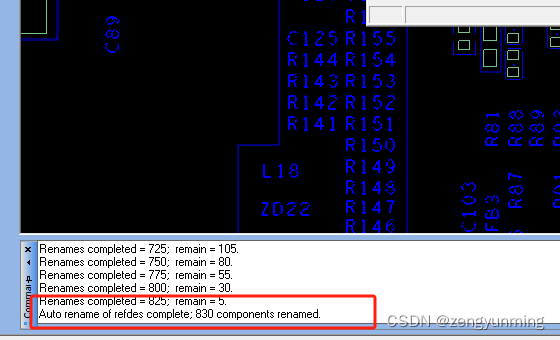

3,点选rename 开始重编位置号,可在log栏看到状态,完成后显示数量

此时你再看pcb 状态是否还是之前一样的,再确认下位置号有么有发生改变。

4,下面再进行原理图位置重编

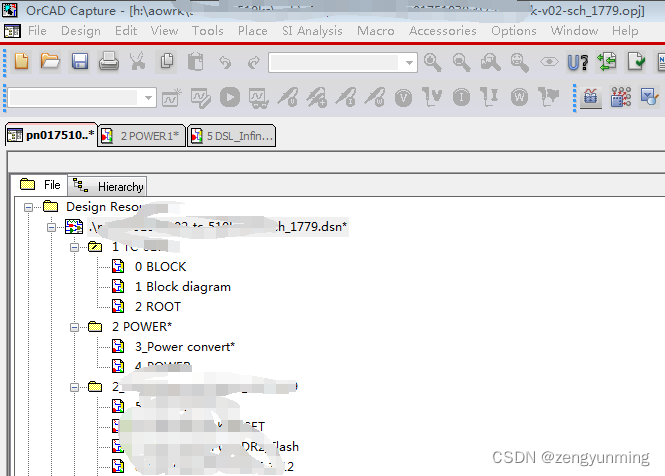

打开capture cis,将之前原理图文件打开,选中文件,再打开菜单Tools -> Back Annotate(或者点击工具栏上的Back Annotate图标),打开反标界面。

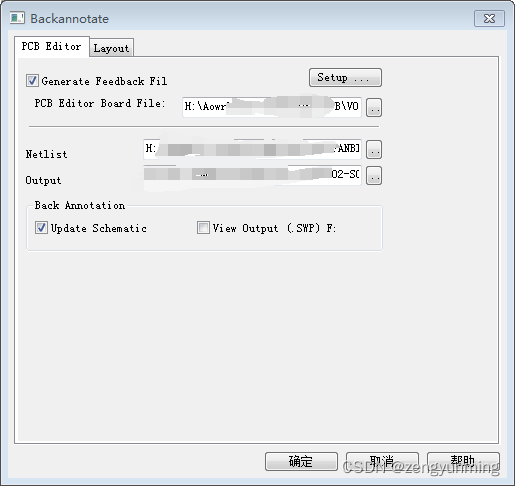

5,选好重遍过的pcb文件,之前的原理图和原理图网表。点击确定

6,弹出窗口再点击确定,等待完成后会发现所以原理图都显示*号,意思出现了变动,

这个时候可以保存导出新的网表再跟变过的PCB文件进行对比下,看看对不对。

结语

这个方法建议在导入了所以封装还没有布局的时候就开始做,这样有问题也好在中间检查。

layout完了在搞万一有问题损失太大。

6947

6947

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?