目录

- DCI

- DCI-T

- SSTL/HSTL/HSU

- ODT

- 案例分析-LPDDR3

DCI

全称 digitally controlled impedance 数字控制阻抗。

只能用在单向信号中,对应源端串联,远端并联。

通常在FPGA,DDR中有两个专用引脚,VRN 和 VRP.

内部阻抗校准就是通过两个外部参考电阻实现。

通常VRN 接2*Z0到VCCO

VRP接2*Z0到VCCO

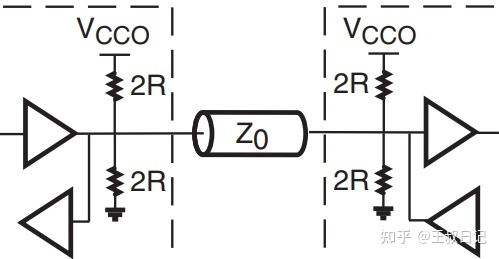

- 输出阻抗控制

包括两种形式,不管什么情况,必须保证源端阻抗等于Z0.

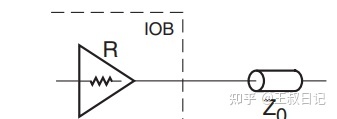

- R=Z0

图1

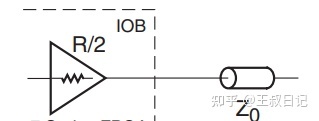

2. R=2*Z0

图2

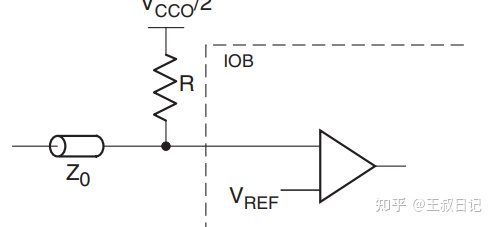

- 输入戴维南

我们经常看到DDR中电阻端接到VCCO/2=VTT的形式。

其目的就让负载电阻等于Z0.

图3

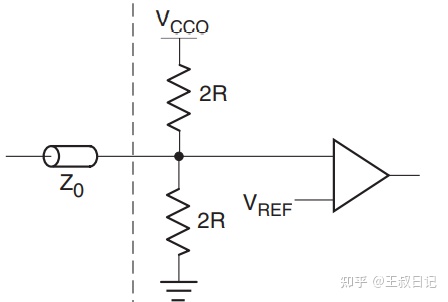

如果采用两个2R电阻一个接VCCO,一个接地其戴维南等效电路同图3

图4

DCI-T

全称 The 3-state digitally controlled impedance 三态数字控制阻抗。

DCI解决的是单向信号匹配问题,但是如果是双向信号怎么办?

DCI-T 就是为了解决双向通信阻抗匹配问题。

当发送时,左边的电阻网络关闭,右边打开

当接收时,左边的电阻网络打开,右边关闭。

图5

SSTL/HSTL/HSUL

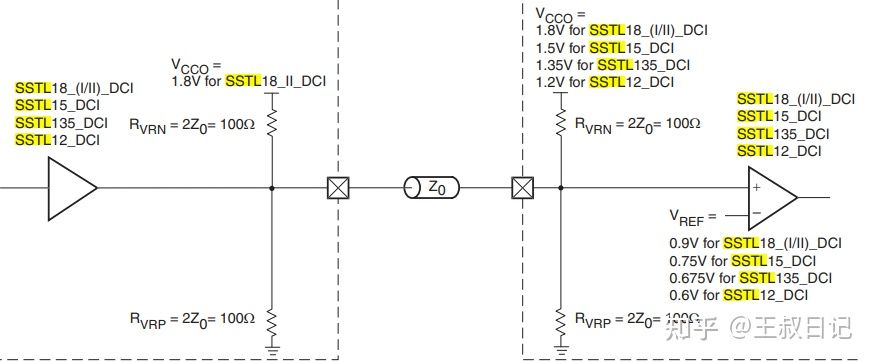

- SSTL

全称STUB SERIES TERMINATED LOGIC 短截线串联端接逻辑。

我们所熟知的DDR 采用的就是这个标准。

DDR2 采用SSTL18, 1V8电源

DDR3 采用SSTL15, 1V5电源

DDR3L 采用SSTL135, 1V35电源

DDR4 采用SSTL12, 1V2电源

目前有两个标准,CLASS-1和CLAS-2

CLASS-1只有输入有戴维南模式,输出没有,且只支持单项传输。

CLASS-2输出和输出都支持戴维南模式,且支持双向传输。

- 通常结构

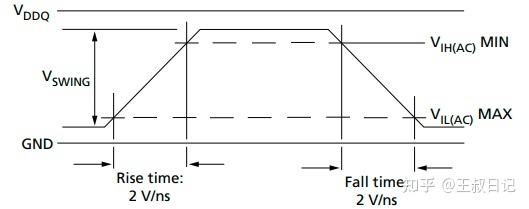

发送同LVCOMS构造相似,接收端采用VREF,具有更小的摆幅和速度。

单端单向模式

图6

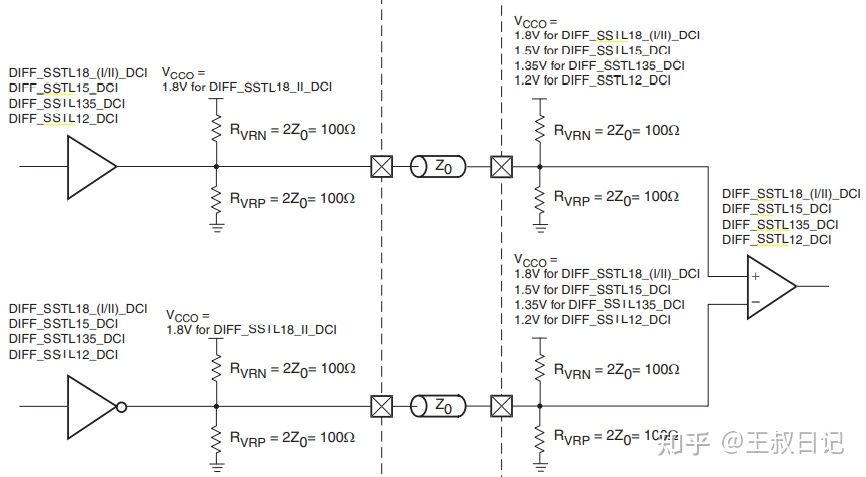

差分单向模式

图7

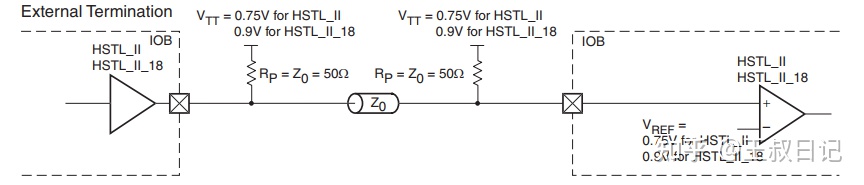

- HSTL

全称 The high-speed transceiver logic 高速传输逻辑。

常应用在1000phy,和存储器中。

结构和SSTL类似.

CLASS-1只有输入有戴维南模式,输出没有,且只支持单项传输。

CLASS-2输出和输出都支持戴维南模式,且支持双向传输。

图8图9

HSTL和SSTL 输入和输出端端接必须存在,不可以分时处理。

这点和DCI-T 完全不同,DCI-T只是一种端接技术,而HSTL和SSTL是一种接口协议。

以图8为例,假设源端电阻为25Ω,则信号线上的直流电压VDC=0.25V

当输出为VDDQ时,到负载端的电压VAC=0.5+VDC=0.75V

当输出为GND时,到负载的电压VAC=0.25V

图10

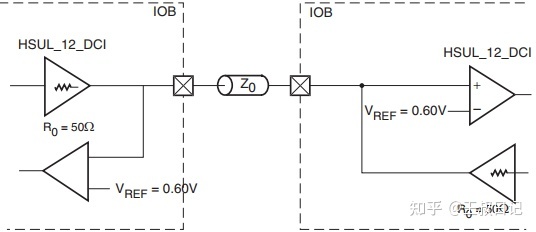

- HSUL

全称 High Speed Unterminated Logic 高速非端接逻辑。

常在LPDDR2/3中使用。

只是在源端串联匹配,没有在接收端并联匹配,功耗可以做到特别低。

图11

ODT 和LPDDR3 调试后面介绍

8311

8311

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?