前言

本文介绍FPGA的FIFO模型与应用。

一、FIFO模型

二、FIFO应用

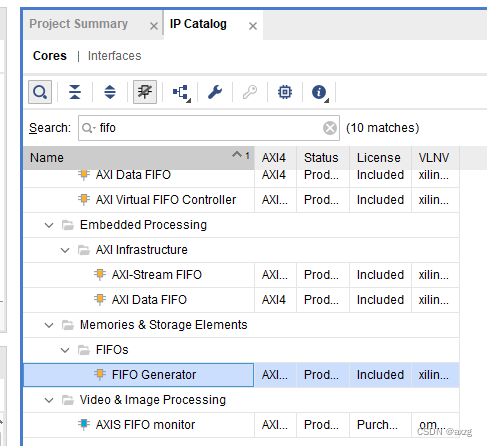

1.ip核配置

1.1 Basic

(1)

FIFO Generator

(2)

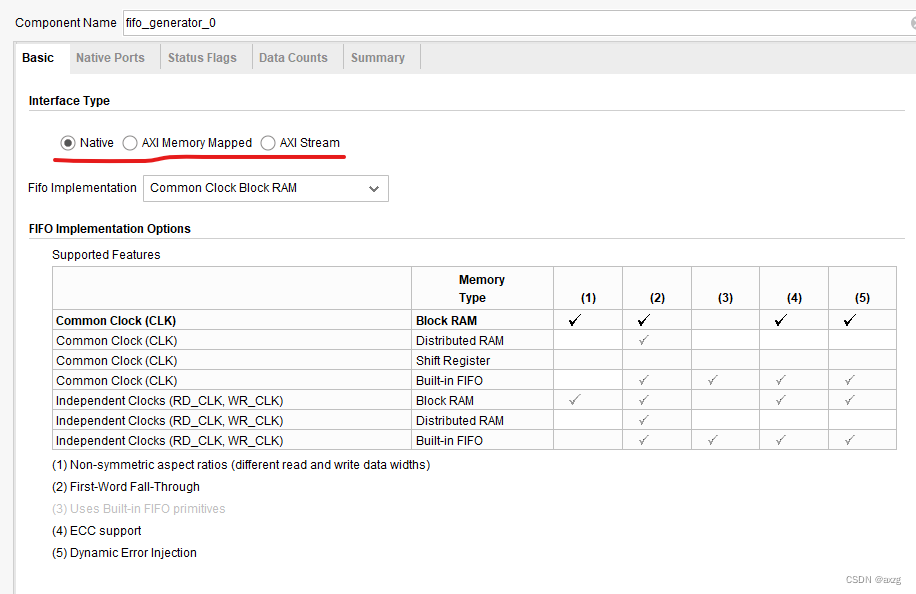

Interface Type

3种接口:

Native:自己写verilog时用的接口

AXI Memory Maped:软核或者静态硬核用的接口

AXI Stream:AXI的流接口,传输流数据,高速数据的高速设备接口

(3)

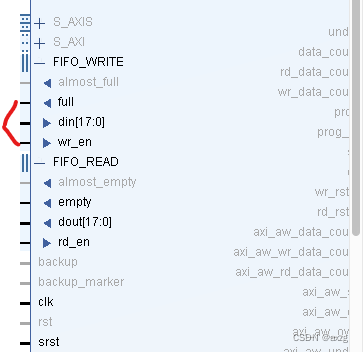

FIFO_WRITE

full:FIFO满了的信号,不能再写了,即使写也写不进去

din[17:0]:要数据FIFO的数据

wr_en:类似于1个门,只有这个门打开了,数据才能写进FIFO

(4)

FIFO_READ

empty:FIFO空了的信号,不能从FIFO中再读数据,即使读也是无用的数据

dout[17:0]:从FIFO中读到的数据

rd_en:类似于1个门,只有这个门打开了,数据才能读出FIFO

(5)

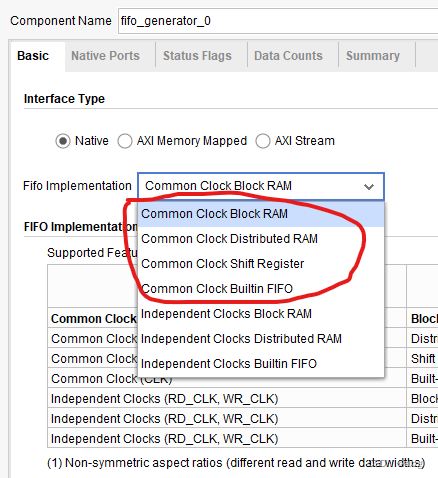

Fifo Implementation

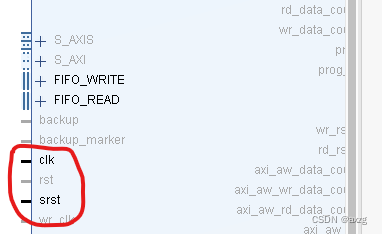

1)Common Clock

写入的同步时钟和读出的同步时钟是同一个

只有一个clk

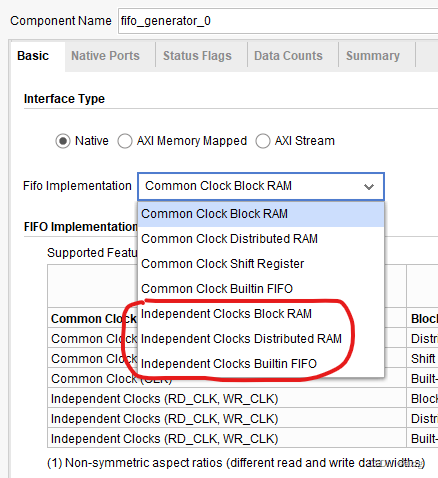

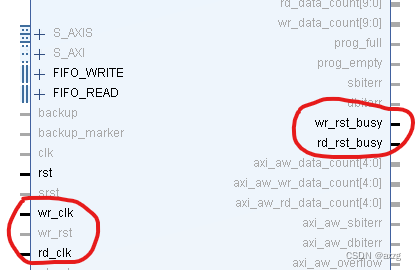

2)Independent Clocks

有wr_clk和rd_clk

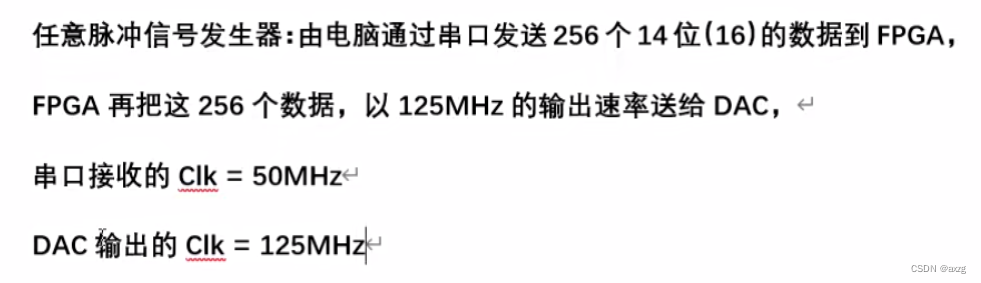

双时钟应用场景

需要以50M时钟写入FIFO,以150M速率从FIFO中读出数据

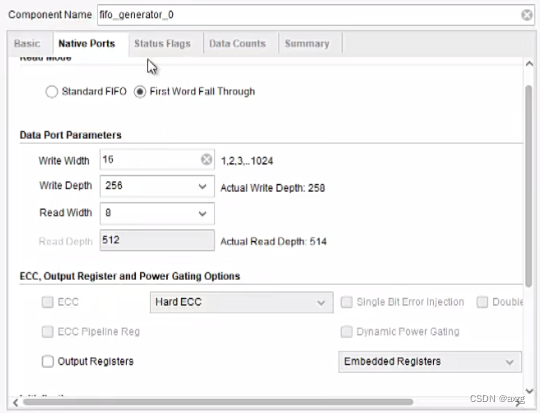

1.2 Native Ports

本地端口

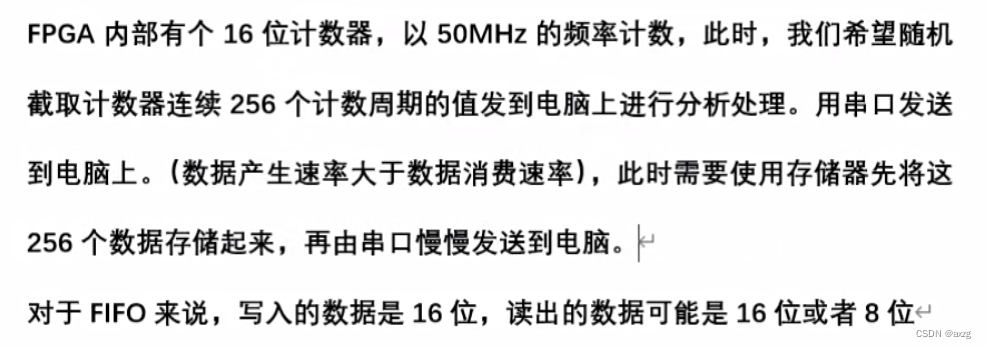

以下面例子为例

(1)Standard FIFO

标准模式下,仅在用户给了读请求rd_en之后,数据才会给到端口供用户使用,先有rd_en,dout[7:0]上面数据才有效。

(2)First Word Fall Throuth

只要FIFO中有数据,端口就会送到端口上供用户读使用,不需要产生rd_en信号。数据送到端口,用户直接去用,用的就是进去的第一个数据,当一个数据取出之后,用户给一个rd_en信号,告知FIFO已经把数据取走了,接着FIFO就会把下一个数据送到端口供用户使用。rd_en信号更像一个应答信号,告诉FIFO送到端口的那个数据已经取走了,赶紧把下个数据放到这来。

(1)Write Width

FIFO写入端口数据宽度,比如16位

(2)Write Depth

FIFO中存储的数据,比如最多数量256个16位的数据。Write Depth要比256大,512也行,但不能比256小。

(3)Read Width

FIFO读出端口数据宽度8位或者16位都行

(4)Read Depth

正常是灰色的,自动生成。如果Read Width为8,则Read Depth值为512,如果Read Width为16,则Read Depth值为256。

可以理解为按16位来写,最多能写256个数据,按8位来读的话,可以读到512个数据。ip核内部可以做处理,比如说它帮你读出16位数据出来,但是它给你一次只往你端口给8位数据,当下一次读的时候另外8位再给你就行了。

(5)Output Registers

加一个寄存器,主要是提高存储器的时序性能。如果没有这个寄存器,那么输出数据相当于一个组合逻辑,从ram直接出来到组合逻辑,这种情况的时序性能没有加一个寄存器后再输出的时序性能好。

但是加上Output Regidters会有一拍的延迟,当发出red请求信号到数据到达read端口,因为有寄存器,所以会晚一拍。

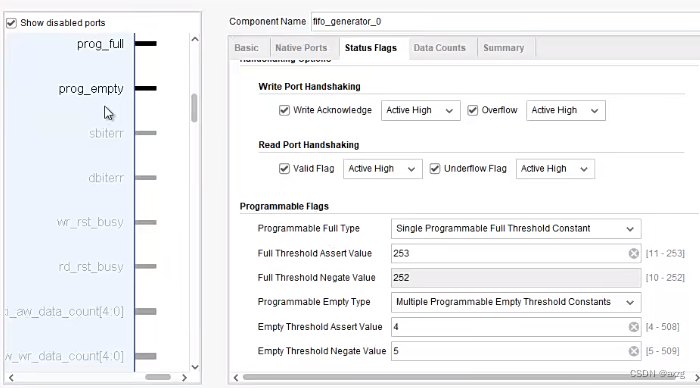

1.3 Status Flags

(1)

Almost Full Flag

比Full信号提前一个周期产生

如果FIFO256深度,在写第256个数据,FIFO内部实际当前还是只有255个数据,就没有full信号,正常当写入第256个数据之后,下一拍把FULL信号拉高,但是实际上不是256个数据往里一写FULL信号就生效。假如FIFO有延迟,因为写进去要过一会才生效,下一拍检测FULL信号的时候可能还没有升高,数据就可能写入第57个数据,这时后这个第257个数据可能会丢。

(2)

Almost Empty Flag

比Empty信号提前一个周期产生,提前知道要空了,这样读完一个数据之后避免再多读一个数据,因为在临界状态,有的时候很难把控。

Write Port Handshaking

(3)

Write Acknowledge

答应答信号

写完给一个应答

(4)

Overflow

溢出信号

FIFO256深度,若写257个数据的时候会溢出

Write Port Handshaking

(5)

Valid Flag

读数据有效信号

若读有延迟,假如读了之后两拍才出来,当valid信号有效,通知我们数据已经送到读端口可以使用。

(5)

Underflow

读空信号

FIFO里面没数据了,你再去读,就有下溢出,读出来的数据肯定不对。

Programmable Flags

(7)Programmable Full Type

可选Mutiple programmable Full Threshold Constants

(8) Full threshold Assert Value

253,表示当FIFO数据多于或等于253个时,prog_full信号拉高

(9)Full threshold Negate Value

252,表示当FIFO数据少于252个时,prog_full信号拉低

(10)Programmable Empty Type

可选Mutiple programmable Empty Threshold Constants

(5)Empty threshold Assert Value

4,表示当FIFO数据小于或等于4个时,prog_empty信号拉高

(11)Empty threshold Negate Value

5,表示当FIFO数据大于5个时,prog_empty信号拉低

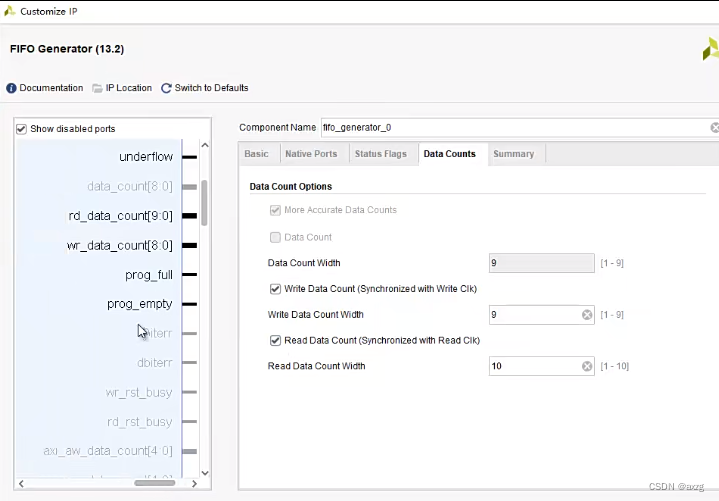

1.3 Data Count Width

观察FIFO当前有多少数据

(1)Write Data Count

勾选后,wr_date_count[8:0]可以实时告诉你FIFO中有多少数据了

(1)Read Data Count

勾选后,rd_date_count[9:0]可以实时告诉你FIFO中有多少数据可以读

rd_date_count位宽比wr_date_count多1位,是因为读的深度是512,写的深度是256

总结

以上就是今天要讲的内容,本文介绍了FIFO模型和应用。

4137

4137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?