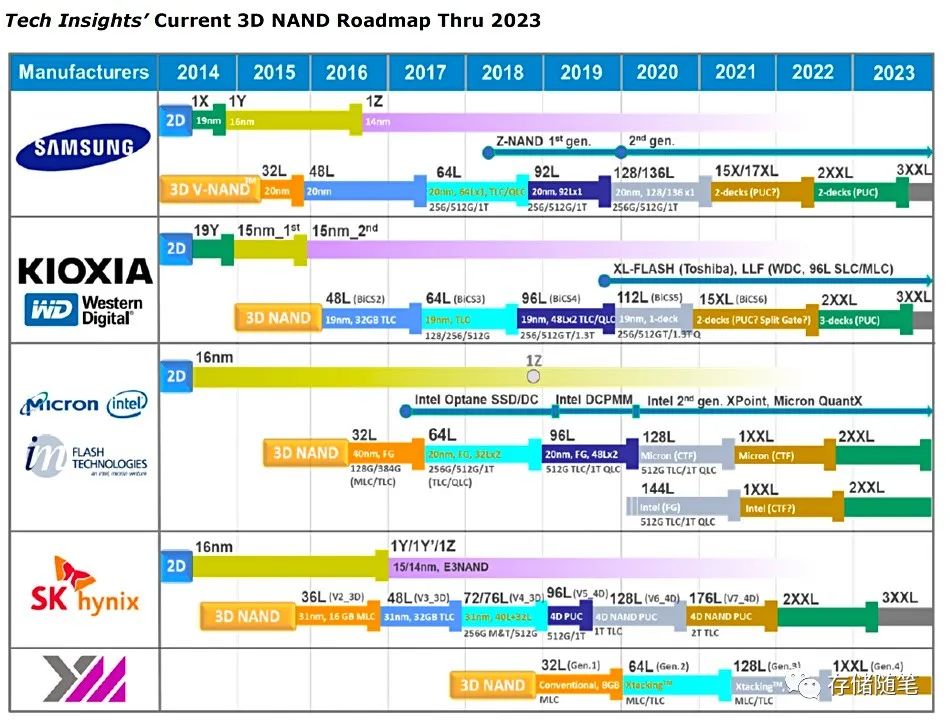

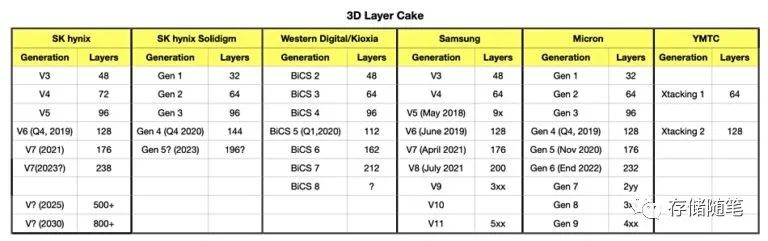

自2014年3D NAND问世,就一直聚焦着全世界的目光。经过多年的沉淀,3D NAND行业可谓是"百家"峥嵘。说"百家"是有点夸张了,说白了,3D NAND行业也就是指三星、东芝、西部数据、美光、SK海力士等这些Flash原厂巨头,因为他们基本完全把控着3D NAND的命脉。中国公司此前在此领域毫无话语权,甚至连收购、合作外资公司都没可能,想获得突破还得靠国产公司自立。值得欣慰的是,长江存储科技在武汉投资国家存储芯片基地,已经迎头赶上,迈进第一阵营。

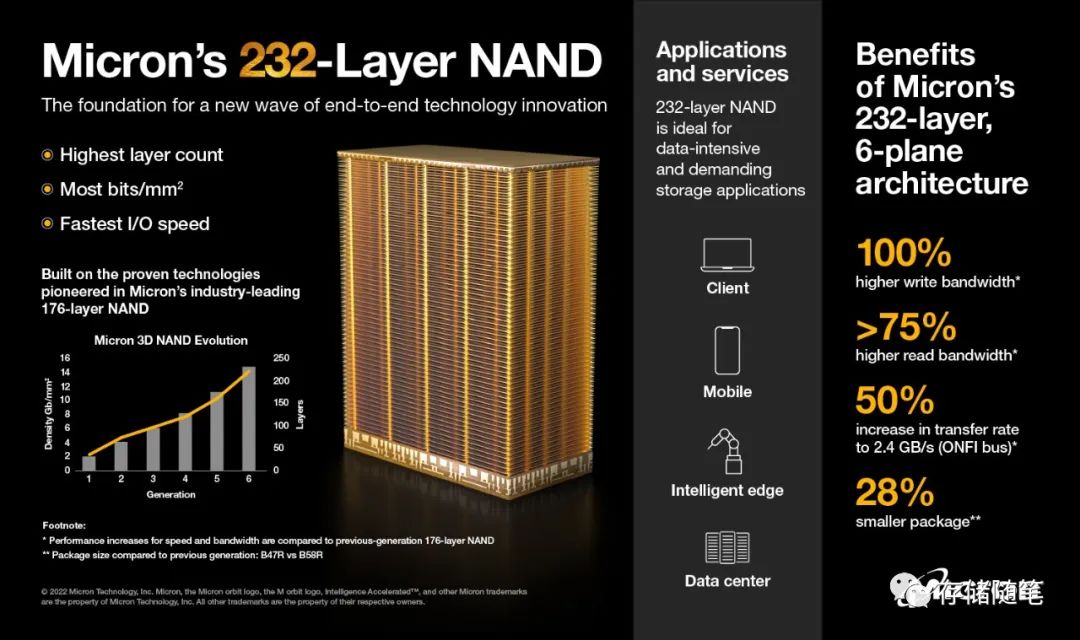

3D-NAND的层数堆叠,已经成为各大厂商竞相追逐的目标。目前主流厂商已经到了第6代工艺,Micron刚刚宣布完成232L 3D TLC NAND,读写性能都得到大幅提升,采用的是双堆栈技术。

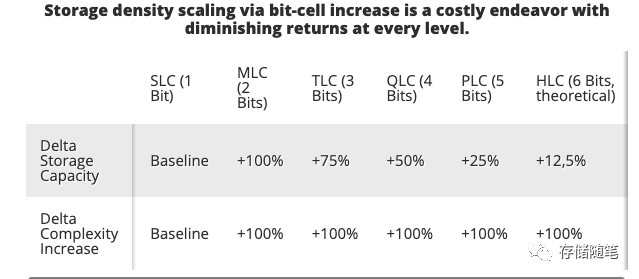

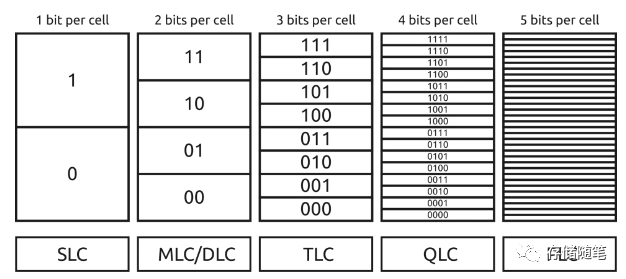

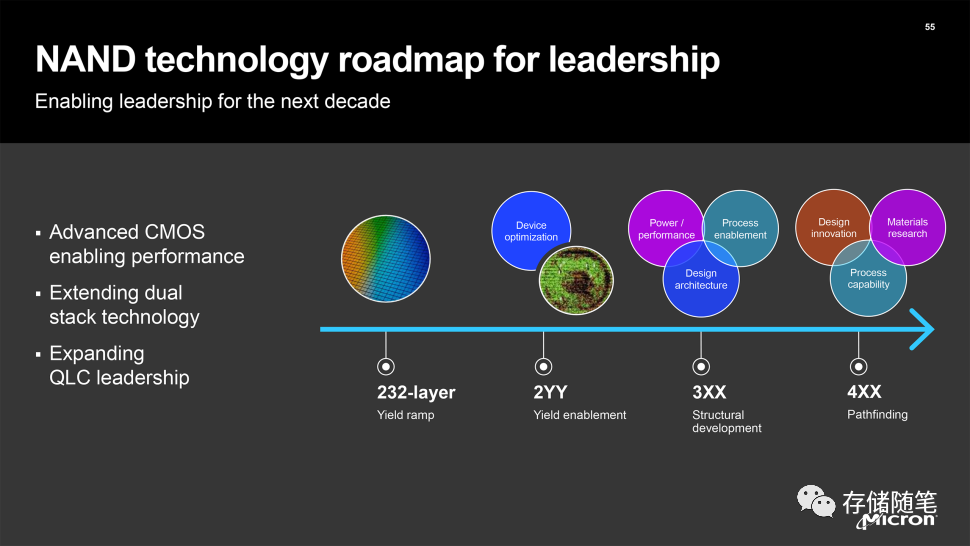

从Micron透露的路标来看,对NAND技术的研发也是持续投入,争取一直处于领先的地位,当前主要在TLC,后续会在QLC继续发力。据了解,Micron在PLC NAND上暂时未打算重点投入,这也跟PLC NAND的可靠性需要更大的技术支撑,研发投入更大有关。同样的工艺研发投入,随着bit/cell的增加,容量的收益却在下降。

更多PLC/QLC信息请参考:PLC SSD虽来但远,QLC SSD火力全开

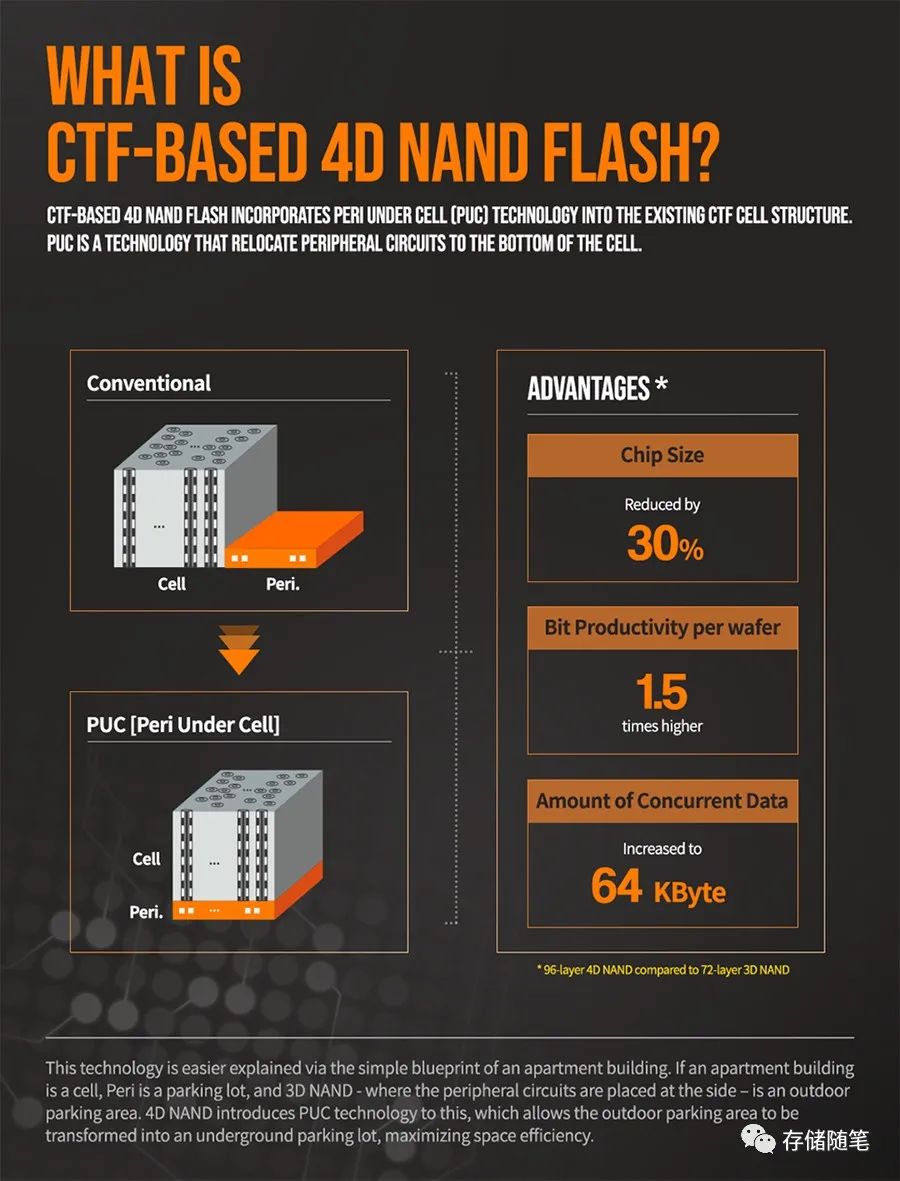

在Micron宣布232层之后,海力士Sk Hynix也接着发布了238层 512Gb TLC 4D NAND。海力士这个4D NAND叫法,噱头大于实际意义,实际也是3D-NAND的变形,类似CuA架构,就是把电路单元放在存储单元之下(Peri Under Cell, PUC)而已.

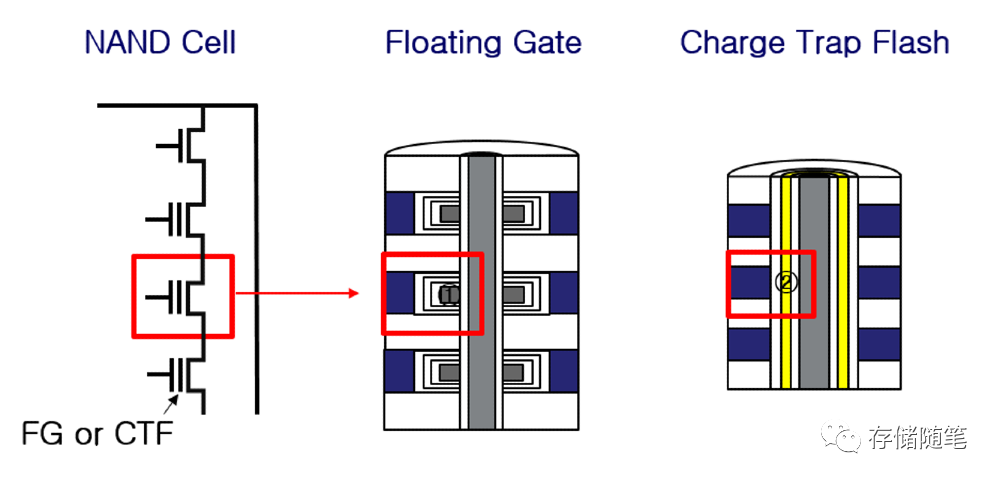

镁光Micron和海力士SK Hynix发布的200L+的NAND,采用的都是Charge Trap Flash(CTF)。目前市场上,也仅剩Solidigm(Intel NAND卖给海力士后新成立的公司)还在坚持使用Floating Gate(FG)架构。与FG浮栅不同,FG浮栅将电荷存储在导体中,而CTF将电荷存储于绝缘体中,这消除了单元之间的干扰,提高了读写性能,同时与浮栅技术相比减少了单元面积。不过,FG浮栅对read disturb和program disturb的抗干扰比CTF要好,总体来说,CTF工艺成本更低,这也是大多数公司选择CTF的原因。

国内厂商YMTC自研的Xtacking技术也到了3.0,预计2023也将发布超过200L层的3D NAND,很可能层数在232层,采用6-plane的设计,相对4-plane的架构,性能将得到超过50%的提升。

根据目前各家NAND原厂的研发状态,预计在2025年,我们将会看到层叠超过500L的3D NAND。甚至在2030之前,超过800L的3D NAND也可能会进入大家的视野。这听上去很Crazy,也许这就是技术的魅力。让我们拭目以待!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?