SSD性能评估中,SSD的性能指标包括IOPS、吞吐带宽,QoS(Quality of Service, 服务质量),其中QoS是重中之重,代表SSD性能的稳定性的指标。影响SSD性能主要因素总结如下。

之前文章(全景解析SSD IO QoS性能优化)中,已经做了全面剖析,本文主要针对NAND后端速率进行深入的解读与学习。

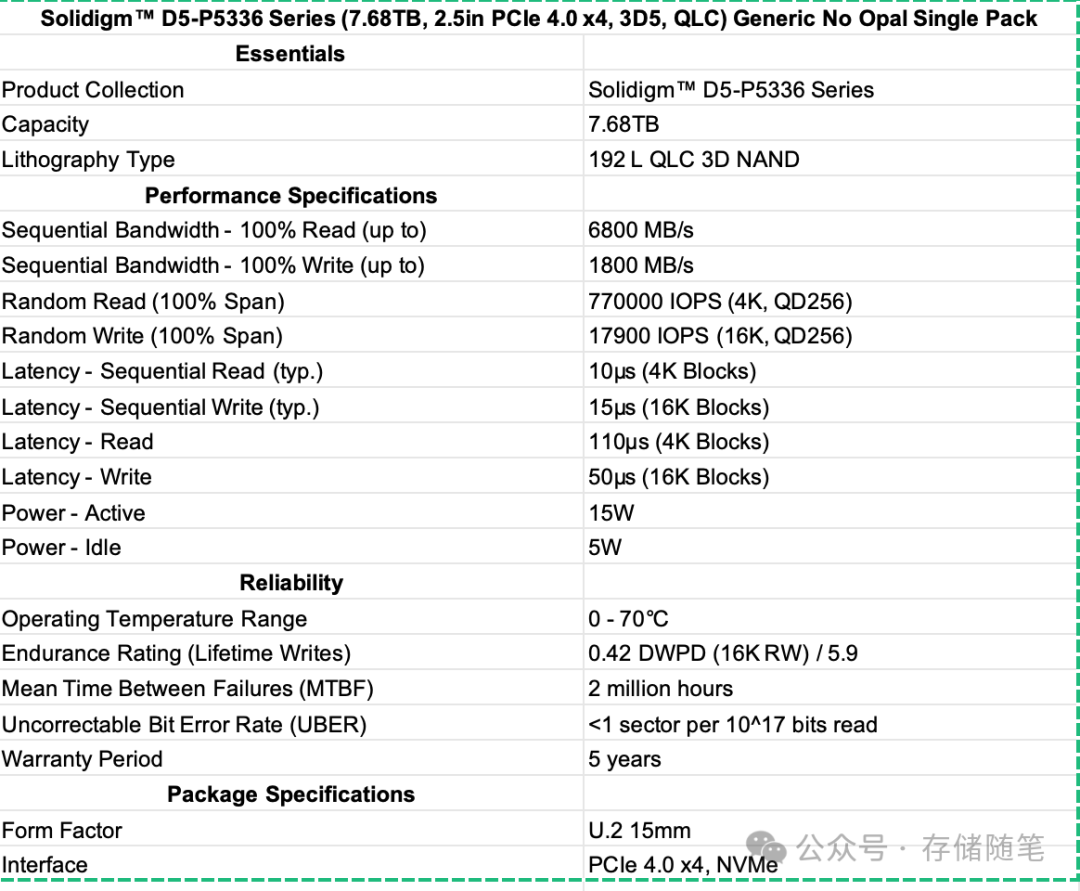

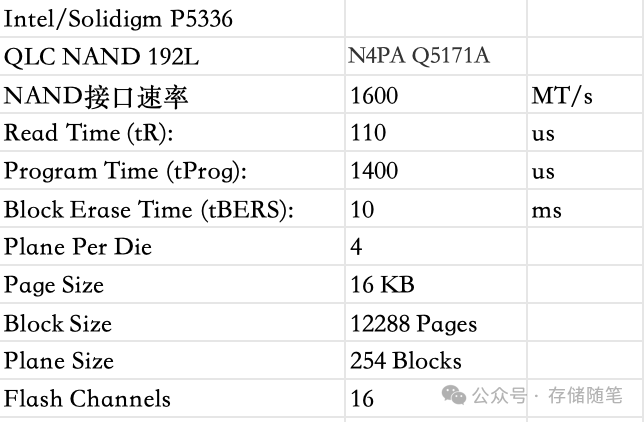

由于计算过程涉及NAND读写延迟数据,本文就以Solidigm P5336 QLC SSD以及相关NAND参数信息作为参考(声明:均为Solidigm官网以及其他公开信息整理):

(1)SSD基本产品信息:

(2)对应NAND关键信息:

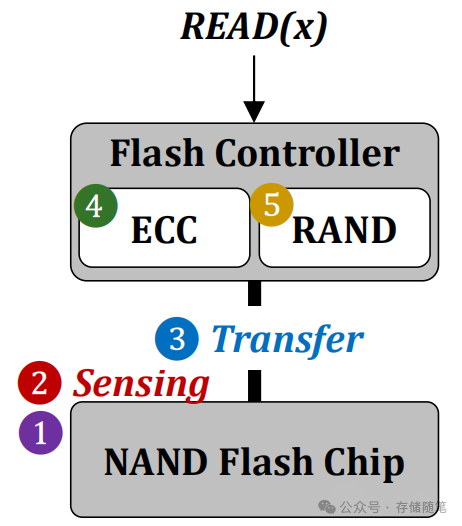

在SSD(固态硬盘)的NAND闪存读取操作中,(tCMD) + tR + tDMA + tECCDEC + (tRND)代表了一次读取操作的总延迟时间,其中每个组成部分代表不同的阶段和它们各自所需的时间。具体解释如下:

-

tCMD: 这代表命令传输时间,即从SSD控制器发送读取命令到NAND闪存开始执行该命令之间的时间。它包含了命令信号在接口上的传输延迟,确保命令正确地被NAND闪存芯片接收和解析。

-

tR: 这是读取延迟时间,指的是从NAND闪存接收到读取命令到数据被实际感应(读取)到闪存芯片内部的页面缓冲区所需的时间。在物理层面上,这涉及到电压施加到存储单元,使得存储在细胞中的电荷状态能够被检测并转化为电信号。

-

tDMA: DMA(Direct Memory Access)传输时间,是指数据从NAND闪存的页面缓冲区转移到SSD控制器的DRAM缓存或直接到主机内存的时间。这个阶段涉及数据在不同存储层次间的物理移动,通常受到I/O总线速度和数据宽度的限制。

-

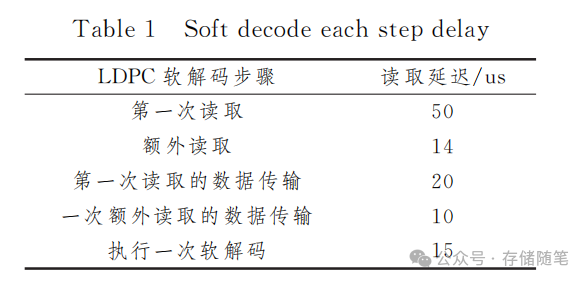

tECCDEC: ECC(Error Correction Code)解码时间,是在数据从闪存读出后,SSD控制器对数据进行错误校验和纠正所需的时间。ECC用于确保数据的完整性,特别是在NAND闪存中常见的位翻转错误。当硬解码无法正确处理错误时,通常会转向软解码,即使这意味着读取操作的整体延迟会增加。根据研究人员实验数据显示,LDPC软解码每一步执行的大致延迟数据如下:

扩展阅读:

-

tRND: 随机化处理是在写入数据之前完成,也是在LDPC encode之前。这部分随机化处理时间,也是会影响数据写入时间tPROG和读取出来tR。

-

tCMD地址传输时间:可以忽略

-

16KB, tR读取时间是110us

-

16KB, tDMA=(16KB/(1.6GB/s*1024))*10^6=9.7us (接口速率1600MT/s,转化IO带宽就是1600MT/s*8bit=12.8Gbps, 也就是1600MT/s*1Byte=1.6GB/s)

-

tECCDEC: 根据上面研究数据,可以设定15us

-

tRND:时间很短,这里暂时忽略

所以,一次读取16KB的总时间Ttotalread=110us+9.7us+15us=134.7us,对应的读带宽=16KB/134.7us=121.6MB/s

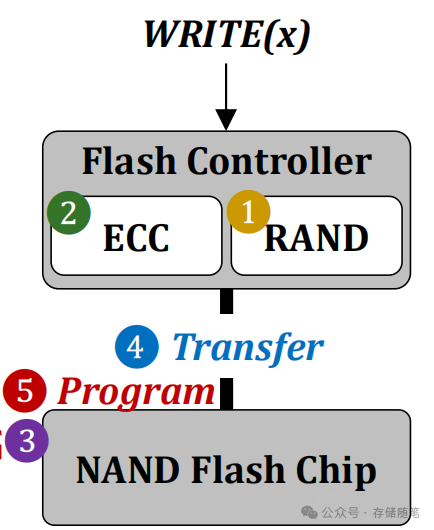

同样的方式,对于一次写16KB的时间Ttotalwrite=(tRND) + tECCENC + (tCMD) + tDMA + tPROG=15us+9.7us+1400us=1424.7us,对应的写带宽=16KB/1424.7us=11.5MB/s

上面计算的都是单次读写的性能,但是在固态硬盘(SSD)中,为了实现高性能,通过同时执行多个操作或利用存储设备内部的多个组件来提高整体性能和吞吐量。

-

多通道架构:现代SSD通常包含多个闪存通道(Channel),每个通道连接到一个或多个NAND闪存芯片。每个通道可以独立执行读写操作,从而实现并行读写,显著增加总带宽。例如,如果一个SSD有4个通道,每个通道同时进行读写操作,那么理论上可以达到单通道操作四倍的吞吐量。

-

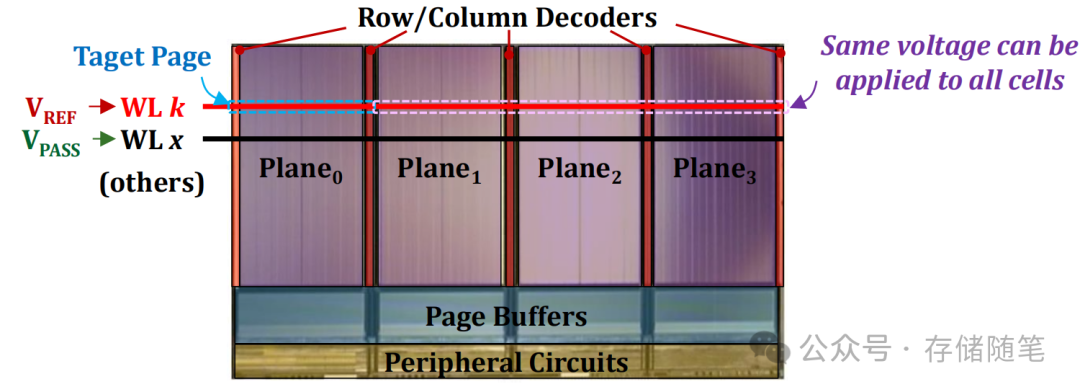

Multi-Plane操作:在一个NAND闪存芯片中,存在多个层面(Planes)。这些层面可以同时进行读或写的操作,只要操作针对的是相同页面偏移。例如,在多层面操作中,两个层面可以同时读取或编程不同页面的数据,从而加倍了单个操作的吞吐量。虽然每操作的延迟可能略微增加,但总体数据传输速率会显著提升。

-

读取与写入缓存:SSD内部通常配备有读取缓存和写入缓存(DRAM),可以并行处理数据传输和数据校验。当系统发送读取请求时,如果数据已经位于读取缓存中,则可以直接返回给主机,而无需等待从闪存中读取,显著减少了读取延迟。对于写入操作,数据可以先写入高速缓存,然后异步地转移到闪存中,允许立即确认写入完成,从而提高了响应速度。

-

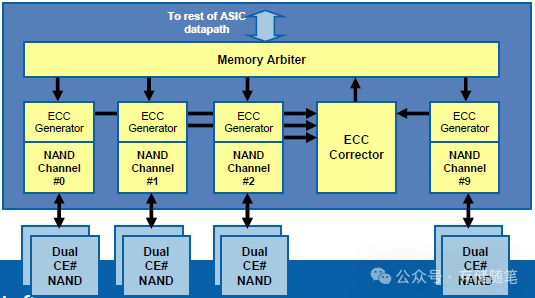

ECC处理并行化:错误校正编码(ECC)过程也可以并行处理,尤其是在数据读取时。使用并行ECC引擎可以加速数据解码过程,减少从闪存读取数据到其准备就绪供系统使用之间的时间。

-

命令调度与队列深度管理:SSD控制器通过优化命令调度逻辑,可以有效管理多个并发请求,确保多个命令在不同组件间高效分配,充分利用各部分的并行处理能力。增加队列深度(Queue Depth)意味着更多的命令可以同时处于待处理状态,进一步提升并行度。

-

垃圾回收(Garbage Collection)与磨损均衡(Wear Leveling):SSD的固件(Firmware)在后台执行这些维护任务时,也会尽量与用户操作并行执行,以减少对前端性能的影响。例如,通过预测和利用空闲时间进行垃圾回收,可以避免与用户请求直接冲突,从而减少对整体性能的负面影响。

Multi-Plane操作:

在一个NAND闪存芯片中,存在多个层面(Planes)。这些层面可以同时进行读或写的操作,只要操作针对的是相同页面偏移。

-

单Page写时间=tECCENC + tDMA + tPROG=1424.7us,对应的写带宽=16KB/1424.7us=11.5MB/s

-

Multi-plane写时间: N-Plane×(tECCENC + tDMA) + tPROG= 4*( 15us + 9.7us) + 1400us = 1498.8us,对应的带宽:4*16KB/1498.8us=43.7MB/s

另外,在一个通道上的Multi-LUN(单CE#多Die)操作是可以有交错Interleave的。当一个NAND闪存处在被占用状态Busy时,可以让第一个NAND闪存自己忙着,主控可以访问同一个通道上的第二个NAND闪存。

举个例子,主控需要连续对一个通道上所有的NAND闪存进行写入(Write)操作,在Interleave功能的帮助下,同一个通道上的NAND闪存形成了一个最大通道利用率的流水线(Pipeline)

考虑Multi-LUN操作(比如2 LUN):

单Chanel-MultiLun-MultiPlane的写时间:2 * N-Plane× ( tECCENC + tDMA) + tPROG = 2*4*(15us + 9.7us ) + 1400us = 1598us,对应带宽=2*4*16KB/1598us=82MB/s

多通道Channel操作:

现代SSD通常包含多个闪存通道(Channel),每个通道连接到一个或多个NAND闪存芯片。每个通道可以独立执行读写操作,从而实现并行读写,显著增加总带宽。

所以,这里16个Channel并发的写带宽=16*82MB/s=1312 MB/s

以上计算仅仅考虑的最简单的情况,仅供学习参考,实际SSD性能带宽与QoS优化是一项非常复杂艰巨的工程。

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?