双非硕士 研一下学期视觉转FPGA(在b站跟小梅哥视频)

长路漫漫,但希望前途光明

省去前面创建工程的内容(如果对创建工程有疑问的,可以看我前面的两篇文章),首先给出跑马灯的逻辑代码,如下图所示:

module led_run(

Clk,

Reset_n,

Led

);

input Clk;

input Reset_n;

output reg [7:0]Led;

reg [24:0]counter;

parameter MCNT =25'd24999999;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter <=0;

else if(counter == MCNT)

counter <=0;

else

counter <= counter +1'd1;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

Led <=8'b0000_0001;

else if(counter == MCNT)begin

if (Led == 8'b1000_0000)

Led <=8'b0000_0001;

else

Led <=Led <<1;

//Led <= {Led[6:0],Led[7]};

end

else

Led <= Led;

endmodule接下来要进行仿真验证,代码如下:

`timescale 1ns/1ns

module led_run_tb;

reg Clk;

reg Reset_n;

wire [7:0]Led;

led_run

led_run_ints0(

.Clk(Clk),

.Reset_n(Reset_n),

.Led(Led)

);

defparam led_run_ints0.MCNT=24999;

initial Clk =1;

always #10 Clk =!Clk;

initial begin

Reset_n = 0;

#201;

Reset_n=1;

#40000000;

$stop;

end

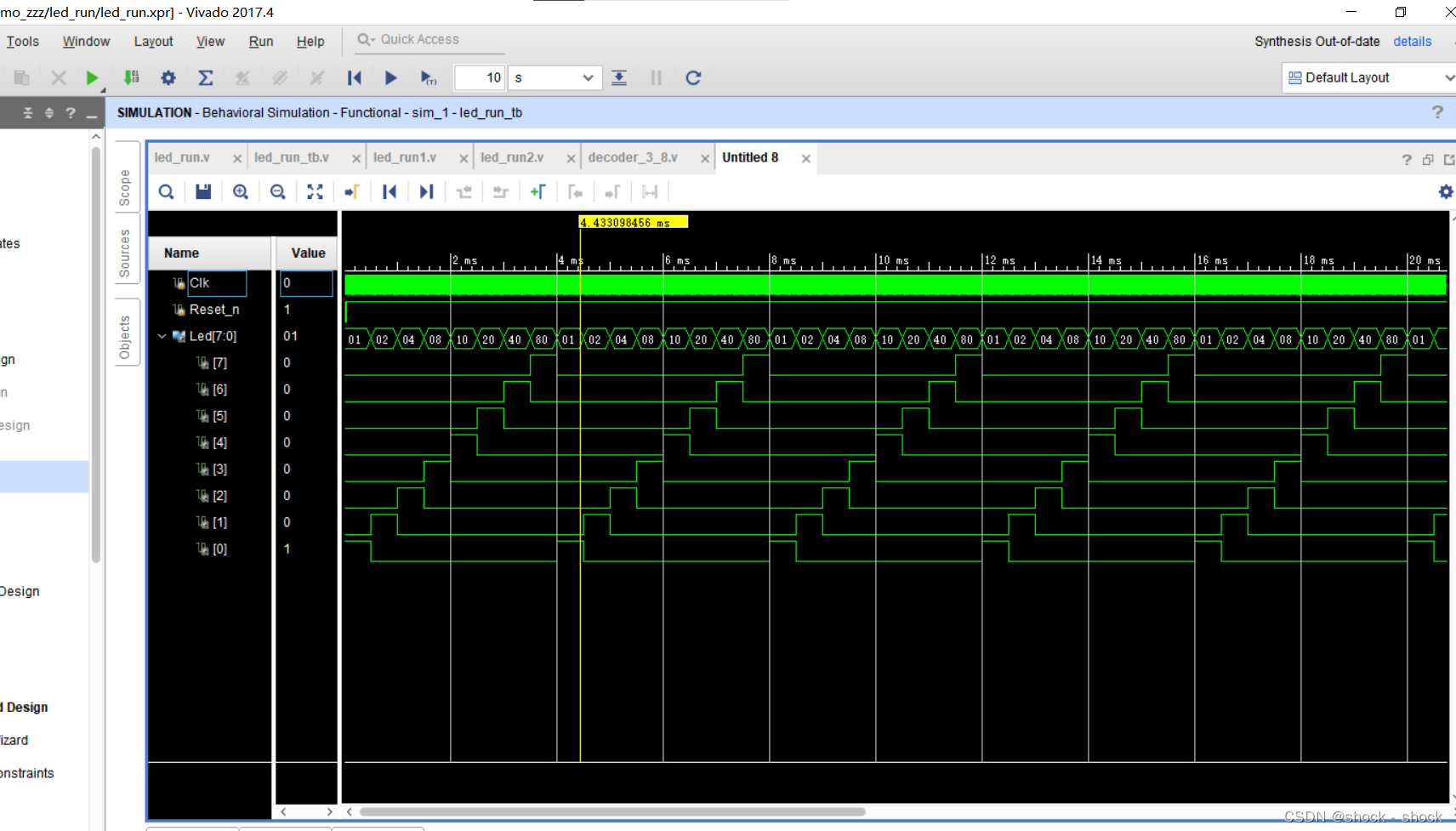

endmodule观察波形图,可以验证我们的代码逻辑是正确的

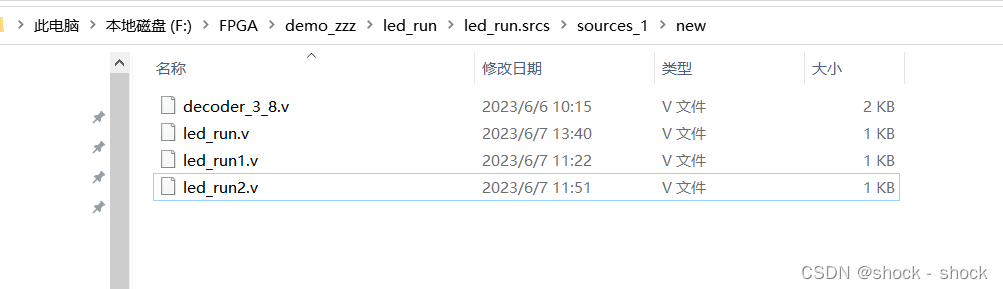

补充,如果使用3-8移码器实现上述效果的话,我们可以将之前创建的decoder_3_8.v文件复制到本路径下,如下图所示

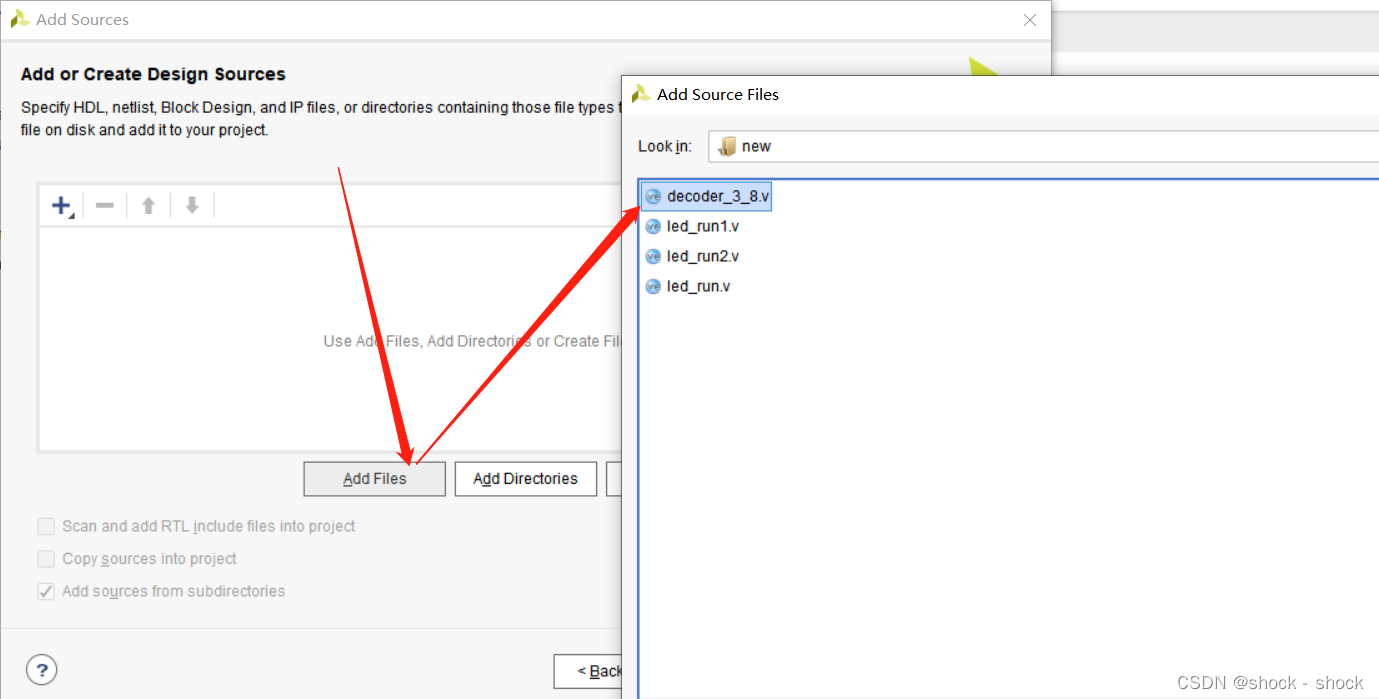

接下来,点击左侧栏中的Add Sources ,同样选择Add or create design sources,点击OK就可以将之前的项目包导进来了。

代码内容如下:

module led_run_test2(

Clk,

Reset_n,

Led

);

input Clk;

input Reset_n;

output [7:0]Led;

reg [24:0]counter;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter<=0;

else if(counter == 24999)

counter<=0;

else

counter <= counter +1'b1;

//使用3-8译码器来实现LED灯的变动

reg [2:0]counter2;

always@(posedge Clk or negedge Reset_n)

if(!Reset_n)

counter2 <=0;

else if(counter2 == 7)

counter2<=0;

else if(counter == 24999)

counter2 <= counter2 +1'b1;

decoder_3_8 decoder_3_8(

.a(counter2[2]),

.b(counter2[1]),

.c(counter2[0]),

.out(Led)

);

endmodule以上,就是通过使用Verilog实现流水灯的实验

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?