1 门电路和寄存器的基本原理

-

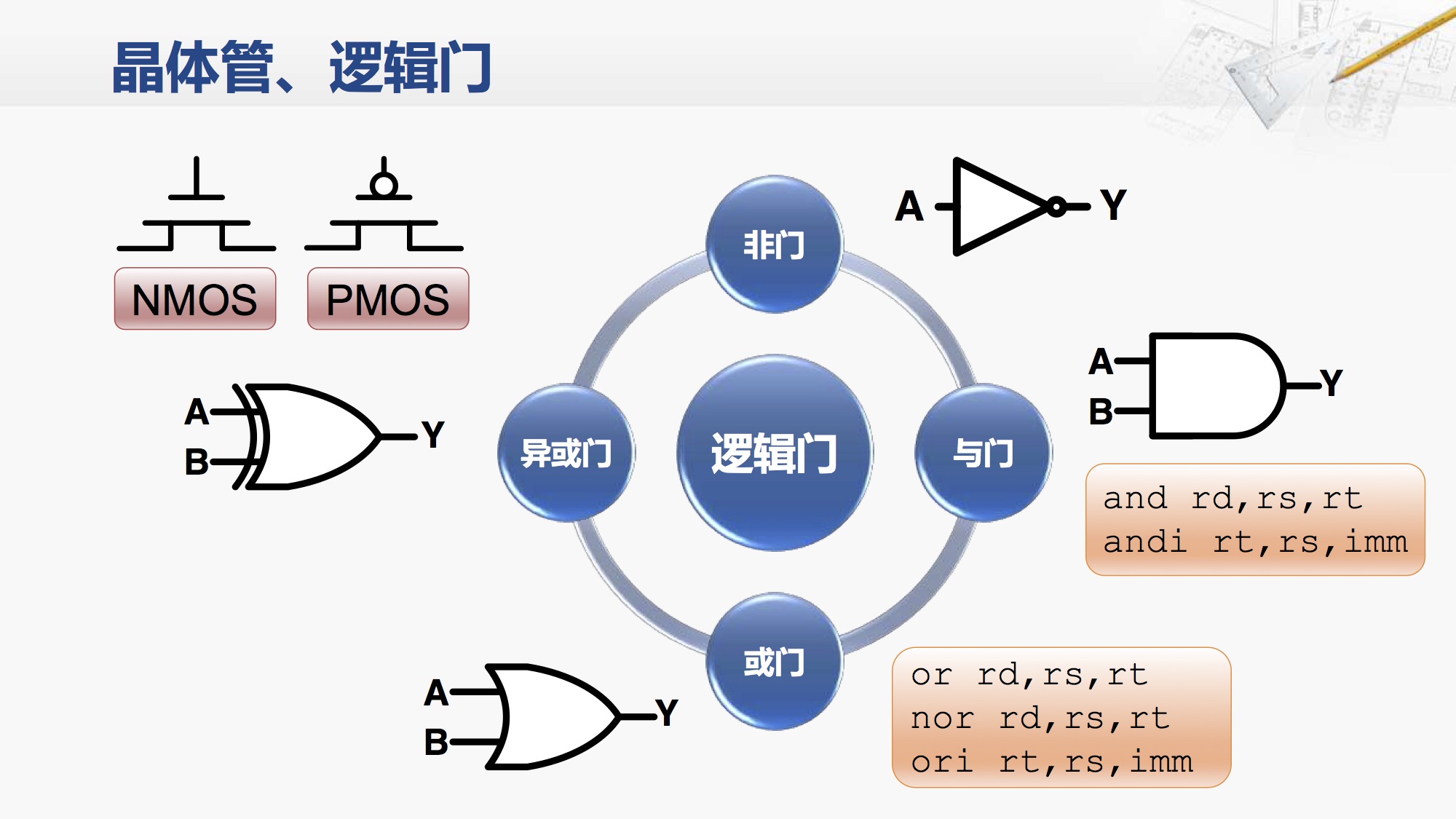

现代集成电路中通常使用MOS晶体管

- Metal-Oxide-Semiconductor:金属-氧化物-半导体 CMOS集成电路(Complementary MOS)

- 由PMOS和NMOS共同构成的互补型MOS集成电路

-

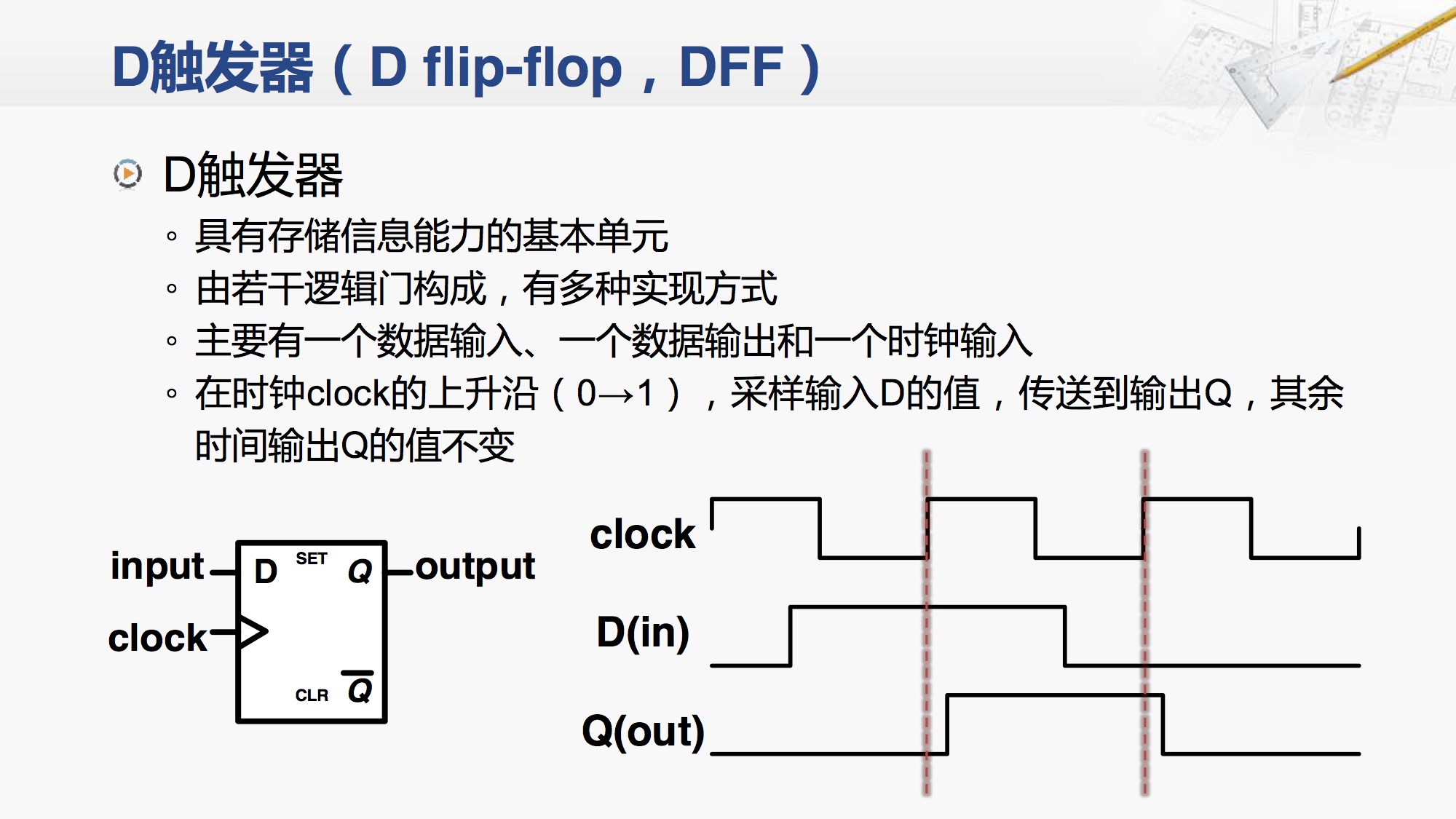

D触发器(D Flip-Flop,DFF)

- 例:采样后经过1秒,传送到输出 → CLK-to-Q时间为1秒

- 每10秒钟采样一次 → 时钟频率为0.1Hz

- 采样前后,输入不能有变化 → Setup/Hold时间

32位寄存器由32个D触发器构成

这只是一个简单的原理性说明,现实中寄存器的实现要复杂的多

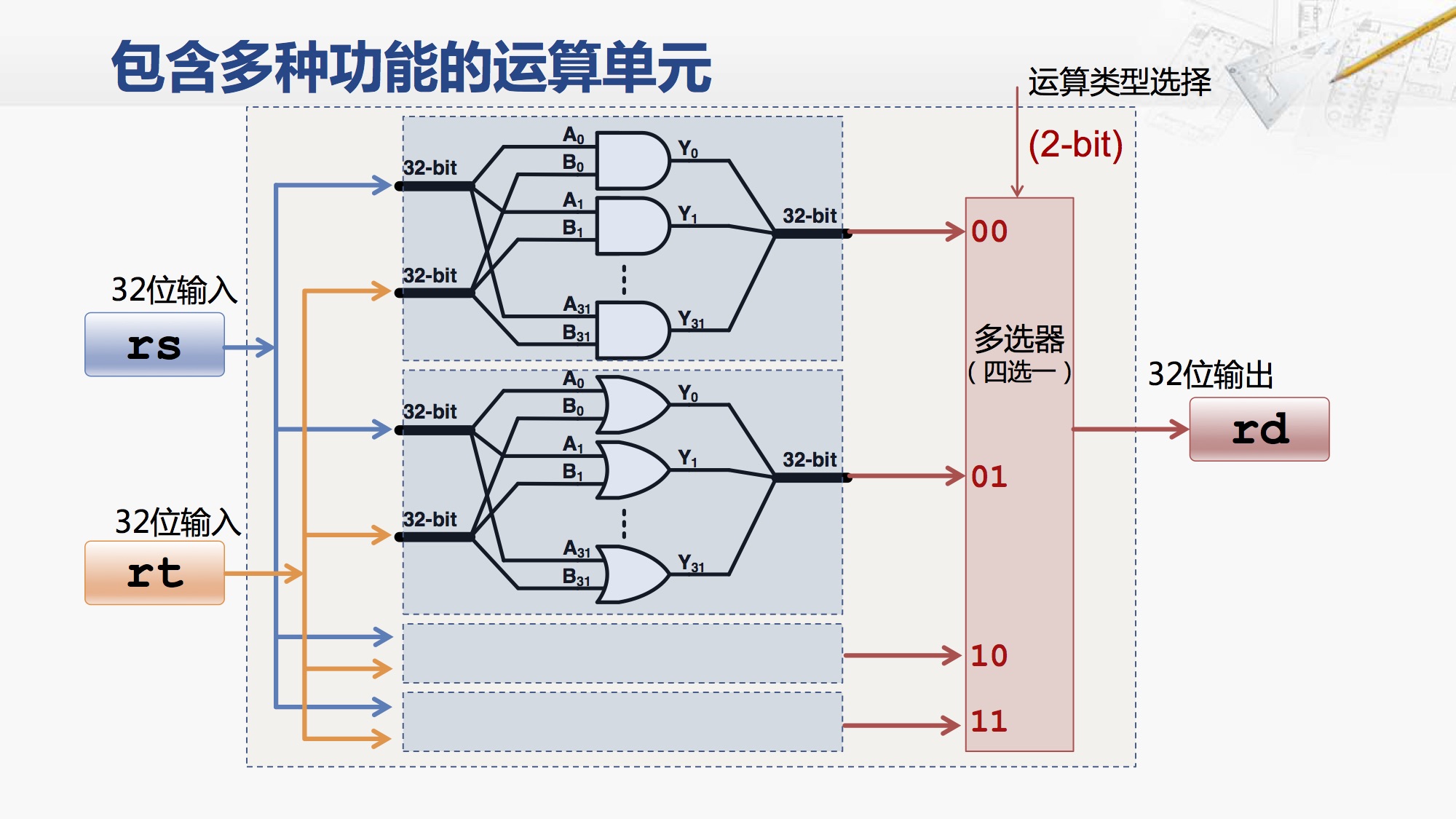

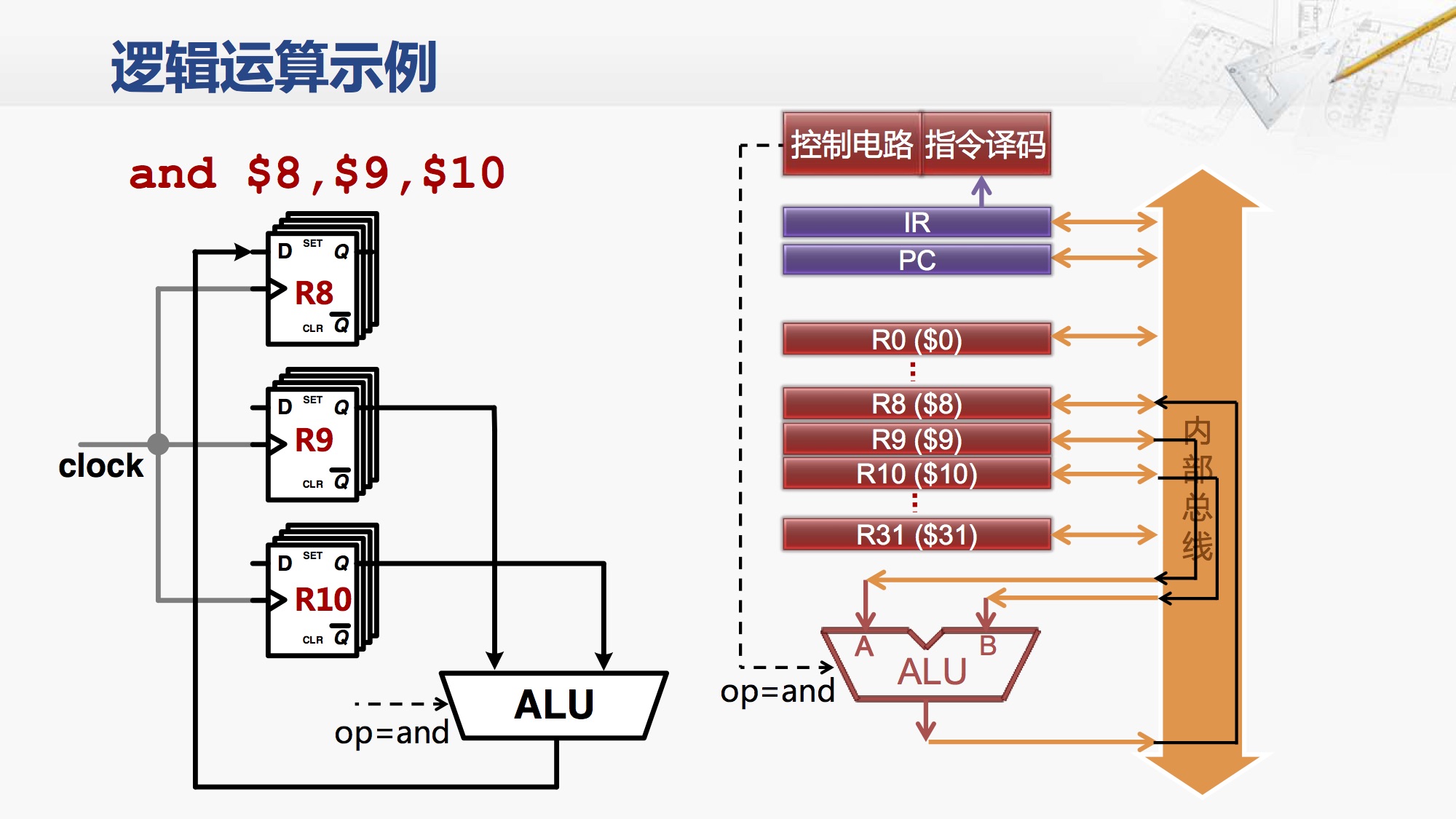

2 逻辑运算的实现

3 加法和减法的实现

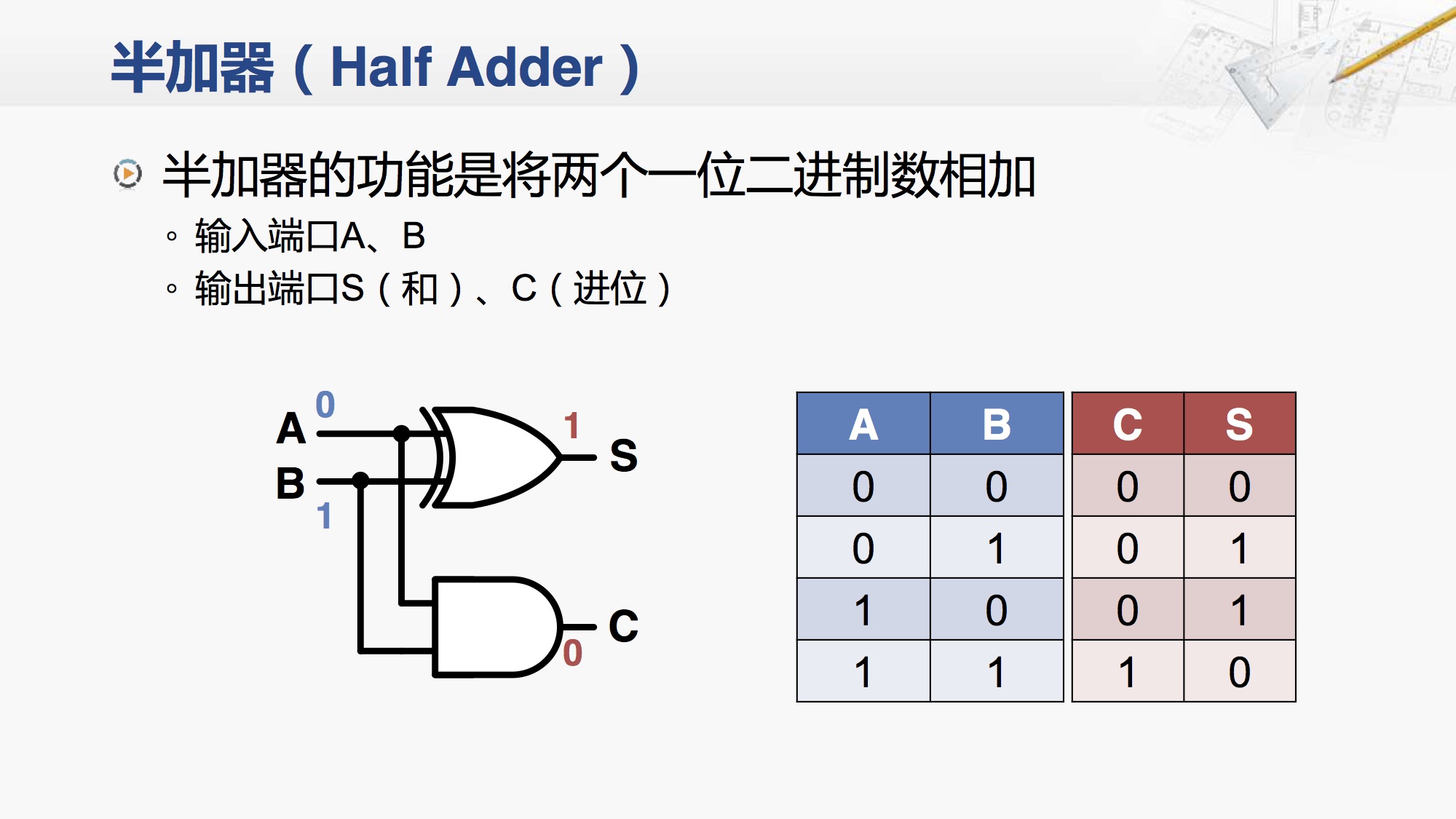

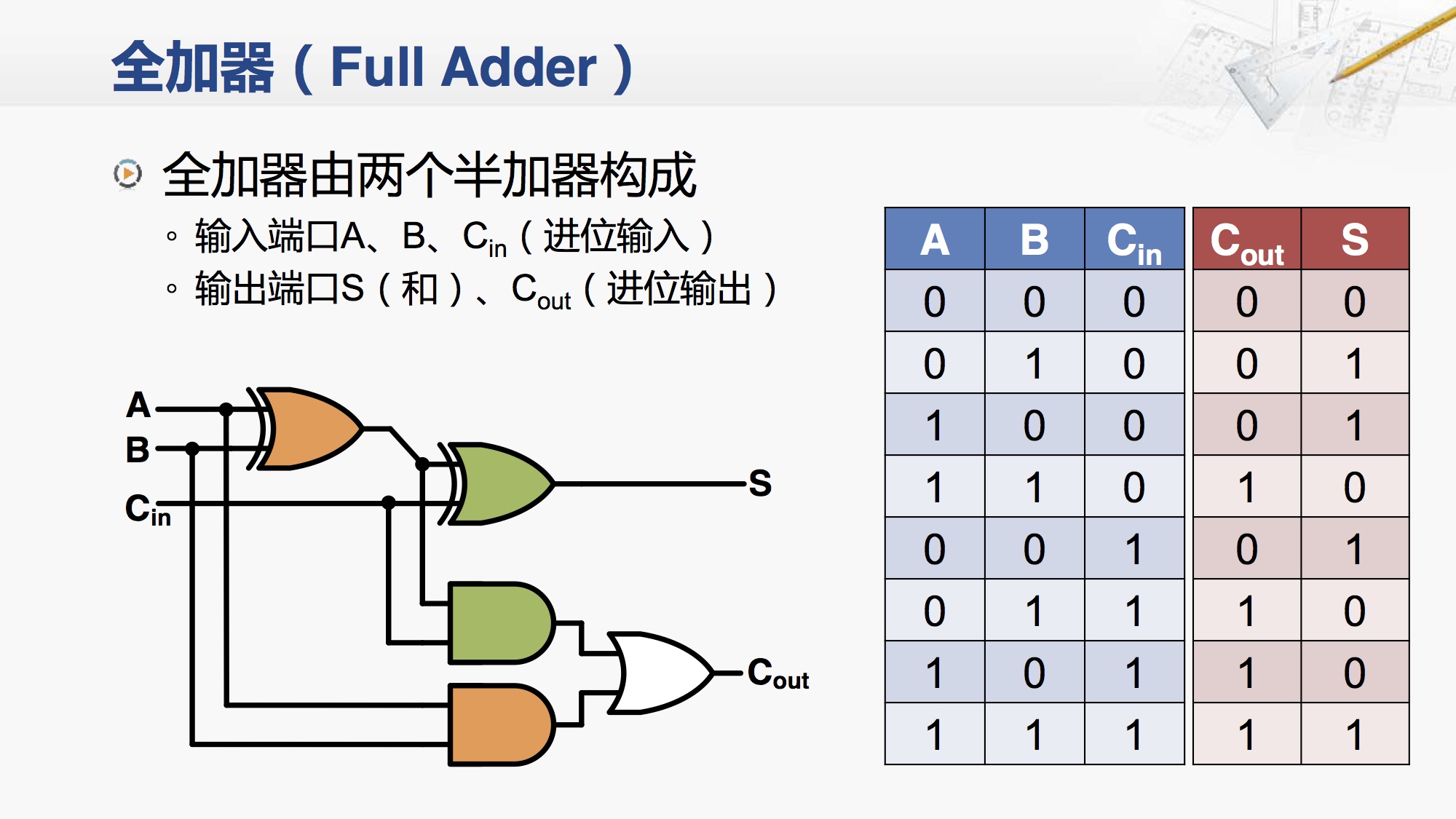

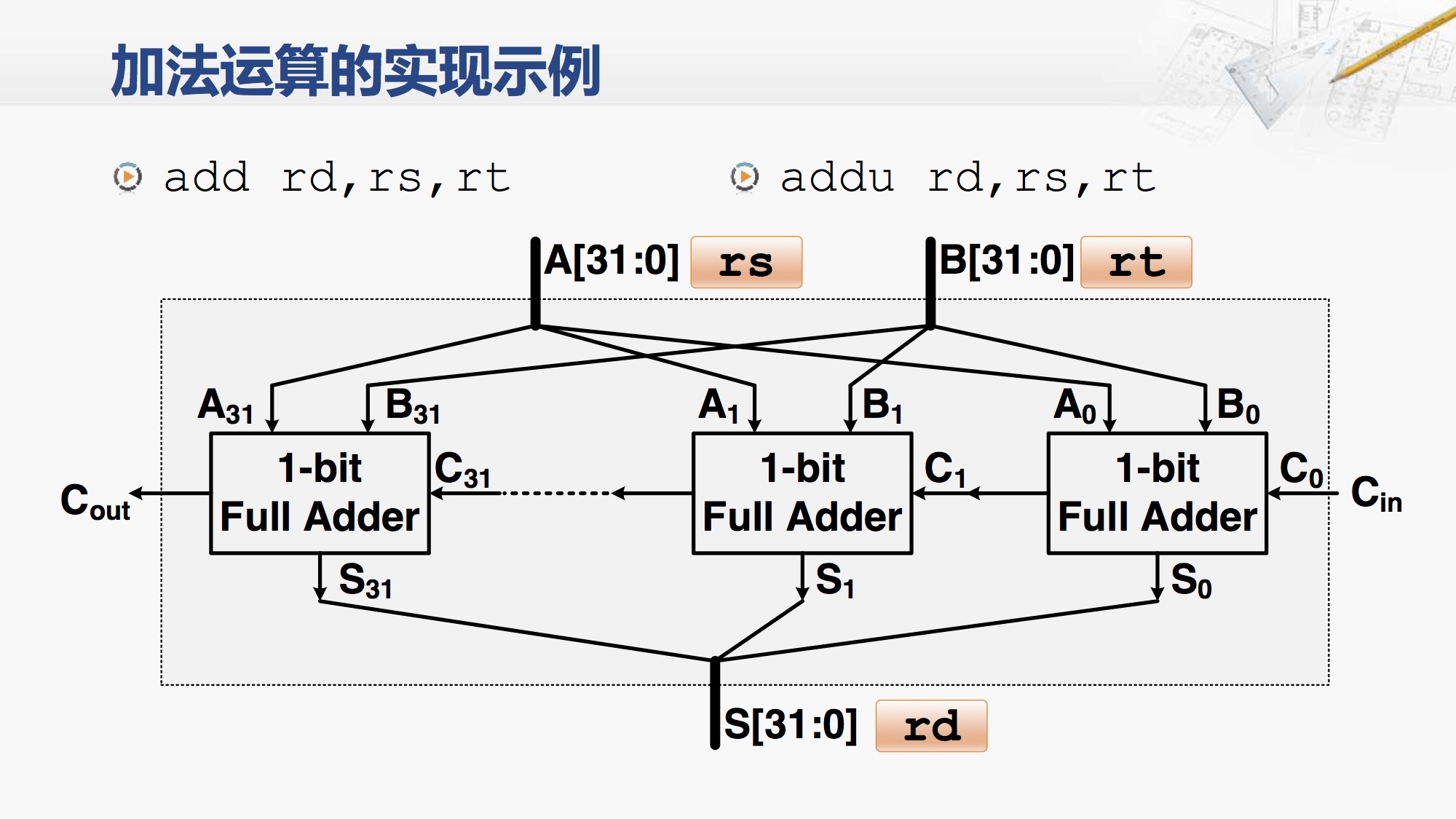

3.1 加法

3.2 溢出

溢出(Overflow):运算结果超出了正常的表示范围

- 仅针对有符号数的运算

- 有溢出时不一定有进位,有进位时也不一定有溢出

- 溢出的检查方法:最高位的进位输入不等于最高位的进位输出

-

处理方式: MIPS提供两类不同的指令分别处理

- 将操作数看做有符号数,发生溢出时产生异常(add,addi)

- 将操作数看做无符号数,不处理溢出(addu,addiu) x86设置溢出标志OF(Overflow Flag)

- 如果把操作数看做有符号数,看运算结果是否发生溢出

- 若发生溢出,则自动设置OF=1;否则,OF=0

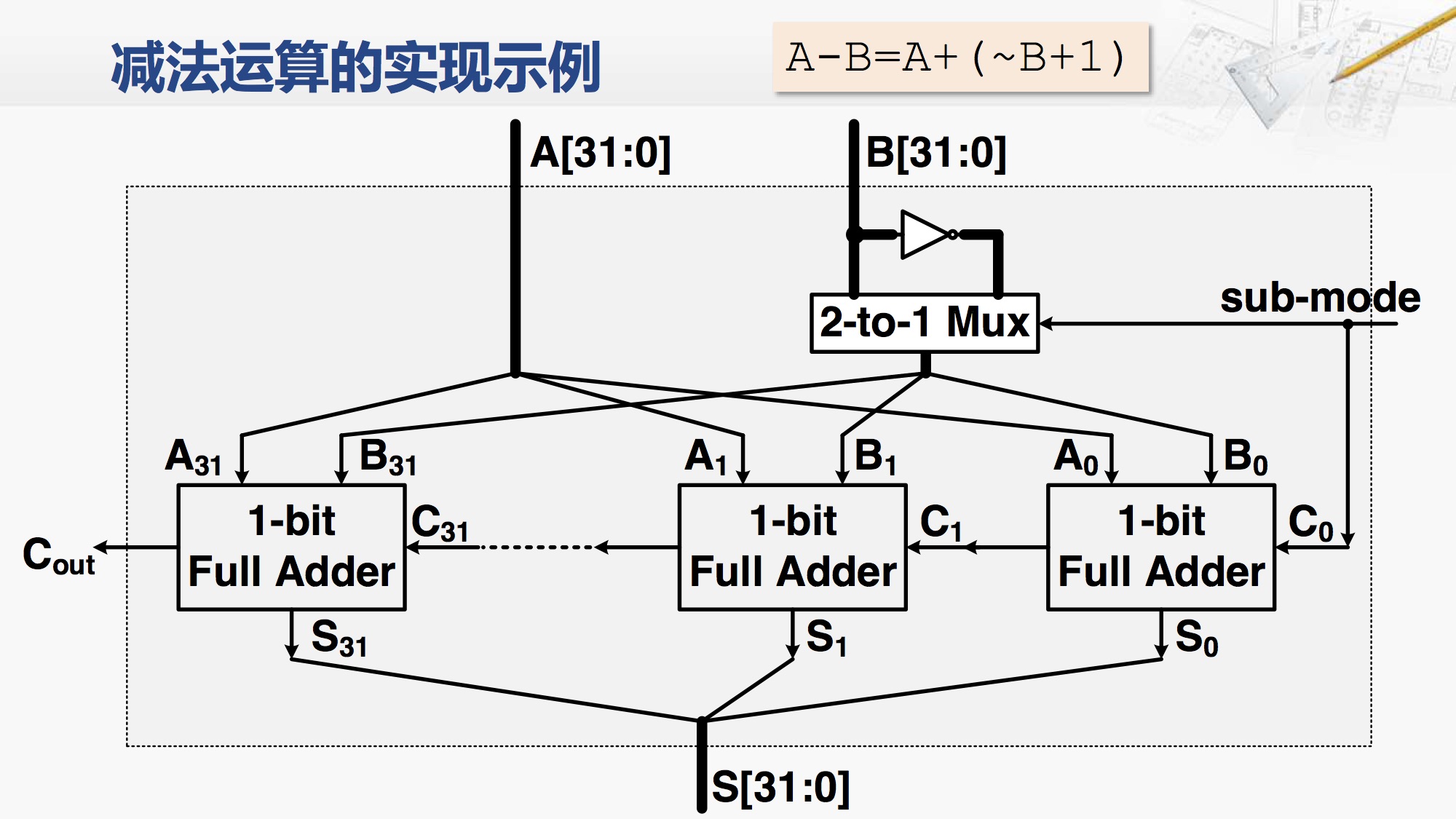

3.3 减法

-

减法运算均可转换为加法运算

- A - B = A + (-B) 补码表示的二进制数的相反数

- 转换规则:按位取反,末位加一 在加法器的基础上实现减法器

- A + (-B) = A + (~B+1)

3.4 加法器的优化

-

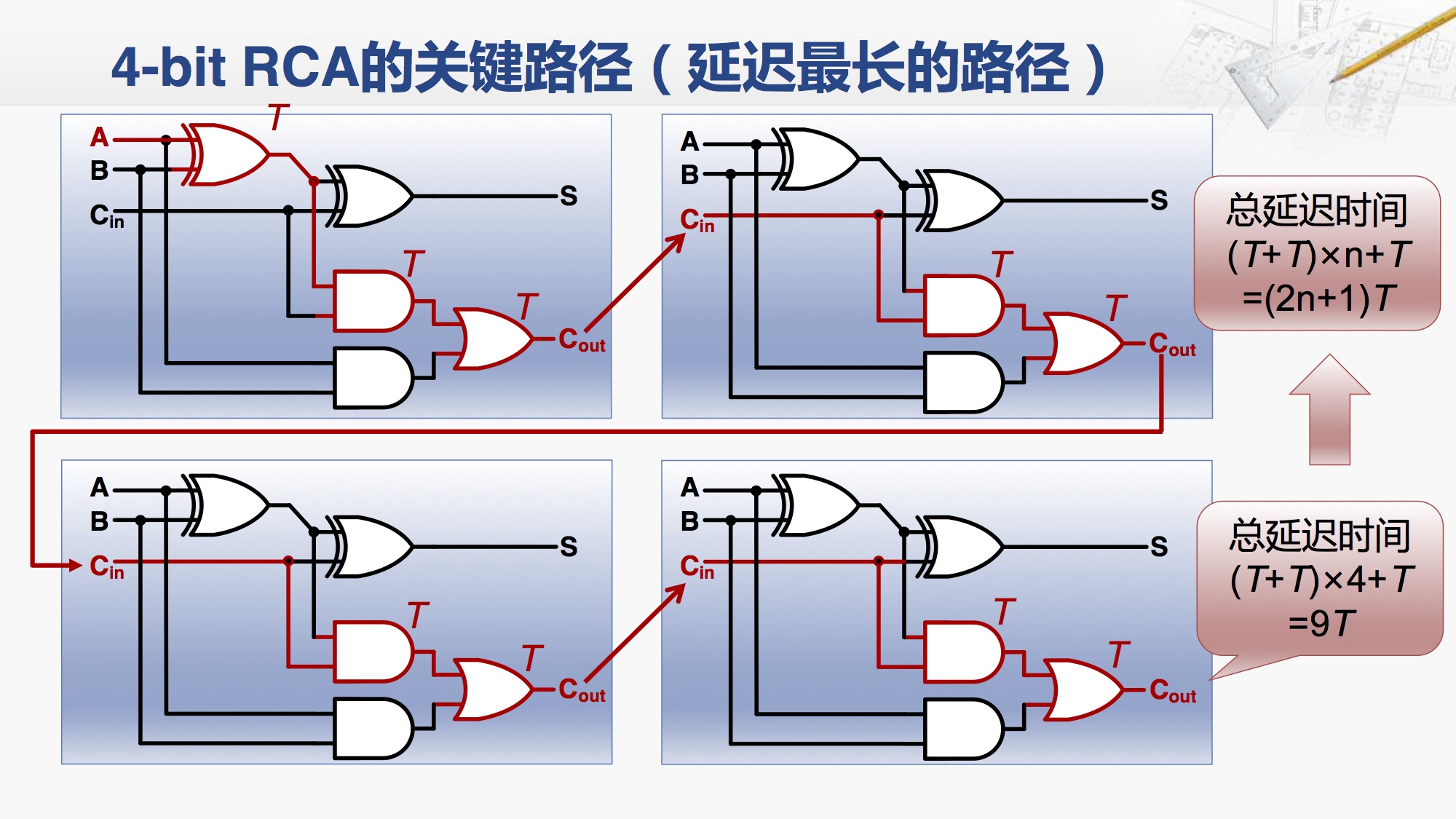

行波进位加法器(Ripple-Carry Adder,RCA) 结构特点

- 低位全加器的 Cout 连接到高一位全加器 Cin 优点

- 电路布局简单,设计方便 缺点

- 高位的运算必须等待低位的运算完成,延迟时间长

优化思路:提前计算出进位输出信号

Ci+1=(Ai⋅Bi)+(Ai⋅

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

543

543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?