目录

一、前言

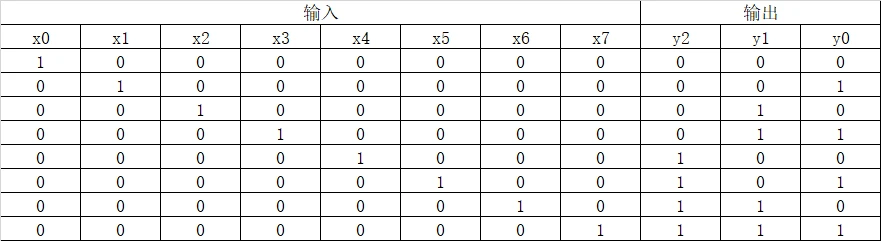

译码器的实现为编码器的逆过程,以3-8译码器为例,真值表如下。

二、工程实现

实现同时使用for循环和case两种方式。

2.1 工程代码

module Decoder(in,out,out_case );

input [2:0] in;

output reg [7:0] out,out_case;

integer i;

always@(in)

begin

for(i=0;i<8;i=i+1)

begin

if(in==i)

out[i]<=1;

else

out[i]<=0;

end

end

always@(in)

begin

case(in)

3'd0: out_case<=8'b0000_0001;

3'd1: out_case<=8'b0000_0010;

3'd2: out_case<=8'b0000_0100;

3'd3: out_case<=8'b0000_1000;

3'd4: out_case<=8'b0001_0000;

3'd5: out_case<=8'b0010_0000;

3'd6: out_case<=8'b0100_0000;

3'd7: out_case<=8'b1000_0000;

default: out<=8'bxxxxxxxx;

endcase

end

endmodule仿真代码

module Decoder_tb( );

reg [2:0] in;

wire [7:0] out,out_case;

initial

begin

in=3'b0;

end

always #5 in=in+1'b1;

Decoder decoder_test(.in(in),.out(out),.out_case(out_case));

endmodule2.2 仿真结果

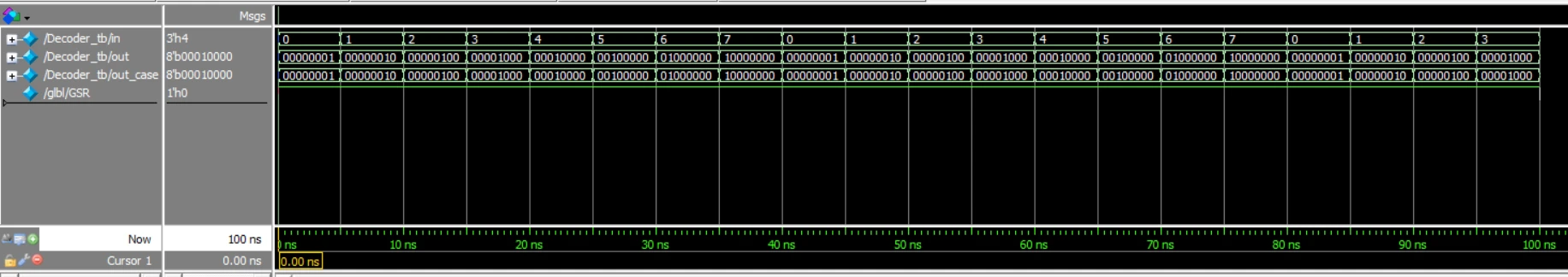

仿真结果如下图,out和out_case输出的结果一致,符合真值表中的逻辑

2.3 参考

《Vivado入门与FPGA设计实例》 4.4 译码器

859

859

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?