September 16, 2016

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52557422

声明:转载请注明作者及出处。

可综合文件放到design文件夹下,testbench文件放到sim文件夹下(文件夹名可自定义)

//ex_module.v

module ex_module(

input wire sclk,

input wire rst_n,

input wire [7:0] d,//声明模块的时候,输入一定是wire变量

output reg [7:0] q//声明模块的时候,输出可以是wire变量也可以是reg;reg变量必须在always块里面赋值

);//接口列表

//异步的D触发器

always @(posedge sclk or negedge rst_n) //括号里面是敏感列表,可以包括电平触发或者沿触发

//寄存器发生变化或翻转就是由CLK(让D触发器翻转)或CLR(复位端让寄存器清零)

if(rst_n == 1'b0) //if后面的括号里是条件表,这里是组合逻辑。"=="声明一个比较器,"1"指的是1比特、"’"用来区分阿拉伯数字和进制,"b"代表的进制binary,“0”是一个比特的0

q<=8'h00; //10'b00000_00000 10'd10 10'hff,沿触发的逻辑里边一定都用<=非阻塞赋值。

else

q<=d;

同步

//always @(posedge sclk)//同步的时候sclk在上升沿的时候,检测到低电平;异步的时候,当rst_n出现下降沿的时候,寄存器复位

// if(rst_n == 1'b0)

// q<=8'h00;

// else

// q<=d;

endmodule//ex_wire.v

module ex_wire(

input wire sel,

input wire a,

input wire b,

output wire c

);//always 对reg赋值,assign语句(连续赋值)对wire赋值

//wire 变量一定用assign连续赋值语句赋值,而且必须是用阻塞赋值

assign c=(sel == 1'b1)?a:b;//(条件)?条件为1:条件为0

/*

if(sel == 1'b1)

c =a;

else

c =b;

*/

endmodule//ex_cnt.v

module ex_cnt(

input wire sclk,//模拟晶振产生时钟震荡

input wire rst_n,//模拟外部复位电平testbench

output wire [9:0] cnt

);

reg [9:0] cnt_r;//定义一个寄存器变量"r"代表reg

always @ (posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

cnt_r <= 10'd0;//"'d0"直接返回32位的0,截取低10位给cnt_r,1023+1=1024

else

cnt_r <= cnt_r + 1'b1;//0---1023-0---1023

assign cnt =cnt_r;

//仿真工具modelsim

//链接:http://pan.baidu.com/s/1qW5IhhM 密码:n28z

endmodule

//请参考verilog数据常量

//数字表达式:<位宽><进制><数字>

//'b:二进制 //eg.4'b1110 表示4位二进制数1110

//'h:十六进制 //eg 8'hef、4’ha等

//'d:十进制 //eg 2'd3、4‘d15(不能写16,4位宽最大15)等

//

//所以10’d0表示10位宽的数值0,0000000000

//加入10‘d15,则表示十进制15 ,0000001111

//tb_ex_cnt.v

//声明延时单位,1ns指的是单位,100ps(0.1ns)指的是时标的精度。

//例如:#10.11--->10.10(最后的10ps精度被忽略)

`timescale 1ns/100ps

module tb_ex_cnt;//这是完整的顶层,没有输入输出接口

reg tb_sclk,tb_rst_n;

wire [9:0] tb_cnt;

initial//一上电只被执行一次,在initial这个块里面只能被寄存器变量赋值

begin//在testbench里面begin、and是顺序执行的;在可综合模块里面begin、and就是一个括号

tb_sclk <=0;

tb_rst_n<=0;//它俩有先后顺序,先是tb_sclk被赋值然后再是tb_rst_n被赋值。但是之间的延迟是0。

#200.1

tb_rst_n<=1;

end

always #10 tb_sclk <= ~tb_sclk;//例如初始状态是0,过了10ns变成1,又保持10ns变成0,周而复始的进行翻转。于是产生了时钟和复位信号

//例化的方法

//原始模块名字 例化的名字(可以自定义)

ex_cnt ex_cnt_inst(

.sclk (tb_sclk),//模拟晶振产生时钟震荡

.rst_n (tb_rst_n),//模拟外部复位电平testbench;例化模块的时候如果原始模块是输入信号,那么括号内可以是wire变量也可以是reg变量

.cnt (tb_cnt) //例化模块的时候如果原始模块是输出信号,那么括号内必须是wire变量(正好和可综合模块相反)

);

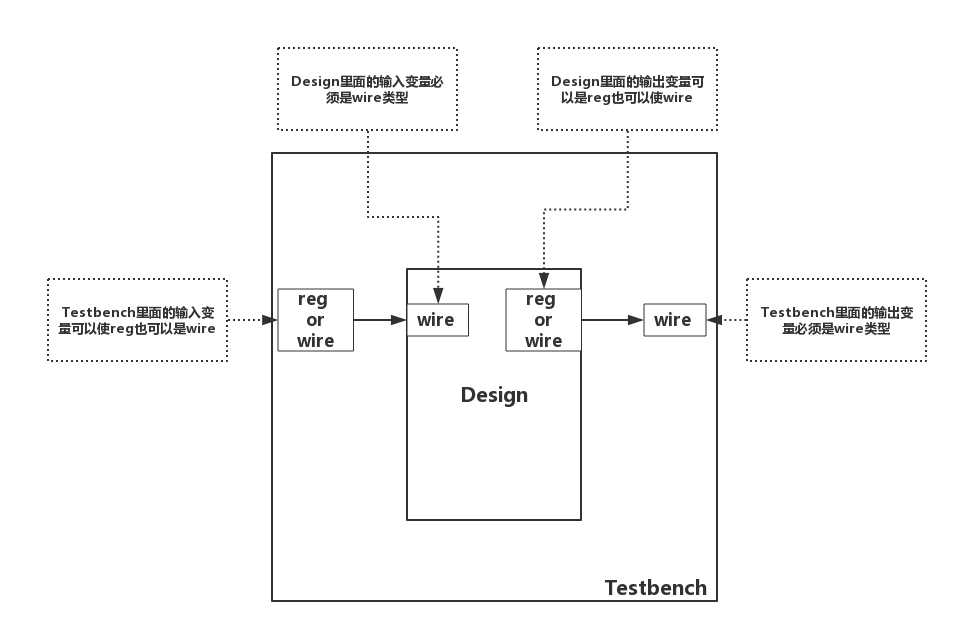

endmodule例化时,变量的赋值应该遵循下图(按照自己理解画的,不一定正确,欢迎指正):

Design中的模块输出的时候可以作为寄存器,它相当于把输出寄存器的Q端直接连接到输出口了,就把中间那根线给省略了;

Testbench中输出变量必须是wire类型,因为芯片画PCB时,输出的管脚都用线连。

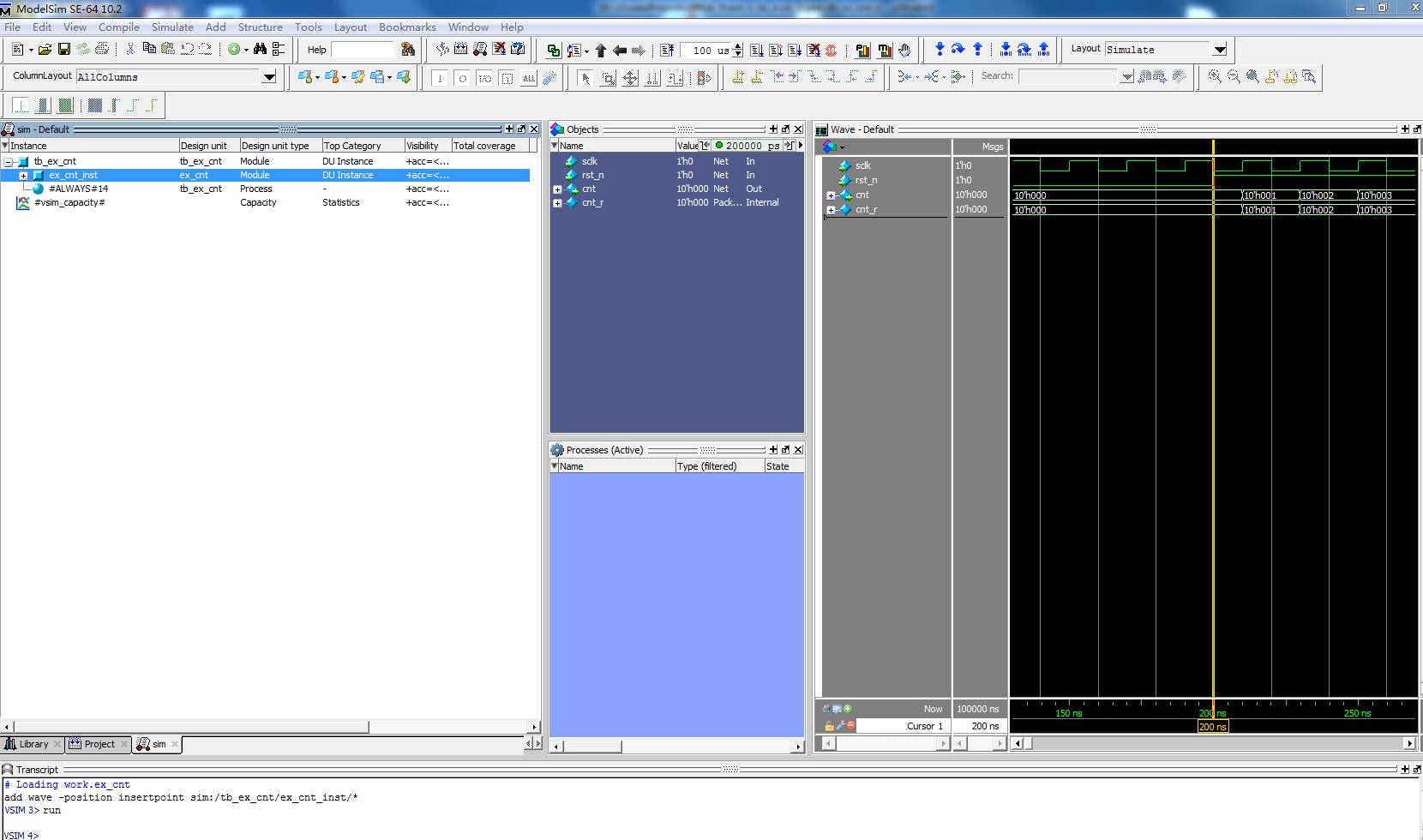

打开ModelSim--->File--->new--->Project--->Project Name:ex_cnt(自定义,别写中文);路径:D:\VivadoProjects\FPGA_From_e_to_c\ex_1\sim(根据你文件的路径写)

--->在Project标签页下右键--->Add to Project--->Existing File--->将ex_cnt.v,tb_ex_cnt.v加进来--->Compile All--->数据编译到Library标签页的work下

--->右键tb_ex_cnt--->Simulation without Optimization--->右键ex_cnt_inst,Add Wave--->

如图所示:

在Wave 页面下,如果左侧信号栏变量名带路径,可以在Tools--->Window Preferences--->Display Signal Path改为1即可。

然后在Wave页面设置运行时间:这里设置100us--->点击Run--->在左侧右击变量--->Radix--->选择显示的进制。

Verilog中wire与reg类型的区别:

http://blog.csdn.net/changhaizhang/article/details/6933806

来源:

https://ke.qq.com/user/index/index.html#cid=66019&term_id=100056181

1024

1024

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?