always语法是Verilog_HDL中最常用的一种语法。 always过程语句和语句块组成的,语法格式如下所示。

always@(敏感信号1 or 敏感信号2.....)

always实现组合逻辑和时序逻辑。用always实现组合逻辑要将所有的敏感信号加入敏感列表中;用always实现时序逻辑时不一定将所有信号添加到敏感列表中。

举例说明:

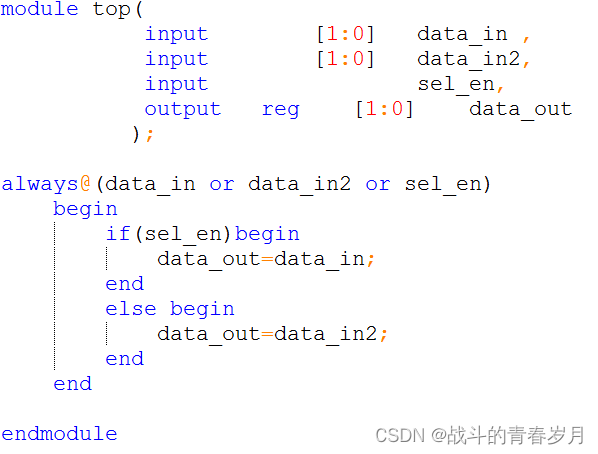

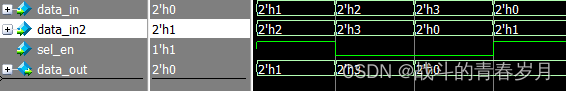

A.always实现组合逻辑

当执行always组合逻辑时,根据sel_en的逻辑值对data_out进行赋值,当sel_en的逻辑值为1时,将data_in的数值赋值给data_out;当sel_en为0时,将data_in2的数值赋值给data_out。

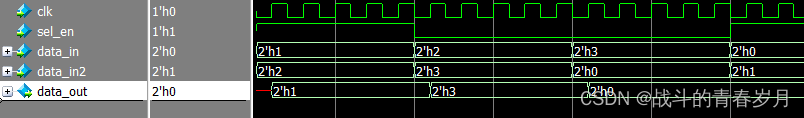

B.always实现时序逻辑

当执行always时序逻辑时,根据sel_en与clk的逻辑值对data_out进行赋值,当sel_en的逻辑值为1同时clk为上升沿时,将data_in的数值赋值给data_out;当sel_en为0同时clk为上升沿时,将data_in2的数值赋值给data_out。

always语法使用注意事项:

- 不要在不同的always块内为同一个变量赋值。即某个信号出现在<=或=左边时,只能在一个always块内。

- 不要在同一个always块内同时使用阻塞赋值(=)和非阻塞赋值(<=)。

- 使用always块描述组合逻辑时使用阻塞赋值(=),在使用always块描述时序逻辑时使用非阻塞赋值(<=)。简单理解可以是,在电平敏感的always块内使用阻塞赋值,在边沿敏感的always块内使用非阻塞赋值。

- 任何在always块内被赋值的变量都必须是寄存器型(reg)。即<=或=左边的信号,必须是reg型,<=或=右边的信号可以是reg型也可以是wire型。

- always的敏感列表中可以同时包括多个电平敏感事件,也可以同时包括多个边沿敏感事件,但不能同时有电平和边沿敏感事件。另外,敏感列表中,同时包括一个信号的上升沿敏感事件和下降沿敏感事件也是不允许的,因为这两个事件可以合并为一个电平事件。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?