概念

SPI, Serial Perripheral Interface, 串行外围设备接口, 是 Motorola 公司推出的一种通信接口技术。

SPI,是一种高速的,全双工,同步串行通信总线,并且在芯片的管脚上只占用四根线(MISO,MOSI,NSS,SCK)。

主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

引脚

SPI接口经常被称为4线串行总线,以主/从方式工作,数据传输过程由主机初始化。4条信号线分别为:

1) SCK:串行时钟,用来控制数据交换的时机和速率,由主机提供;

//serial clock output for masters and input for slaves

2) MOSI:主机输出从机输入数据线;

3) MISO:主机输入从机输出数据线;

4) NSS:从机选择线,低电平有效,由主机控制。

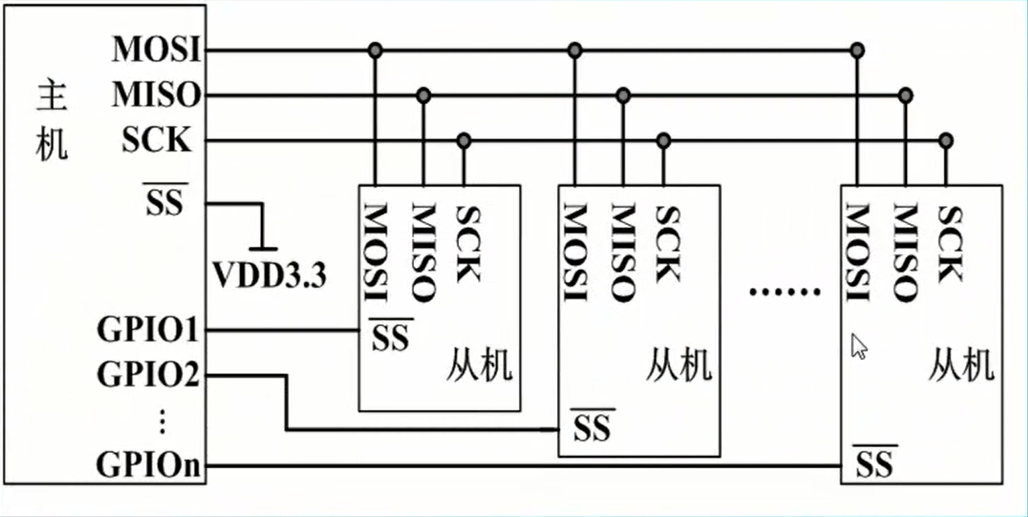

在SPI总线上,某一时刻可以出现多个从机,但只能存在一个主机,主机通过片选线来确定要通信的从机(也就是任何时刻只能有一对主从机在通信)。这就要求从机的MISO口具有三态特性,使得该口线在器件未被选通时表现为高阻抗。

引脚连接

从图中看到,主机的NSS信号为高电平,从机的NSS信号被主机片选。

原理

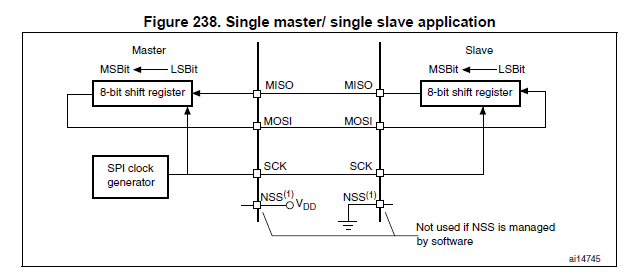

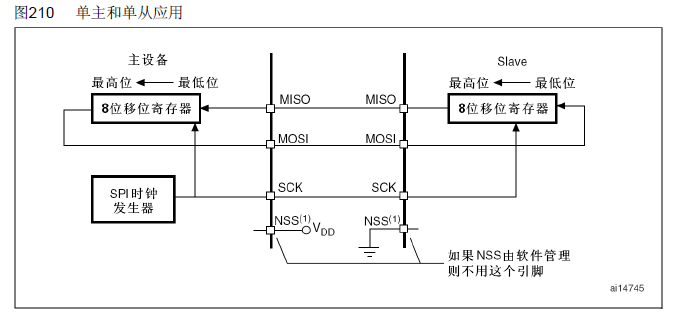

如图:

1.MISO引脚相连接,MOSI引脚相互连接。这样,主从设备

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2392

2392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?