1.1 SPI协议简介

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是一种高速的,全双工,同步的通信总线(SPI相比于IIC具有更高的通信速率)。现在越来越多的芯片集成了SPI通信协议,如FLASH、AD转换器、SD卡(其实就是flash)等。

SPI 通讯协议的优点是支持全双工通信,通讯方式较为简单,且相对数据传输速率较快;缺点是没有指定的流控制,没有应答机制确认数据是否接收。

流控方面:SPI缺乏流控机制,无论主器件还是从器件均不对消息进行确认,主器件无法知道从器件是否繁忙。IIC存在ACK应答信号,所以有流控机制。

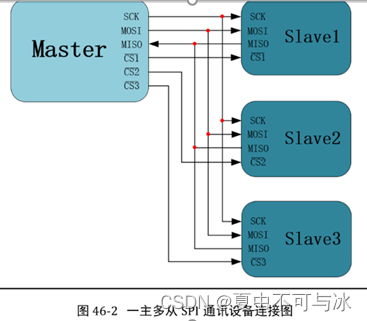

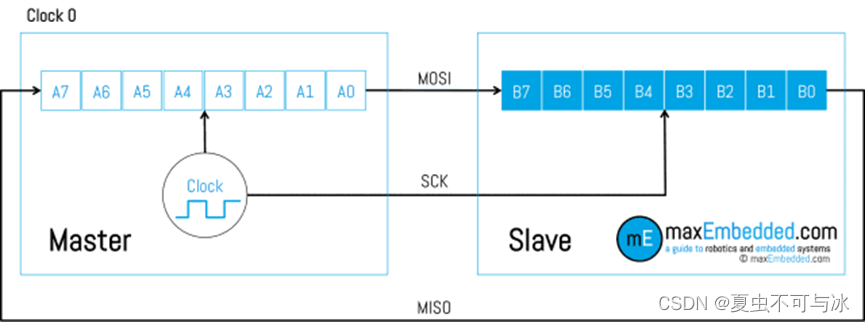

SPI的通信原理比较简单,它以主从方式工作,通常有一个主设备(此处指FPGA)和一个或多个从设备(此处指SD卡)。

一主多从(无论有多少个从设备,都共同使用这 3 条总线;而每个从设备都有独立的这一条 CS_N 信号线,低电平有效)

1.2 CPOL/CPHA 及通讯模式

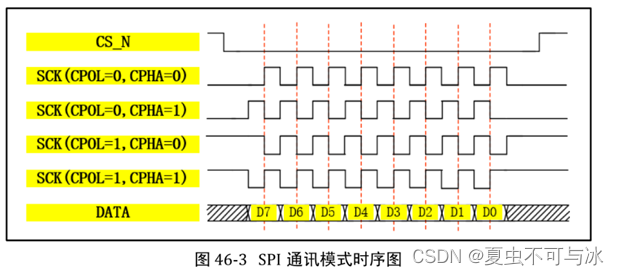

SPI 通讯协议一共有四种通讯模式,模式 0、模式 1、模式 2 以及模式 3,这 4 种模式分别由时钟极性(CPOL,Clock Polarity)和时钟相位(CPHA,Clock Phase)来定义,不同的从设备在出厂时被厂家配置为其中一种模式,模式是不允许用户修改的。

CPOL控制着SPI_CLK的时钟极性,时钟极性变化如下图所示:

模式0:CPOL = 0,CPHA = 0;

模式1:CPOL = 0,CPHA = 1;

模式2:CPOL = 1,CPHA = 0;

模式3:CPOL = 1,CPHA = 1。

由上图可知,当CPOL = 1时,SPI_CLK在空闲时为高电平,发起通信后的第一个时钟沿为下降沿;CPOL = 0时,SPI时钟信号SPI_CLK空闲时为低电平,发起通信后的第一个时钟沿为上升沿。

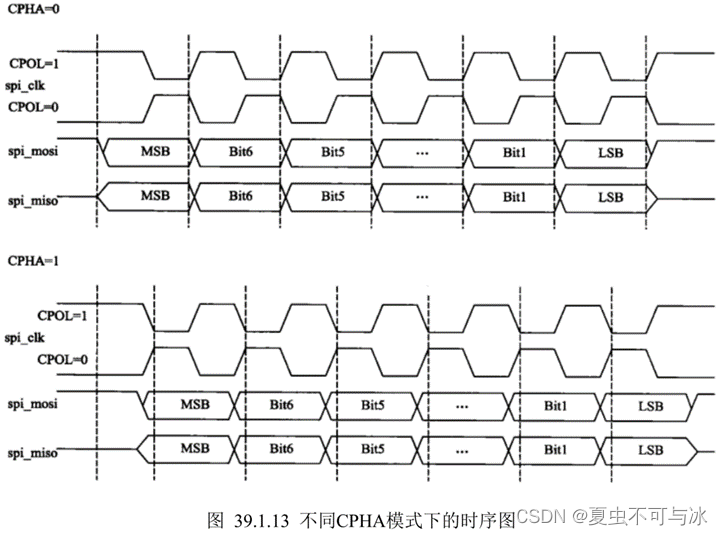

CPHA用于控制数据与时钟的对齐模式,其不同模式下的时序图如下图所示:

由上图可知,当CPHA = 1时,时钟的第一个变化沿(上升沿或者下降沿)数据开始改变,那么也就意味着时钟的第2个变化沿(与第一个变化沿相反)锁存数据;当CPHA = 0时,数据在时钟的第一个变化沿之前就已经改变,并且保持稳定,也就意味着在时钟的第一个变化沿锁存数据。

CPHA = 0,数据采样是在 SCK 时钟的奇数边沿,CPHA = 1,数据采样是在 SCK 时钟的偶数边沿。

1.3 SPI 基本通讯过程

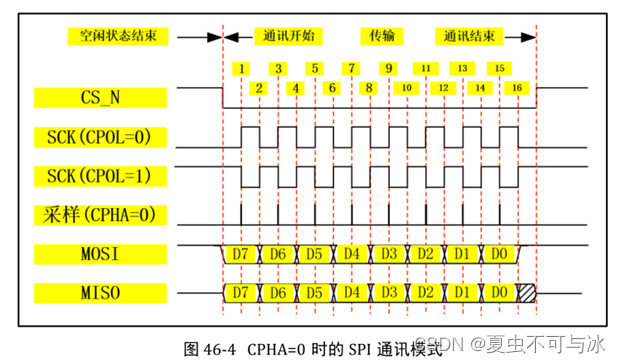

此图表示的是主机视角的通讯时序。SCK、MOSI、CS_N 信号均由主机控制产生,SCK 是时钟信号,用以同步数据,MOSI 是主机输出从机输入信号,主机通过此信号线传输数据给从机,CS_N 为片选信号,用以选定从机设备,低电平有效;而 MISO 的信号由从机产生,主机通过该信号线读取从机的数据。MOSI 与 MISO 的信号只在 CS_N 为低电平的时候才有效,在 SCK 的每个时钟周期 MOSI 和 MISO 传输一位数据。

- 数据传输时,MSB 先行或 LSB 先行并没有作硬性规定,但要保证两个 SPI 通讯设备之间使用同样的协定,一般都会采用MSB先行模式。

- SPI 每次数据传输可以 8 位或 16 位为单位,每次传输的单位数不受限制。

- SPI接口,模式0中,主机只需要负责:1.在奇数沿采集从机输出的数据(从机采集数据由具体的外设来负责,只需确保主机和从机在同一个协议模式下工作即可);2.在偶数沿放置写入从机的数据。

- 主机数据MOSI写入从机的同时,也会从 从机中读出数据MOSI。

参考文献:

1.征途Pro《FPGA Verilog开发实战指南——基于Altera EP4CE10》

2.《开拓者FPGA开发指南》

12万+

12万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?