本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM(OCM)和使用DDR3两种情况

JTAG方式

JTAG方式是调试中最常用的方式,在SDK中

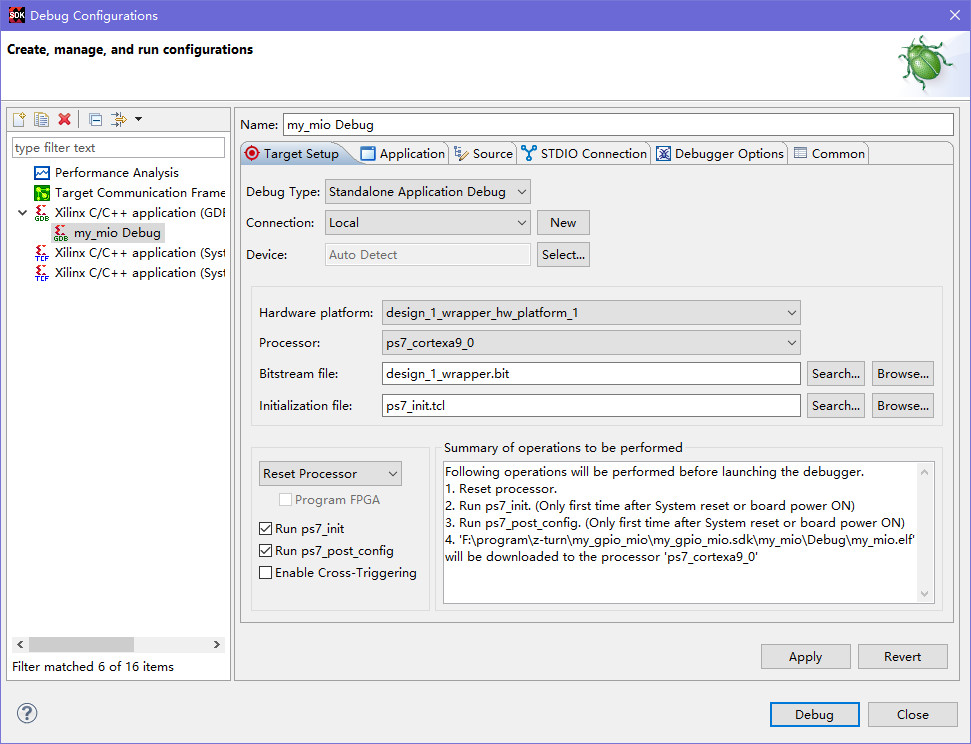

- 在“Project Explorer”窗口工程上右键->Debug As->Debug Configurations可以看到以下窗口

- 首次打开左边窗口中Xilinx C/C++ application(GDB)下没有子项,这时双击Xilinx C/C++ application(GDB)即可新建一个调试;

- 这时右边窗口会自动填充如上图,若没有则手动填入;

- 在右边Application窗口指定要下载调试的.elf文件;

- 在右边STDIO Connection可以指定标准输入输出串口,即printf打印串口,若这里选择开发板上uart的com口,则调试时printf的信息打印到调试时Console窗口,同时也可从Console窗口输入数据,以此将数据通过串口发送到开发板上

- 以上设置完成后点击Debug即可开始调试;

- 若以上在“Project Explorer”窗口工程上右键->Run As->Run Configurations;配置与此类似,最后点击run即可开始运行,只是不是调试而是直接上板运行。

只用OCM

只用OCM指不使用DDR3的方式,与使用DDR3的方式略有不同。这

本文详细介绍了Zynq芯片的三种启动方式:JTAG、从SD卡启动和从QSPI启动。内容涵盖启动文件的生成、设置以及注意事项,包括在不使用DDR3情况下直接利用OCM启动的方法。对于每种启动方式,文章提供了具体的操作步骤和关键配置,以帮助读者理解和实现Zynq的多种启动模式。

本文详细介绍了Zynq芯片的三种启动方式:JTAG、从SD卡启动和从QSPI启动。内容涵盖启动文件的生成、设置以及注意事项,包括在不使用DDR3情况下直接利用OCM启动的方法。对于每种启动方式,文章提供了具体的操作步骤和关键配置,以帮助读者理解和实现Zynq的多种启动模式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7398

7398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?