这几天对于verlog里面reg变量赋值,导致数据delay的情况十分混论,这里理一理;

首先单独一个reg型变量在always块中,进行常数赋值或者自赋值,显然不会产生delay

always@( posedge clk or negedge rst_n )

begin

if( !rst_n )begin

count_reg <= 0;

end

else

if( count_reg < 255 )

begin

count_reg <= count_reg + 1; //实测这种模式已经存在一个时钟的延时了,不

end

end这个count_reg在仿真的时候不会产生delay。

而如果在一个时钟沿上级联两个寄存器,那么这种后一个寄存器会出现一拍的延时。如下图:

always@( posedge clk or negedge rst_n )

begin

if( !rst_n )begin

count_reg <= 0;

end

else

if( count_reg < 255 )

begin

count_reg <= count_reg + 1; //实测这种模式已经存在一个时钟的延时了,不

end

end

always@( posedge clk or negedge rst_n )

begin

if( !rst_n )

count <= 0;

else

count <= count_reg;

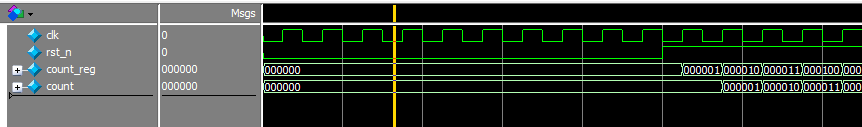

end 仿真效果如下

可以看到count是较count_reg延时了一拍的.

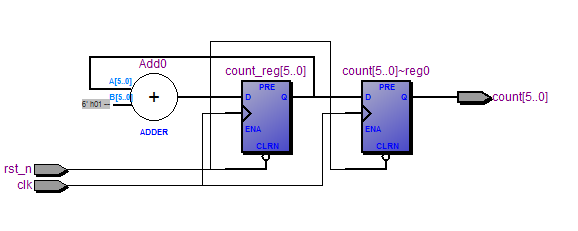

综合出的电路图如下:

可以看到count 与count_reg是级联的。count比count_reg延时一拍

但是注意到下面这种情况

always@( posedge clk or negedge rst_n )

begin

if( !rst_n )begin

count_reg <= 0;

count <= 0;

end

else

if( count_reg < 255 )

begin

count_reg <= count_reg + 1; //实测这种模式已经存在一个时钟的延时了,不

count <= count_reg;

end

end综合出的电路,以及时序都跟上面一样,会顺延一拍。

总结的规律是:当一组级联的寄存器级联串起来,当第一级寄存器变化的时候,最后的输出要延时几个周期才能输出,延时的周期数跟级数的差值相同。

一个寄存器和另一个寄存器级联,除非要求第一级寄存器和第二级寄存器在同一个时钟沿同时变化,否则不会出现延时的情况。

8929

8929

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?