今天讨论有关PCB布局技术的问题,着重于以 PCB的布线原则来降低发射体杂讯的强度与提升电路对杂讯的免疫能力。欢迎各位来跟我探讨,我们实验室有专业的电磁兼容设备认证检测整改一站式158-89142-030

1、元件的放置

PCB 布局之前应先注意将元件放置(placement)在适当的位置,一方面需考虑电路板外部接线端子的位置,另一方面也需考虑不同性质的电路应予以适当的区隔。

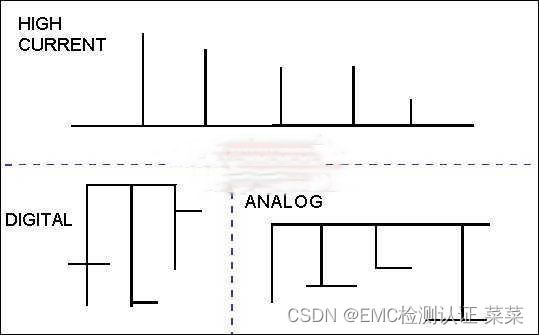

低阶类比、高速数位以及杂讯电路(继电器、高电流开关等等) 应加以分隔以降低子系统间的耦合。当放置元件时,应同时考虑子系统电路间的内部电路绕线,特别是时序及震荡电路。为了去除EMI的潜在问题,应该系统化的检查元件放置与线路布局,返覆检视及修正布线一直到确定所有的 EMI风险降低到最低为止,简而言之,事先的防范是将低EMI干扰问题的首要原则。下图说明不同性质电路的区隔概念。

将PCB上不同性质的电路予以隔离

2、接地的布局

一个电子设备的设计关键即在于具有强韧的与可靠的电源系统,而接地布局尤为其中关键。

事实上,接地可视为所有好的PCB设计的基础。大部分的EMI问题皆可藉由良好的接地来解决。

3、接地噪声的定义

降低地线杂讯对系统影响的关键在于了解产生接地杂讯的机制。接地杂讯的主要关键在于所有的地线都有些微的阻抗,对所有的电路而言,电流都必须流经地线,那些有限的接地阻抗电就会在地线上产生压降,这些压降则会耦合到相关的电路而形成杂讯。

由于传输线具有电感性(杂散电感),因此线上的瞬间突波电流(surge current),将引发极大的脉冲电压。电感的端电压与其流过之电流有下列关系:

高频率数位系统当电晶体开关时曾产生突波电流;类比系统则在负载电流改变时产生瞬间的电流变化。举例来说,一个闸在"ON"而载有4 mA的电流时,突然开关切到"OFF"且现在载有0.6 mA的电流,假设开关时间为4 msec,载有450 mH的电感信号的导体,此时所产生的电压突波为:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

392

392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?