以下是rtl代码

module shift(

input clk, // 鏃堕挓淇″彿

input [2:0] MD, // 妯″紡閫夋嫨

input model,

input rstn, // 澶嶄綅

output [7:0] QB // 值杈撳嚭鍊?

);

reg cnt = 0; // 璁℃暟鍣?

reg clk_out; // 鍐呴儴鏃堕挓淇″彿

reg [7:0] REG; // 8浣嶅瘎瀛樺櫒

reg [24:0] count; // 璁℃暟鍊?

reg cnt_flag; // 璁℃暟鏍囧織

always @(posedge clk) begin

if (!rstn) begin

count <= 1'b0; // 澶嶄綅鏃跺皢璁℃暟鍣?count 缃浂

end

else if (cnt == 50) begin

count <= 1'b0; // 褰?cnt 杈惧埌 50000000 鏃跺皢璁℃暟鍣?count 缃浂

end

else begin

count <= count + 1'b1; // 姣忎釜鏃堕挓鍛ㄦ湡璁℃暟鍣?count 鍔?1

end

end

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt_flag <= 1'b0; // 澶嶄綅鏃跺皢璁℃暟鏍囧織 cnt_flag 缃浂

end

else if (count == (50 - 1)) begin

cnt_flag <= 1'b1; // 褰?count 杈惧埌 4999999 鏃跺皢璁℃暟鏍囧織 cnt_flag 缃负 1

end

else begin

cnt_flag <= 1'b0; // 鍏朵粬鎯呭喌涓嬭鏁版爣蹇?cnt_flag 缃浂

end

end

// always @(posedge clk) begin

// if (count == 5000000-1) begin

// count <= 0;

// clk_out <= ~clk_out; // 时 藕 取

// end

// else

// count <= count + 1;

//end

always @(posedge clk) begin

if (model == 0 && cnt == 0 && cnt_flag==1) begin

REG = 8'b11111110; // 鍒濆鍖栧瘎瀛樺櫒鐨勫€贾?

cnt = 1; // 灏嗚鏁板櫒缃负1

end

else if (model == 1 && cnt == 1 && cnt_flag==1) begin

REG = 8'b11101110; // 鏇存柊瀵勫瓨鍣ㄧ殑鍊?

cnt = 2; // 灏嗚鏁板櫒缃负2

end

else if(cnt_flag==1) begin

case (model)

1'b0: begin

case (MD)

3'b000: begin

REG[0] <= REG[7]; // 妯″紡0 寰幆宸︾Щ

REG[7:1] <= REG[6:0];

end

3'b001: begin

REG[7] <= REG[0]; // 妯″紡1 寰幆鍙崇Щ

REG[6:0] <= REG[7:1];

end

3'b010: begin

REG[1:0] <= REG[7:6]; // 妯″紡2 寰幆宸︿袱绉?

REG[7:2] <= REG[5:0];

end

3'b011: begin

REG[7:6] <= REG[1:0]; // 妯″紡3 寰幆鍙充袱绉?

REG[5:0] <= REG[7:2];

end

endcase

end

1'b1: begin

case (MD)

3'b100: begin

REG <= {REG[6:4], REG[7], REG[2:0], REG[3]}; // 妯″紡4 闈炲惊鐜乏绉?

end

3'b101: begin

REG <= {REG[4], REG[7:5], REG[0],REG[3:1]}; //妯″紡5 闈炲惊鐜彸绉?

end

3'b110: begin

REG[4] <= REG[6]; //妯″紡6 闈炲惊鐜乏涓ょЩ

REG[5] <= REG[7];

REG[7:6] <= REG[5:4];

REG[0] <= REG[2];

REG[1] <= REG[3];

REG[3:2] <= REG[1:0];

end

3'b111: begin

REG[6] <= REG[4]; // 妯″紡7 闈炲惊鐜彸涓ょЩ

REG[7] <= REG[5];

REG[5:4] <= REG[7:6];

REG[2] <= REG[0];

REG[3] <= REG[1];

REG[1:0] <= REG[3:2];

end

endcase

end

endcase

end

end

assign QB[7:0] = REG[7:0]; // 杈撳嚭瀵勫瓨鍣ㄧ殑鍊?

endmodule

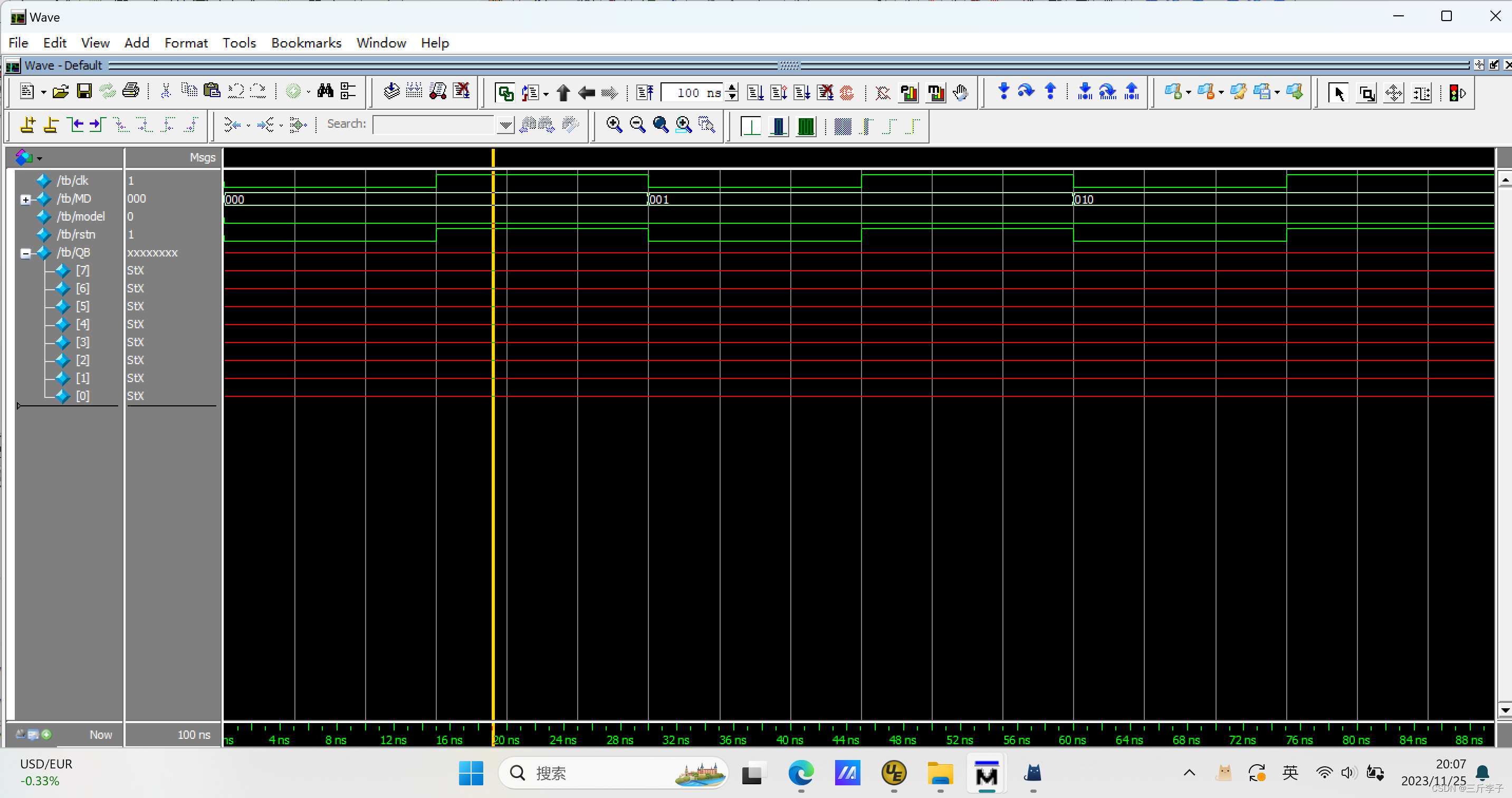

下面是testbeach

`timescale 1 ns / 1 ns

module tb;

reg clk;

reg [2:0] MD;

reg model;

reg rstn;

wire [7:0] QB;

initial begin

clk = 1'b0; //初始时钟为0

rstn = 1'b0;

model = 0;

MD = 3'b000;

#30;

model = 0;

MD = 3'b001;

#30;

model = 0;

MD = 3'b010;

#30;

model = 0;

MD = 3'b011;

#30;

model = 1;

MD = 3'b110;

#30;

model = 1;

MD = 3'b111;

#30;

end

always #15 clk = ~clk;

always #15 rstn = ~rstn;

shift dut

(

.clk (clk),

.MD (MD),

.model (model),

.QB (QB),

.rstn (rstn)

);

endmodule

大佬求解

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?