前言

在FPGA学习中常用到modelsim进行仿真,该贴用来记录我在modelsim仿真中出现红色线条出现的原因及解决方法,同时总结已有的网上的出现该现象的例子modelsim

检查

首先modelsim中出现红色线条,表示不确定状态,常与testbench文件的编写有关。

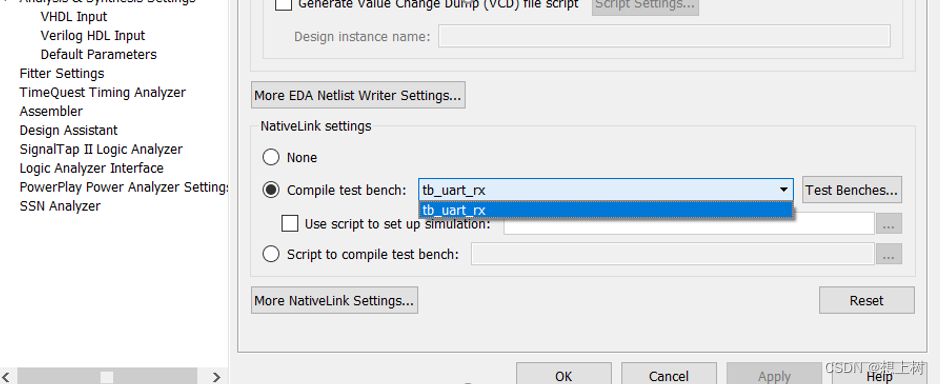

1.可以先检查一下仿真设置,确定仿真文件是否选择正确 此处仿真文件选择错误,可能导致输入设置不对,状态不确定,出现红线

此处仿真文件选择错误,可能导致输入设置不对,状态不确定,出现红线

2.可以检查仿真文件`timescale指令是否正确,就我自己有次忘写后并没出现什么问题,也没有出现红线,但不能确定跟这个没关系,因为看网上其他说法有说到可能是这个指令导致的问题

3.仔细检查initial语句是否赋值正确,clk信号是否有准确赋值,变量位宽是否保持一致。很大概率问题就出现在此,极有可能没写赋值或没写准确导致状态不定

4.检查是否使用case语句,使用case语句不要用<=进行赋值

我的错误经历(TAT)

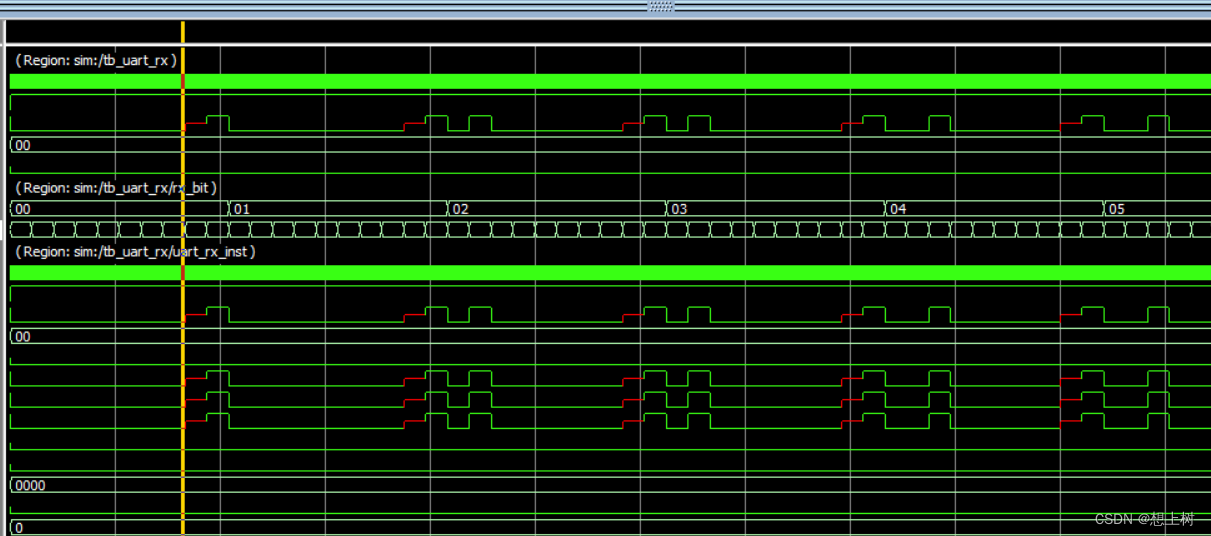

1.不严谨的赋值导致data[0]成了不定态,波形表现得很规则o(TヘTo),很有规律的出现了不定态

本文详细描述了在modelsimFPGA仿真中遇到红色线条(不确定状态)的原因,包括仿真设置错误、timescale指令、initial语句、case语句赋值和时钟信号配置,通过作者的亲身经历给出了具体案例和解决方法。

本文详细描述了在modelsimFPGA仿真中遇到红色线条(不确定状态)的原因,包括仿真设置错误、timescale指令、initial语句、case语句赋值和时钟信号配置,通过作者的亲身经历给出了具体案例和解决方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1034

1034

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?