在进行印刷电路板(PCB)的信号完整性(SI)仿真分析时,一个重要设计参数是介电材料的相对介电常数(εr),也称为介电常数(Dk),最好的来源是PCB供应商的数据表。

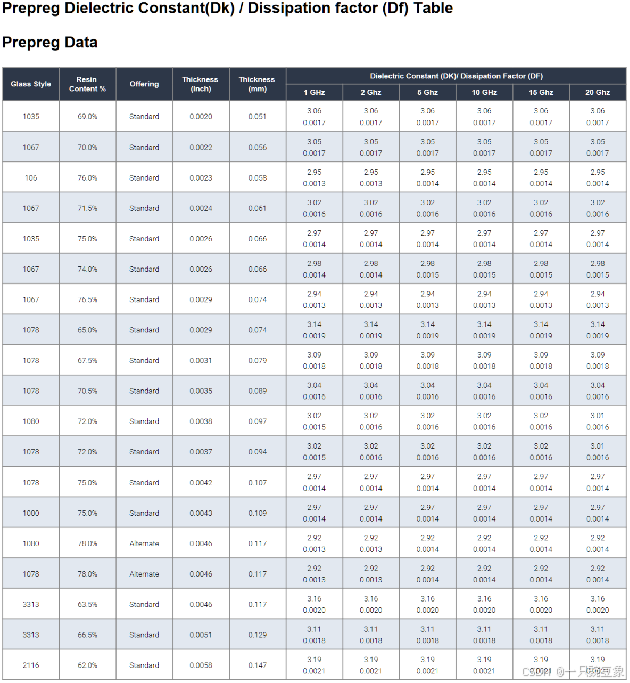

虽然这些参数很容易在供应商的网站上获取,但是,数据表并不能代表设计实际堆叠或进行阻抗和SI损耗建模所需的内容。这是因为,根据玻璃类型、树脂含量、厚度、Dk和耗散系数(Df)的不同,同一层压板的不同芯和预浸料厚度会有所不同。数据表通常只报告50%树脂含量和两个或三个频率点的典型Dk/Df,未指定厚度。此外,Dk和Df在频率上不是恒定的。因此,使用这些数据表中的数字将导致不准确的阻抗和相位延迟结果。

相反,如下图所示,更为真实的Dk/Df表应当提供了不同玻璃编制密度在不同频率下的实际芯材和预浸料厚度、树脂含量和Dk/Df,并且,每个厚度都有不同的Dk值。

许多工程师认为Dk是材料的固有属性,但实际上,它是通过特定的行业标准测试方法测量的有效Dk (Dkeff)。当它们与设计应用中的实际测量值进行比较时,由于金属表面粗糙度引起的相位延迟增加,Dkeff通常存在差异。

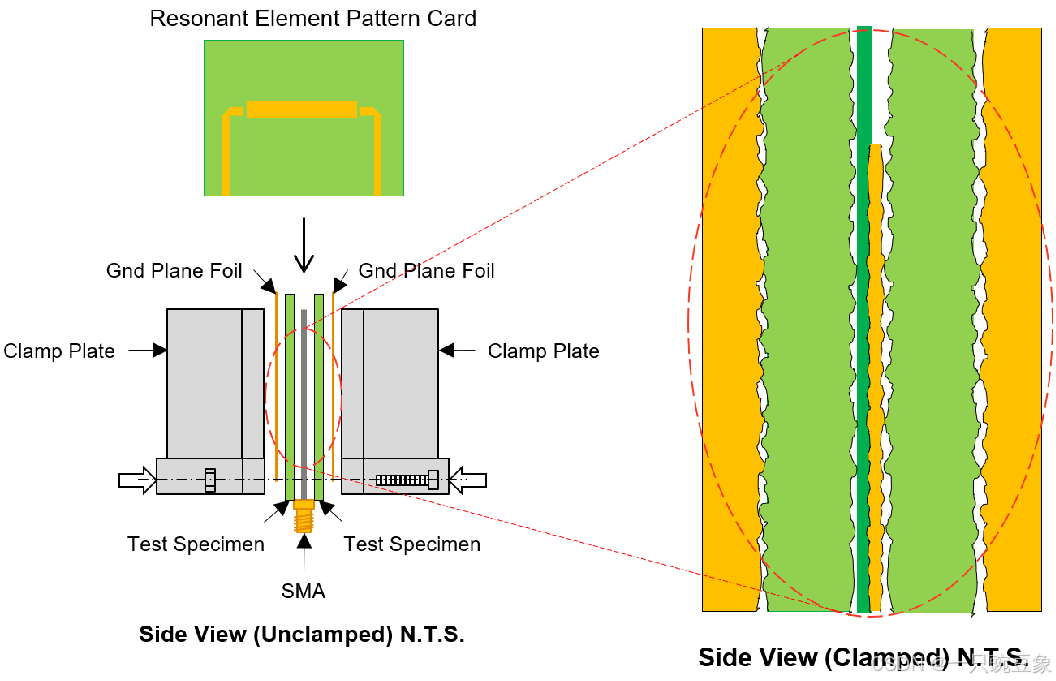

Dkeff高度依赖于测试设备和测量条件。许多PCB供应商通常使用的一种方法是钳位带状线谐振器测试方法,如IPC - TM -650 2.5.5.5, Rev C 测试标准所述。

由于所有的层压板都是各向异性的,任何基于带状线的测试方法,都会报告电场与信号传播横向的Dk值,即如果信号在x-y轴方向传播,则该方法测得的Dk为电场在z轴方向时的Dk。

如图所示,Dk值采用TM-650 2.5.5.5试验法测定。测量是在带状线条件下使用精心设计的谐振元件模式卡( Resonant Element Pattern Card)完成的,卡被夹在两层未包覆的被测介质材料(Test Specimen)之间,然后,整个结构被夹在两块大板(Clamp Plate)之间,并用内衬铜箔接地(Gnd Plane Foil)作为带状线的参考平面。

这种测试方法虽然可以保证测试的稳定性和一致性,但是,依然存在一定的缺陷:由于谐振元件模式卡和被测材料没有物理地粘合在一起,由于铜箔板的表面粗糙度,小的气隙依然存在,这个因素也是造成仿真和测量之间有效Dk和相位延迟差异的主要原因。

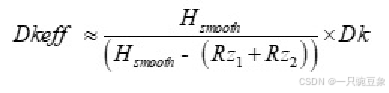

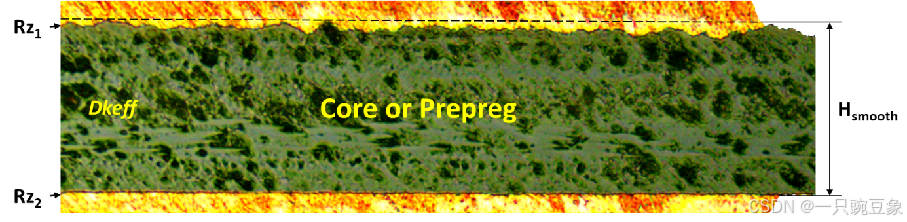

如图所示,Rz1和Rz2是来自供应商数据表的介质两侧铜箔(Copper Foil)的导体粗糙度,通常,Rz是由机械轮廓仪测量的10点平均粗糙度,Hsmooth是来自供应商数据表的层压介质厚度,此时,Dkeff就可以表示为:

式中,Dk为介电常数,来自供应商的Dk/Df表数据表。

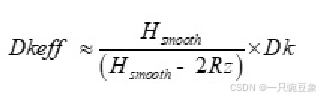

当相同粗糙度的铜箔被同时使用时,上式可以简化为:

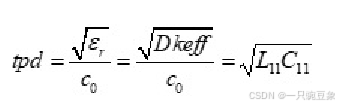

另外一种方法,由S21的相位或时延(TD)得出的Dkeff随频率变化图,计算公式如下:

![]()

该方法与前述的IPC-TM-650测试方法存在明显不同,并不依赖于测试台架的影响。

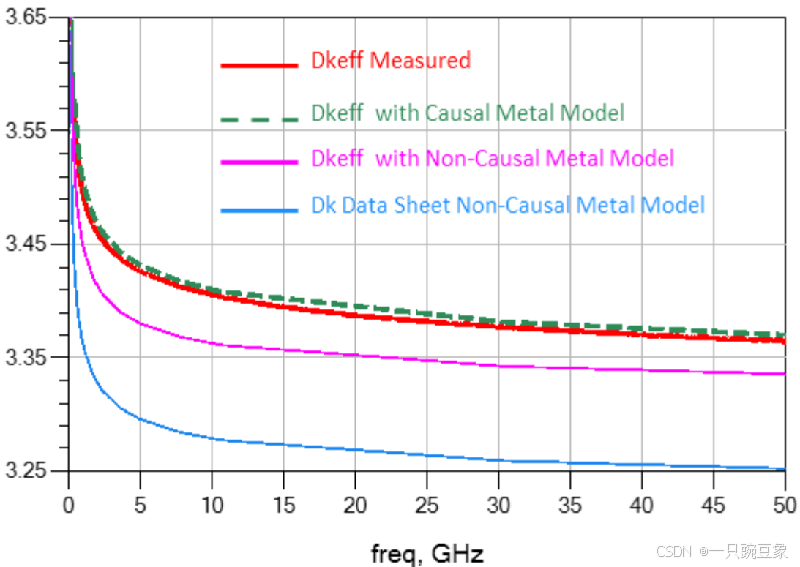

红色图是实际测量的Dkeff;粉色图是使用经粗糙度值公式校正后的Dkeff;蓝色图是使用Dk/Df表中公布的12 GHz Dk,再经S21时延TD的模拟计算Dkeff;绿色图是采用因果Huray-Bracken粗糙度模型的仿真Dkeff。

粉色图和红色图之间的差异是因为粗糙度公式中的Dkeff只校正了由于传输线单位长度的自电容(C11)引起的相位延迟,但是,实际铜箔的粗糙度也增加了传输线单位长度的自感(L11),这增加了额外的相位或时间延迟。

单个传输线的传播延迟(tpd)可以表示为:

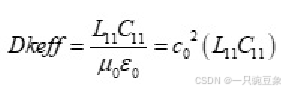

经改写,Dkeff最终可以表示为:

该式可以清楚地表明,随着自感的增加,Dkeff将成比例地增加。这意味着对于PCB传输线,通过S21的相位或时延(TD)得出的Dkeff不能被认为与介电材料的相对介电常数(εr)相同,这也是蓝色图和红色图差异之所在。

当场解算器通过对金属复杂阻抗的虚部施加粗糙度校正因子来适当地校正自感时,则模型是因果的,因此,只有当与粗糙度的校正Dkeff相结合时,才能看到自感的增加,与测试结果相比,展现出很好的一致性,如图中虚线绿色图所示。

最后,总结如下:

- 许多层压板供应商提供的Dk/Df表来源于箝位带状线谐振器测试方法,但是,这些数字并没有考虑到铜箔的实际粗糙度。当需要考虑基于层压厚度和铜箔粗糙度的Rz校正因子时,可以使用更精确的Dkeff值以及因果粗糙度模型(比如,Huray-Bracken roughness model)来进行传输线建模。

- 对于PCB传输线,用相位或时延测量方法计算Dkeff不能保证是真实的介质材料的相对介电常数,因此,使用此值将导致不准确的模拟结果。

本文翻译整理自:

May | 2022 | Bert Simonovich's Design Notes

扩展阅读

[1] 有效Dk值提取方法的仿真分析_等效dk怎么提取-CSDN博客

[2] 金属表面粗糙度对信号的影响_hammerstad-CSDN博客

[3] 【知识分享】PCB叠层材料各向异性对高速通孔建模的影响-CSDN博客

1074

1074

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?