1、 3-8译码器相关实验

1.1Verilog 3-8译码器

代码编写及生成的RTL视图

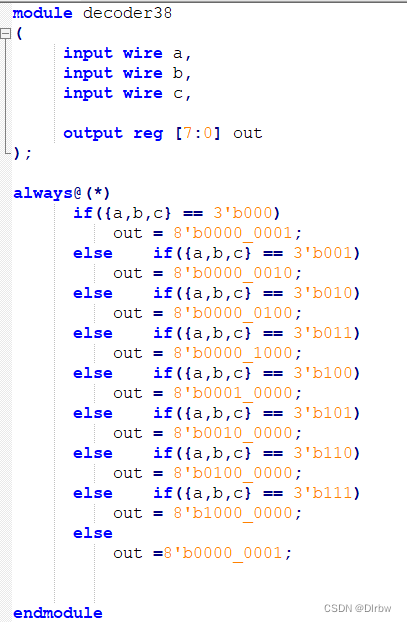

(1)always中if-case实现方法

生成的RTL视图

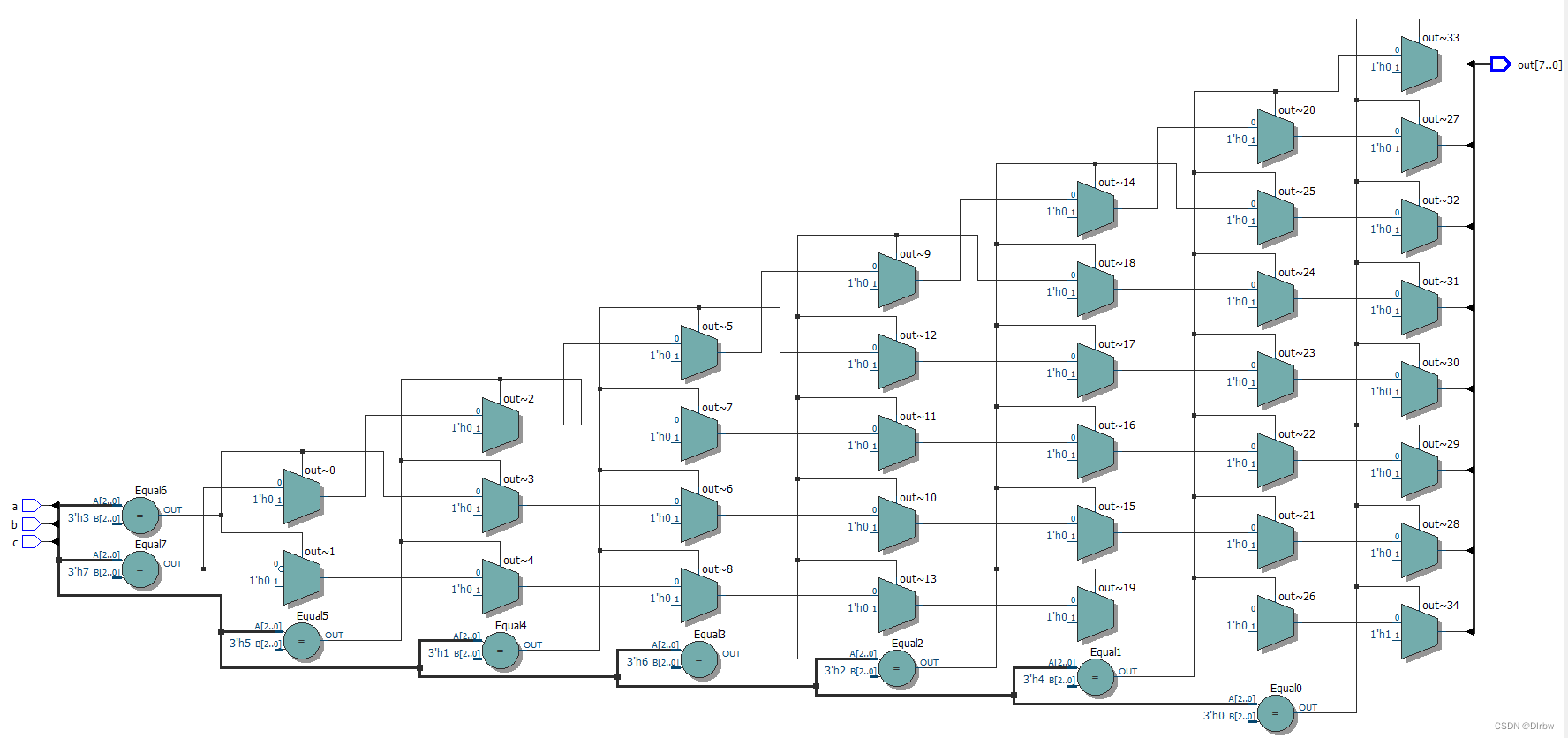

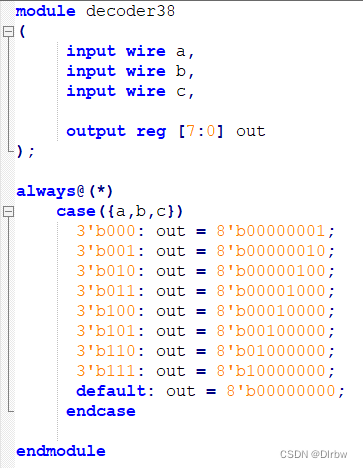

(2)always中case实现方法

生成的RTL视图

仿真验证

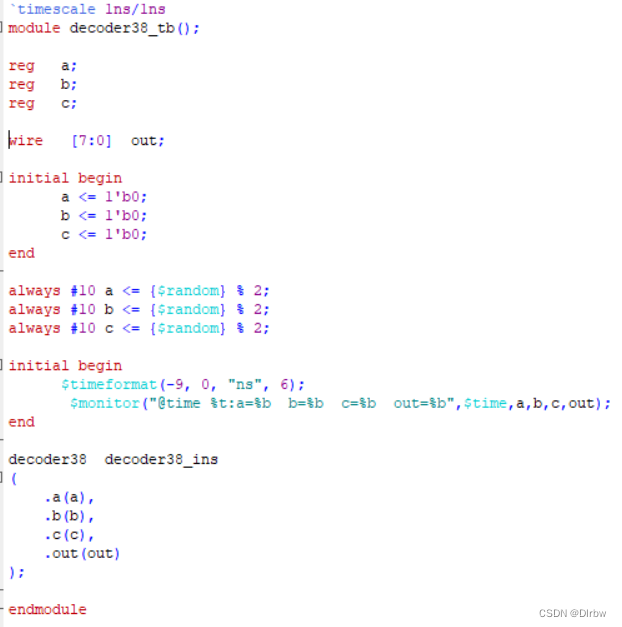

(1)仿真文件编写

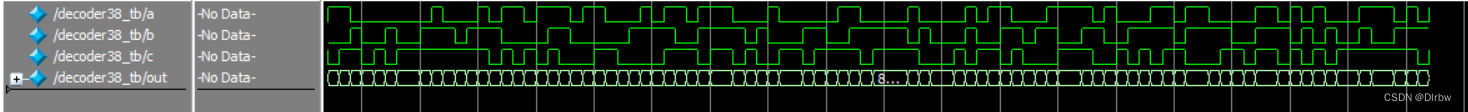

(2)仿真波形验证

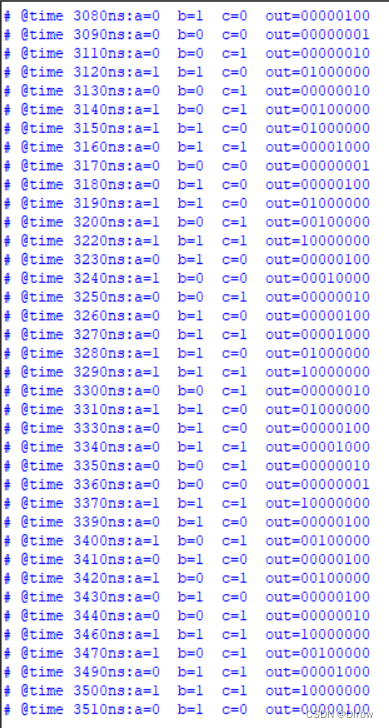

(3)Transcript结果

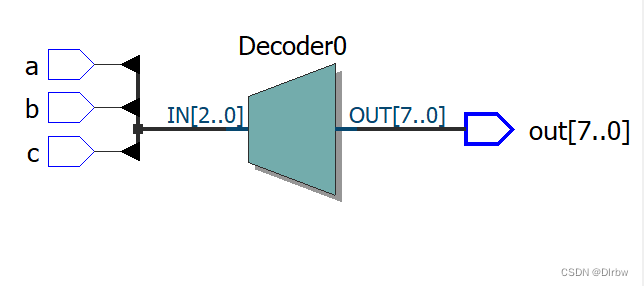

1.2 Logsim 3-8译码器

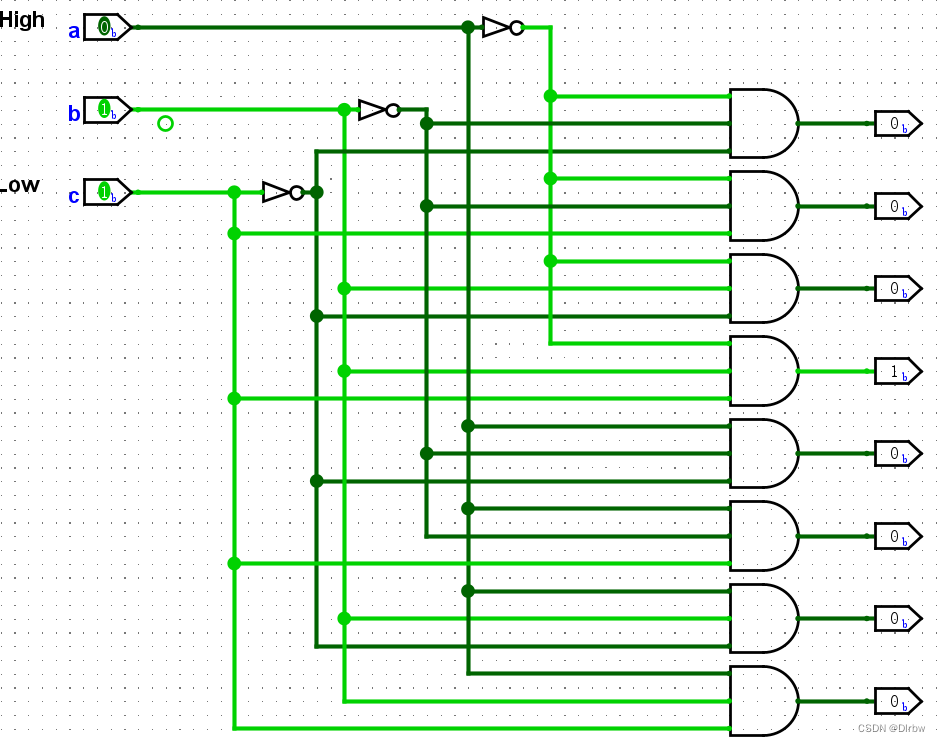

电路图

逻辑真值表

| a | b | c | cout |

|---|---|---|---|

| 0 | 0 | 0 | 00000001 |

| 0 | 0 | 1 | 00000010 |

| 0 | 1 | 0 | 00000100 |

| 0 | 1 | 1 | 00001000 |

| 1 | 0 | 0 | 00010000 |

| 1 | 0 | 1 | 00100000 |

| 1 | 1 | 0 | 01000000 |

| 1 | 1 | 1 | 10000000 |

1.3注意事项

1.Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

(1)基本上没什么差异。

(2)仿真测试生成的结果与真值表中的结果一致。

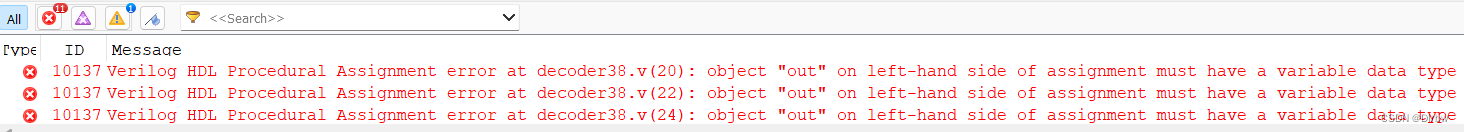

2.Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以?

(1)Verilog代码设计的3-8译码器模块的输出信号要定义为 reg类型而不用默认wire(导线)类型。

(2)当改成wire型是的结果(把 output reg [7:0] out 改为 output [7:0] out)

我们可以看到此时会报错,为什么会出错呢?究其原因,我们会发现在Verilog中,wire永远是wire,就是相当于一条连线,用来连接电路,不能存储数据,无驱动能力,是组合逻辑,只能在assign左侧赋值,不能在always @ 中赋值;但reg可以综合成register,latch,甚至wire(当其只是中间变量的时候),可以用于组合逻辑或者时序逻辑,能存储数据,有驱动能力,在always @模块表达式左侧被赋值。两个共同具有性质:都能用于assign与always @模块表达式的右侧。

2、全加器相关实验

2.1 1位全加器

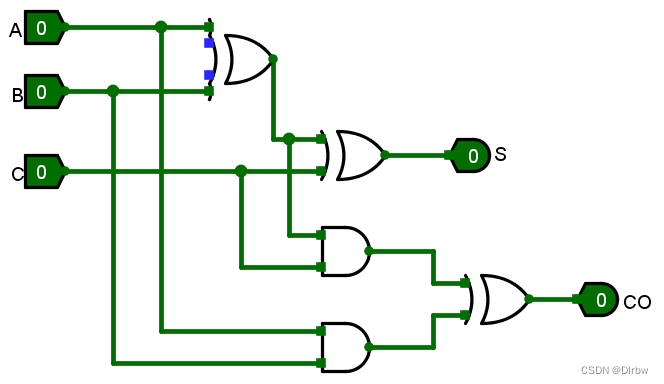

logsim 1位全加器

(1)电路图

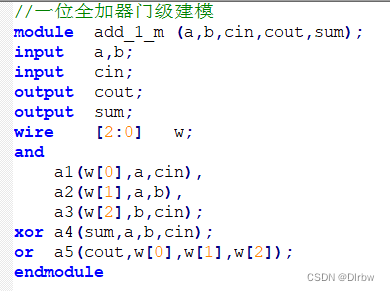

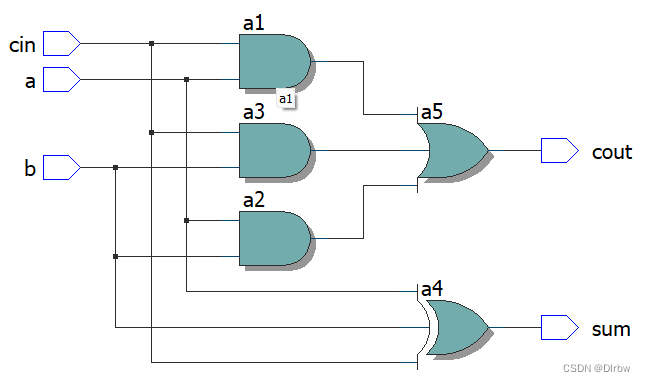

Verilog 1位全加器

门级建模代码编写及生成的RTL视图

生成的RTL视图

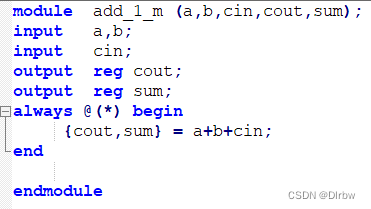

行为级建模代码编写及生成的RTL视图

生成的RTL视图

2.2 4位全加器

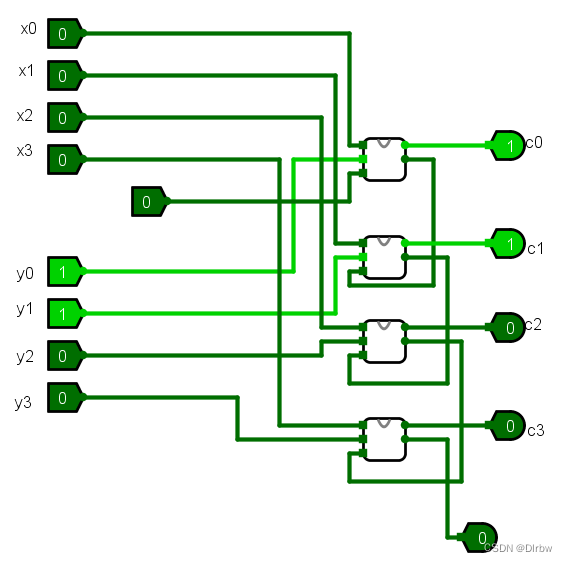

logsim 通过一位全加器构建四位全加器

首先对一位全加器进行封装:

然后在另一个电路文件中进行四位全加器的设计:

我们采用串联的方法进行四位全加器的构建,直接对一位全加器进行串行连接就可以实现四位全加器。

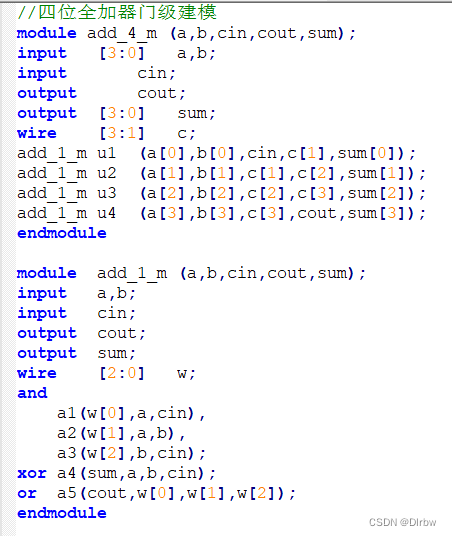

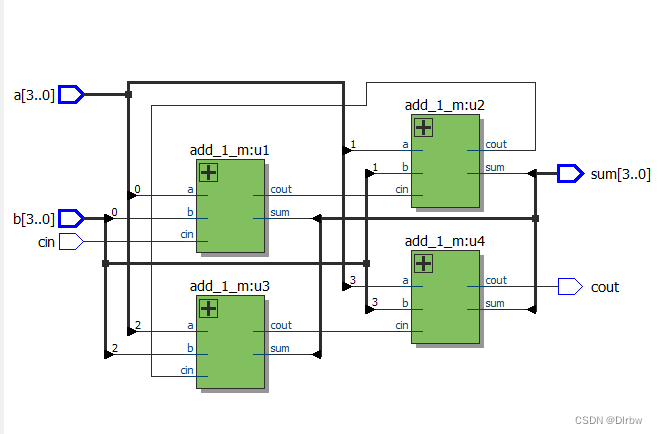

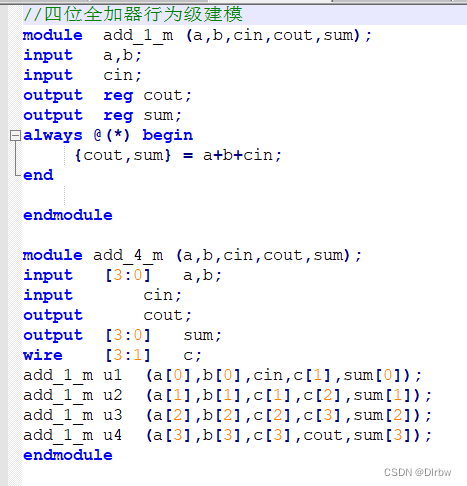

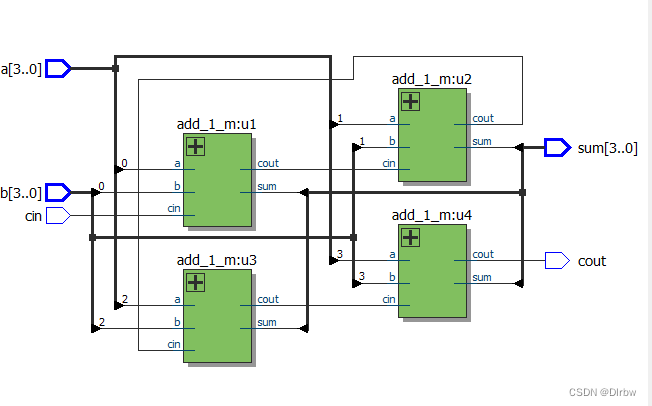

Verilog 4位全加器

采用Verilog模块调用子模块的方式,用4个上面的“1位全加器”级联方式,构成一个“4位全加器”(即串行全加器)

门级建模代码编写及生成的RTL视图

RTL视图

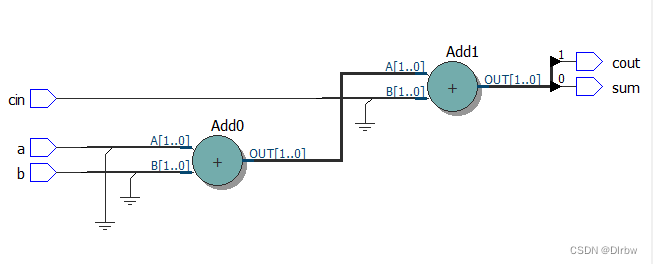

行为级建模代码编写及生成的RTL视图

RTL视图

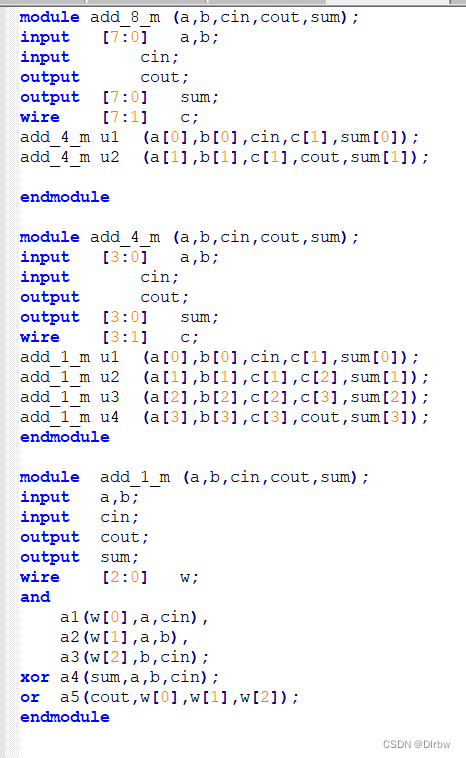

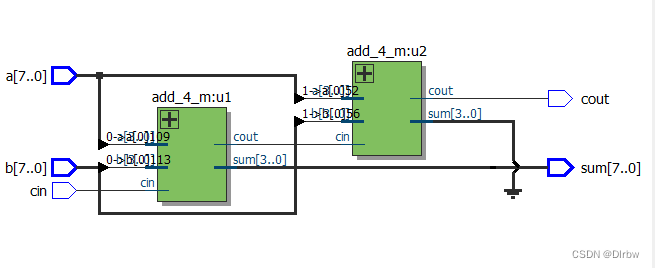

2.3 Verilog 8位全加器

采用Verilog模块调用子模块的方式,先用4个上面的“1位全加器”级联方式,构成一个“4位全加器”,再用2个上面的“4位全加器”级联方式,构成一个“8位全加器”

RTL视图

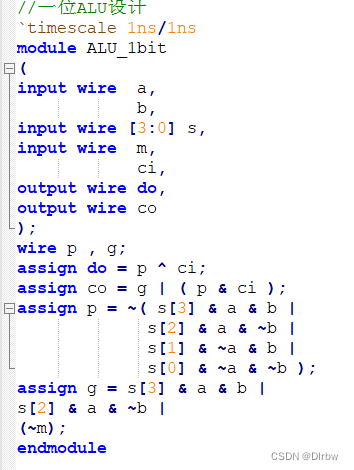

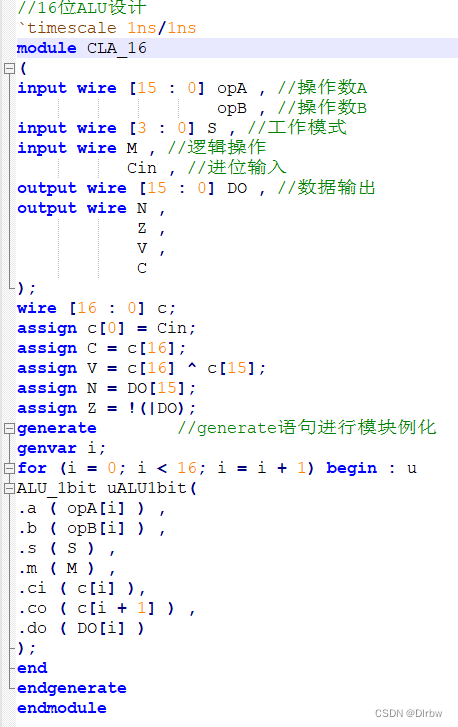

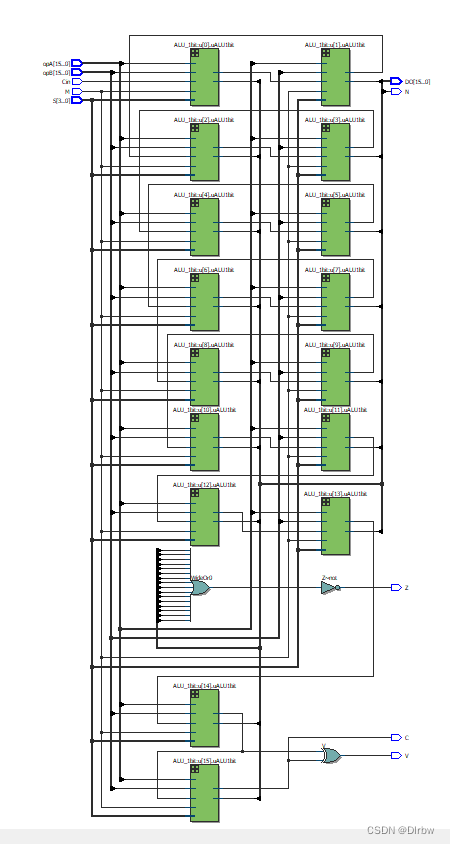

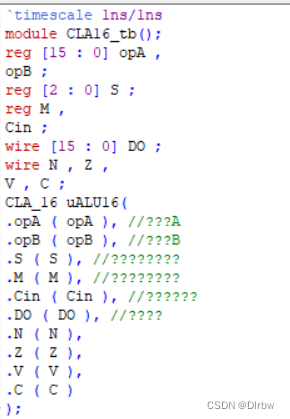

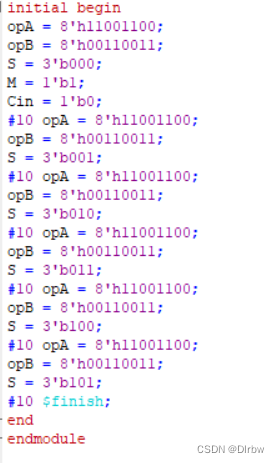

3、16位ALU的电路设计

Verilog代码编写

RTL视图

仿真测试

仿真波形验证

2262

2262

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?