ISE是一个支持数字系统设计的平台,这学期的硬件描述语言课程老师要求用ISE进行编程实验,以后都会记录下实验关键步骤。

软件的使用很简单,就不用记了,和一般IDE很像。

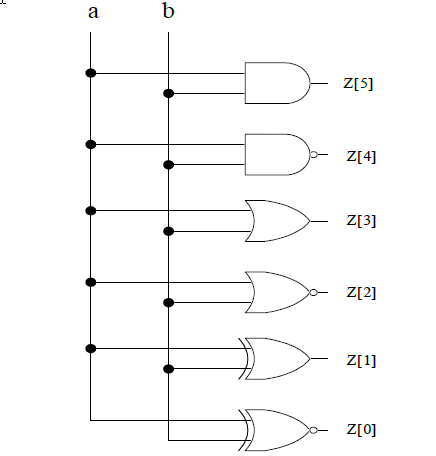

要实现的功能示意图如下:

Implementation part:

module gates2b(

input wire a,

input wire b,

output wire [5:0] z

);

assign z[5] = a&b;

assign z[4] = ~(a&b);

assign z[3] = a|b;

assign z[2] = ~(a|b);

assign z[1] = a^b;

assign z[0] = ~(a^b);

endmodule

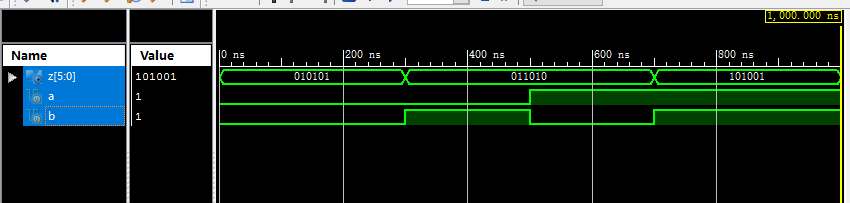

Simulation part:

module gates2bTest;

// Inputs

reg a;

reg b;

// Outputs

wire [5:0] z;

// Instantiate the Unit Under Test (UUT)

gates2b uut (

.a(a),

.b(b),

.z(z)

);

initial begin

// Initialize Inputs

a = 0;

b = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

#200

a <= 0;

b <= 0;

#200

a <= 0;

b <= 1;

#200

a <= 1;

b <= 0;

#200

a <= 1;

b <= 1;

end

endmoduleSimulation Behavioral Model:

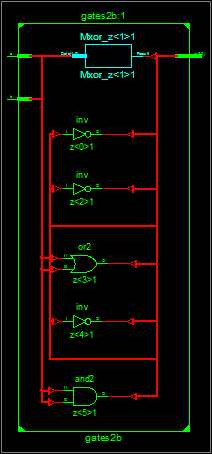

RTL Schematic:

欢迎指正~~~

701

701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?