1. 介绍差分时钟被广泛用于实现高速、耐噪声的时钟传输。钟表制造商包括爱普生在内的公司提供各种格式的差分时钟产品,有必要做出适当的根据系统要求进行选择。爱普生提供三种差分时钟产品标准格式:LV-PECL、LVDS和HCSL,现在我们新增了专有的宽振幅LVDS或WA-LVDS加入产品阵容。本技术说明解释了这四个差分时钟的特性。

2.差分时钟概述

① LV-PECL

LV-PECL代表“低压正发射极耦合逻辑”。正如你从“发射器”一词中看到的,它是一个由双极晶体管组成的输出驱动器。由于ECL(LV-PECL的词根)需要负电源,因此添加了“正”一词来强调驱动器使用正电源运行。在一款电源电压为3.3V的产品问世后,又增加了“低压”一词。如今,由于可在3.3V或更低电压下工作的产品变得相当普遍,“LV-”经常被省略。

LV-PECL适用于高速操作,因为输出晶体管在不关断的情况下工作,如稍后所述。此外,由于振幅相对较大,因此具有低相位噪声特征,以及出色的抗噪性。

② LVDS

LVDS代表“低压差分信号”。顾名思义,LVDS的特点是低振幅操作。LVDS最初主要由美国国家半导体公司(后来被德州仪器公司收购)开发。它于1994年由ANSI/TIA/EIA标准化,目前用于许多电子设备。

最常见的振幅水平为0.35 V(典型值)。通过保持低振幅,实现了低驱动器电流的高速操作。低电流消耗是LVDS的主要优势。然而,由于振幅低,其相位噪声趋于恶化。此外,必须注意的是,接收器需要相当大的功率才能将振幅扩展到所需的水平,在此过程中相位噪声可能会降低。

③ HCSL

HCSL代表“高速电流转向逻辑”。该名称来源于电流输出路径在正负输出端子之间交替控制的电路结构。这种方法是在PCI Express标准中提出的,至今仍然是一种主要的应用。调整爱普生提供的HCSL驱动器的输出波形,使边缘速率适当或不太陡峭。这是因为用于PCI Express的时钟频率通常为100 MHz,并且需要为该频率拟合边缘速率。因此,尽管幅度水平几乎与LV-PECL相同,但相位噪声与之相比有些不利。

④ WA-LVDS

近年来,ASIC和SOC上的时钟接收器越来越定制化,因此上述标准差分时钟并不总是合适的。因此,爱普生最近发布了宽振幅LVDS(WA-LVDS),以提供具有卓越性能和灵活性的差分时钟。

WA-LVDS保持了LVDS负载连接的简单性,并为偏移电压和信号幅度提供了灵活性。偏移电压电平和幅度可以分别从四个电平和十个电平中选择(细节将在后面描述)。因此,在许多情况下,您可以将时钟直接连接到LSI,而不需要额外的组件。当然,与电容器的交流耦合也是可能的。如果选择大振幅,电流消耗会增加,但预期相位噪声会降低。WA-LVDS适用于低功耗和低噪声的两种系统。WA-LVDS的另一个优点是它比LVDS具有更高的PSNR(电源噪声抑制)性能。

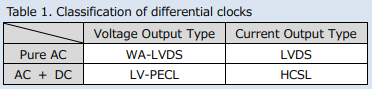

3.差分时钟的分类

虽然它没有得到广泛认可,但差分时钟大致分为两种类型:电流输出型和电压输出型。电流输出类型通过使指定电流通过负载电阻器来获得所需的输出幅度。因此,振幅也取决于负载电阻的精度。另一方面,电压输出型直接向负载输出指定的电压。振幅与负载电阻的精度关系不大。

此外,当从流过负载电阻的电流的角度进行分类时,电流可分为两种类型:纯交流和交流+直流。不可避免地,包含直流组件的时钟驱动器需要过大的电流消耗。

基于这些组合,差分时钟可分为四种类型,如表1所示。新开发的WA-LVDS是一种电压输出型,流经负载电阻的电流是纯交流电。这正是差分时钟的理想组合。

注1:一些产品具有LV-PECL作为电流输出类型的伪实现。

注2:Renesas(前身为IDT)专有的LP-HCSL(低功耗HCSL)是一种HCSL,但它属于与LV-PECL相同的分类。

4.输出电压和电流

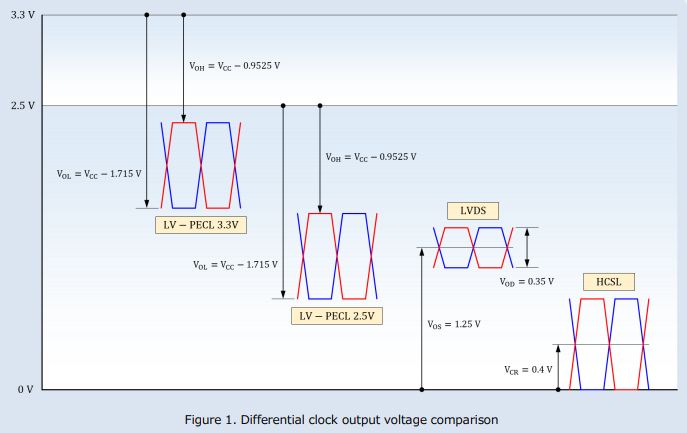

让我们看看现有三种时钟(即LV-PECL、LVDS、HCSL)的输出电压差异。请参考图1。

最独特的可能是LV-PECL。LV-PECL的输出电压相对于电源电压VCC来定义。因此,输出电压值根据电源电压而变化。H电平输出电压VOH和L电平输出电压VOL的规格如图所示。无论VCC如何,差分幅度均为0.7625 V(典型值)。

对于LVDS,偏移电压VOS被指定为1.25V,并且与电源电压无关。差分幅度VOD为0.35V,这是三种方法中明显最小的值。

最后一个是HCSL,其特征是L电平为0V。规范通常确定差分交叉点电压VCR为0.4V。关于H电平通常没有明确的规定。但不可避免的是,它的设计在0.8 V左右。因此,振幅水平与LV-PECL大致相同。

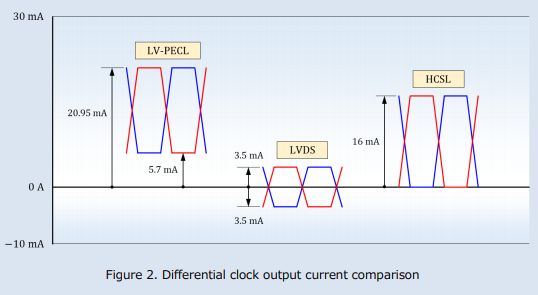

接下来,让我们看看输出电流。这里的输出电流是指从驱动器的输出端子流向负载(或从负载流入)的电流,形成图1所示的输出电压。请参考图2。

如上所述,LV-PECL的输出电压取决于电源电压,但输出电流为与电源电压无关。这是因为终端参考电压也根据电源电压而变化。即使输出L电平,LV-PECL驱动器也需要提供5.7mA。这是LV-PECL在电流消耗方面的一个主要缺点。

LVDS的独特之处在于输出电流是纯交流电,因此不需要多余的电流。此外,由于峰值输出电流限制在3.5mA的小值,LVDS适用于低功耗应用。LVDS的纯交流电流输出还可以将时钟信号与电容器进行交流耦合。

HCSL在输出L电平时不输出电流。因此,即使输出电压幅度为与LV-PECL相比输出电流要低得多。

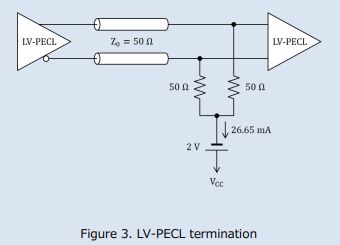

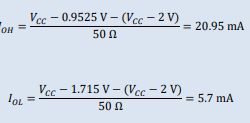

5.电路操作和端接方法接下来,让我们详细解释每种类型的电路操作以及如何连接负载。① LV-PECLLV-PECL的典型端接方法如图3所示。规定50Ω端子必须连接到VCC−2 V,而不是接地。由于电势VCC−2 V必须由用户创建,因此时钟接收电路会有点复杂。

流过H和L电平输出负载的电流(如图2所示)分别计算如下

从上述公式可以理解,从输出端子输出的电流总计为26.65mA。

仅为此终端提供VCC−2 V的恒压源是不切实际的。因此,通常采用另一种方法。图4显示了所谓的Y偏置终止,这是一种方法,其中26.65 mA的电流流过电阻器,产生相当于VCC−2 V的电压。电阻值RT必须根据图中所示的VCC设置。如果VCC=3.3 V,RT=49Ω;或者如果VCC=2.5V,RT=19Ω。电容器可以与RT并联连接,使终端节点更理想地作为交流地。

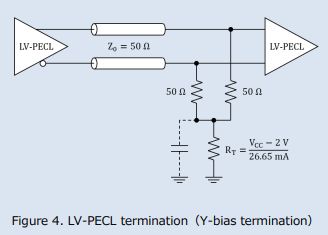

图5显示了另一种方法。电阻器RT被分为两个等效电阻器(2RT),每个电阻器都与一个负载电阻器(50Ω)集成在一起,从而减少了对两个电阻器的需求。如果VCC=3.3V,电阻值为148Ω,如果VCC=2.5V,电阻值为88Ω。总输出电流将与图4相同,但从每个输出端子流出的电流值不同,这将导致电压值略有偏差。此外,由于电路没有端接至50Ω的交流地线,因此该端接不能应用于传输线的末端。只有当时钟驱动器和接收器电路放置在附近时,它才适用。此外,请注意,爱普生不保证使用这种终止方法的时钟特性。

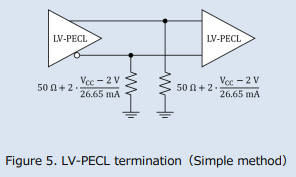

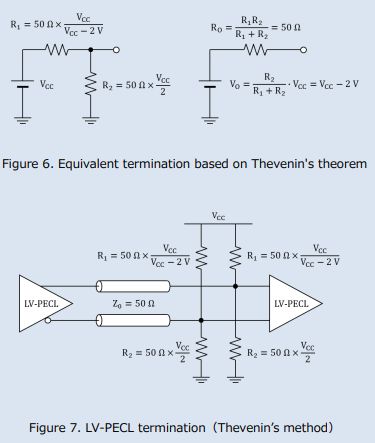

最后,我们将介绍一种名为Thevenin终止的技术。这需要四个电阻器,但最简单。如图6的左图所示,假设电压VCC被两个电阻器R1和R2分压,中点节点被取出。如果我们用戴维南定理变换这个电路,我们将得到右边的等效电路。可以看出,在节点处等效地产生了VCC-2 V和50Ω。将此电路应用于图3中的负载电路,结果如图7所示。这就是所谓的戴维南终止。使用此技术时,VCC电源的输出阻抗必须相对于R1的值保持足够低。此外,您需要小心VCC中的噪声,因为它可能会降低时钟质量。

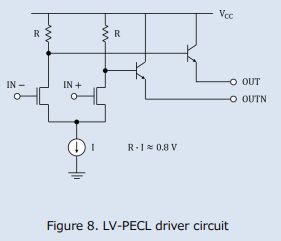

接下来,让我们检查图8所示的LV-PECL驱动器的内部电路配置。输出级是具有公共集电极的开放发射极配置。这是一种通常被称为“发射极跟随器”的电路,因为发射极电势会随着基极电势而变化。通过用MOS晶体管切换恒流“I”,VCC或VCC-0.8V交替施加到双极晶体管的基极端子。

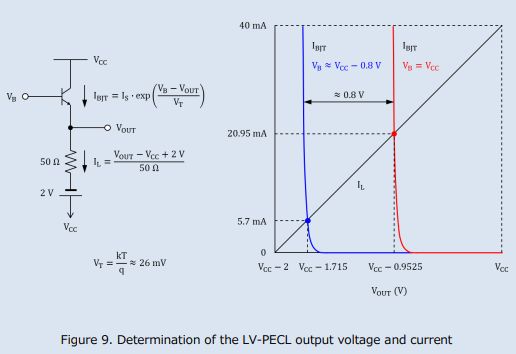

图9展示了如何确定LV-PECL的输出电压和电流。通过双极晶体管的电流IBJT和通过负载电阻器的电流IL使用输出电压VOUT作为参数表示。输出电压和电流在两者相互平衡的点上确定。

如果基极电压VB等于VCC,则IBJT将是图上的红线。当VOUT为VCC−0.9525 V时,IBJT和IL必须平衡,并且根据LV-PECL规范,该点的电流值必须为20.95 mA。为了满足这些特性,调整双极晶体管的尺寸。当该晶体管的基极电压降至VCC-0.8V时,IBJT会跟随一条蓝线。在这种情况下,当VOUT为VCC-1.715V时,IBJT和IL是平衡的,此时的电流值为5.7mA。这样,就满足了LV-PECL的L电平规格。

如果负载电阻偏离50Ω,IL图(黑线)的斜率将增加或减小。但是,您可以理解,即使在这种情况下,输出电压的变化量也很小。从这个特征可以说LV-PECL是一种电压输出型驱动器。请注意,最近爱普生的LV-PECL驱动器使用MOS晶体管而不是双极晶体管。在这种情况下,实现了与图8中略有不同的独特电路配置,但这里将省略其说明。

顺便说一句,你可能会觉得奇怪,VOH和VOL被指定为小数点后3到4位的非常详细的数字。这可能是因为规格被设置为模仿首次发布的产品的特性。实际上,这些数字因制造商和产品而异,因此请在选择产品时查看数据表。

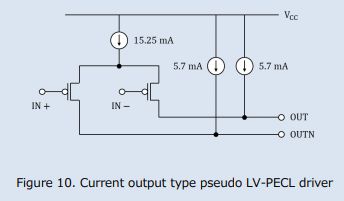

一些LV-PECL驱动器使用电流输出型电路,如图10所示。如果负载为50Ω,则可以获得与电压型相同的结果,但图5所示的简单端接方法不能应用于这种类型的驱动器。这种电路的缺点是,与射极跟随器电路相比,它往往更容易受到寄生电感的影响。因此,振铃可能会叠加在时钟波形上。爱普生过去在一些SAW振荡器中使用这种电路,但现在所有的LV-PECL都统一为电压输出型。

② LVDS

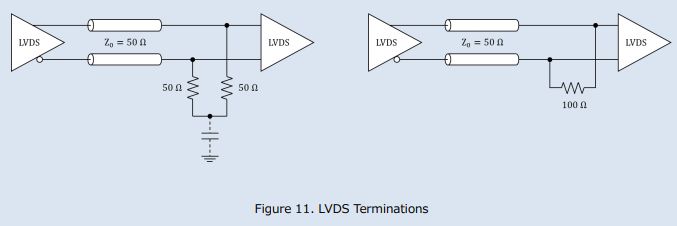

LVDS端接方法如图11所示。由于LVDS的输出电流是纯交流电,因此50Ω负载连接到浮动节点,如左图所示。该节点恒定在1.25V,因此被认为是交流接地。1.25V电压由驱动器设置,因此不需要在接收器侧提供偏置电压。您还可以在端接节点连接一个电容器,使交流接地更加理想。这也可能有效地消除共模噪声。但在通常情况下,这是不必要的。在许多情况下,两个50Ω电阻器可以用一个100Ω电阻器代替,以创建差分100Ω终端,如右图所示。

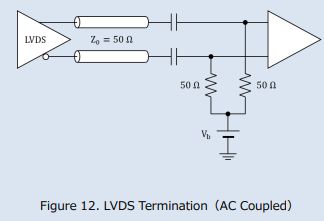

由于LVDS的输出电流是纯交流,因此可以与交流耦合电容器一起使用,如图12所示。电容器可以插入传输线的发射侧或接收侧。在这种情况下,您需要在接收侧准备偏置电压Vb。Vb的值可以根据接收电路的规格任意设置。Vb需要是一个足够低的阻抗电压源,以保证50Ω的端接,或者相反,需要足够高的阻抗,以保证100Ω的差分端接。您还可以使用图7所示的Thevenin终端。

请注意,如果时钟占空比偏离50%,输出电流中会出现直流分量。在这种情况下,电荷可能会积聚在交流耦合电容器中,导致波形变化。变化程度取决于产品的电路设计,因此请在使用前仔细检查。

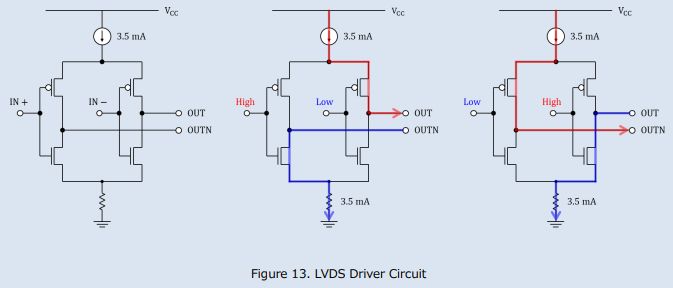

图13显示了LVDS驱动器的内部电路配置。它由一个3.5mA的恒流源、四个MOS开关和一个使用有源元件的可变电阻器组成。图13中的中心和右侧数字显示了电流路径的切换操作。通过在这两种状态之间交替,交流电流流过负载。

3.5mA的恒定电流始终流过电阻器,因此可以通过改变其电阻来调节偏移电压VOS。LVDS驱动器具有CMFB(共模反馈)电路,其功能是将VOS保持在1.25 V。有三种类型的CMFB电路:一种监测实际输出波形,一种从IC内驱动器电路的副本估计VOS,以及两者的混合类型。

③ HCSL

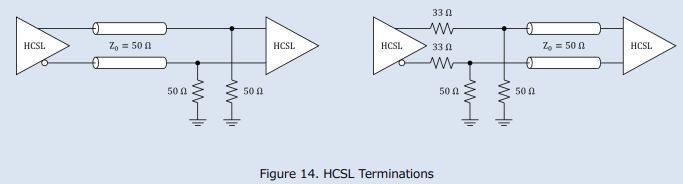

HCSL终止方法如图14所示。图的左侧显示了接收侧端接的示例。这是一种简单、易于理解、问题较少的终止方法。高电平输出侧的负载由HCSL驱动器提供16mA的电流,产生0.8V的幅度。低电平输出侧负载的电流供应被切断,电压变为地电平。

PCI Express标准中规定了另一种端接方法,如图14右侧所示。驱动器侧提供端接电阻器,驱动器的电流输出分为两个方向:50Ω负载和接收电路。在接收器端,波形被全反射,因此振幅加倍,形成振幅为0.8V的波形。反射波形被50Ω吸收,但由于连接了HCSL驱动器,阻抗略低于50Ω。为了使驱动器在节点上不那么显眼,在驱动器的输出端插入了33Ω电阻器。然而,即使采用这种方法,也很难确保完美的阻抗匹配。因此,一些波形将在驱动器侧重新反射。因此,接收器端子处的波形根据传输线的电长度而变化。你必须在设计电路时考虑到这种行为。波形可以通过以下方式进行模拟时钟制造商提供的IBIS型号。

图14中的端子基于差分100Ω传输,但也可以使用差分85Ω。这样做的目的是通过缩小传输线之间的间距来减小电路板的尺寸,或者减小板的厚度。在这种情况下,电阻必须为42.5Ω而不是50Ω,27Ω而不是33Ω。由于必须保持电压振幅,因此需要输出电流的(100/85)倍。

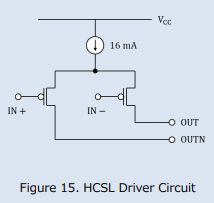

图15显示了HCSL驱动器的内部电路配置。它具有简单的配置,其中16mA的恒定电流通过MOS开关交替施加到两个输出端子。该电路与图10中的电路非常相似,去掉了无用的5.7mA恒流源。

恒流源的交流阻抗理想情况下为∞,MOS开关的交流阻抗理论上为0(处于导通状态)或∞(处于关断状态),因此即使在图14右侧所示的连接情况下,HCSL驱动器基本上也不会导致阻抗失配。然而,寄生电容等因素会破坏理想状态,因此阻抗失配在实际中是不可避免的。

④ WA-LVDS

WA-LVDS的端接方法与LVDS相同,请参考图11或图12。在LVDS具有AC耦合负载的情况下,如果占空比偏离50%,则会产生DC电流,并且担心电荷会积聚在电容器中。由于WA-LVDS是一种电压输出型,其优点是此类问题较少。

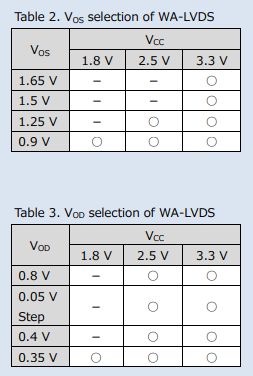

使用LVDS时,偏移电压(VOS)固定为1.25 V,差分输出电压(VOD)固定为0.35 V,但使用WA-LVDS时,您可以分别从4个电平和5个电平中进行选择,如下表所示。可选值取决于电源电压VCC。交流耦合时,选择一个接近VCC/2的VOS值。

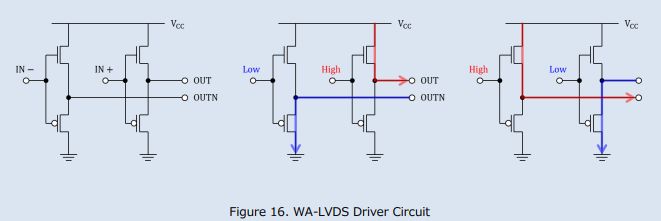

图16显示了WA-LVDS驱动器的内部电路配置。N型MOS晶体管连接到VCC侧,P型MOS晶体管接地侧,源极端子连接到输出端。这是一种称为源极跟随器电路的配置,类似于LV-PECL的发射极跟随器。输出电压电平取决于输入到栅极端子的IN+和IN-的电势。实现了一种独特的电路来控制输入幅度电势,以满足所需的VOS和VOD。电流路径切换操作如图16的中心和右侧图所示。它的行为类似于LVDS。

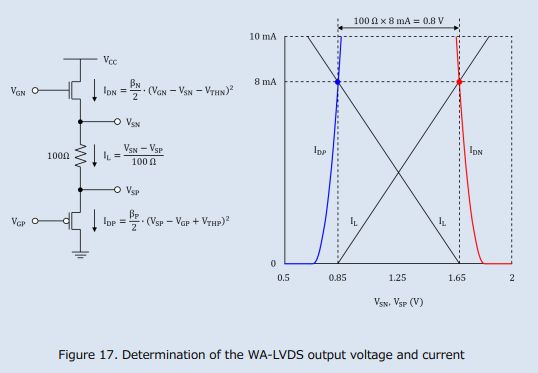

参考图17,让我们看看WA-LVDS输出电压和电流是如何确定的。他们是由流过N型MOS晶体管的电流IDN、流过100Ω负载电阻的电流IL和流过P型MOS晶体管中的电流IDP之间的平衡决定。

图17中的图表显示了输出VOS=1.25V和VOD=0.8V波形的状态。IDN和IDP由每个MOS晶体管的栅源电压决定。当电源电压改变时,所有电流值都会改变。假设VSN和VSP将流过IDN和IDP的相同电流(图中为8mA)。如果VSN和VSP之间的差值是电流值的100倍(图中为0.8V),则IL也将具有相同的电流值,电路将处于平衡状态。

通过适当地调整MOS晶体管VGN和VGP的栅极电压,可以任意设置上述平衡点,从而可以满足所需的偏移电压VOS和差分输出电压VOD。WA-LVDS驱动器IC中实现了用于此目的的内部调整机制。

6.输出幅度、输出电流和抖动之间的相关性

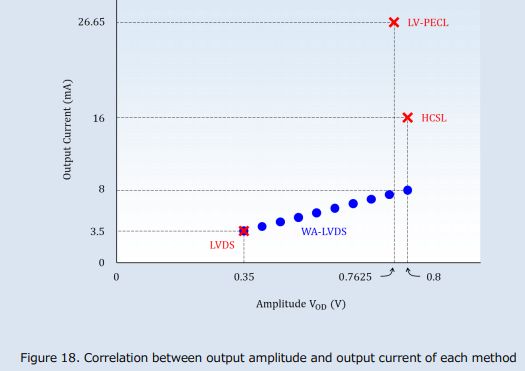

让我们比较一下上述四种方法的输出幅度和输出电流之间的相关性。请参见图18。

WA-LVDS(蓝色●)有10个图,因为差分输出电压VOD可以在10个步骤中切换。波形形成方法与LVDS相同,因此当VOD为0.35V时,它与LVDS匹配。每次振幅增加时,电流都会增加,但即使VOD为0.8V,输出电流也会保持在8mA。这是因为输出电流是纯交流电。

相比之下,即使振幅在0.8 V时相同,HCSL也需要两倍的电流,即16 mA。LV-PECL需要26.65 mA的电流,即使其振幅稍小。通过这样的比较,你可以看到WA-LVDS的效率有多高。

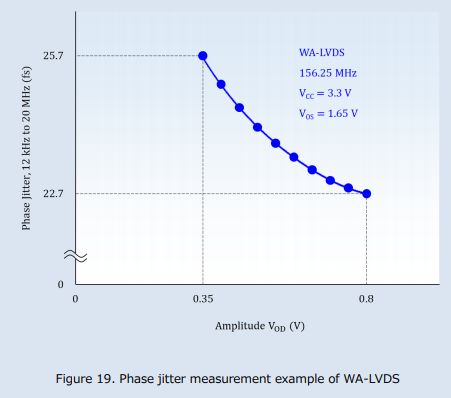

WA-LVDS测量的相位抖动示例如图19所示。可以清楚地看到,相位抖动随着差分幅度VOD的增加而减小。因此,如果电路的电流消耗不受限制,更高的差分幅度VOD是获得更高电路性能的更好选择

7.结论

我们解释了LV-PECL、LVDS和HCSL三种驱动器的特点和使用方法,以及新开发的WA-LVDS。爱普生计划在未来扩大WA-LVDS产品线。如果您对本技术说明的内容有任何疑问,请根据以下信息与我们联系。

3678

3678

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?