单片机用的是:正点原子的STM32f103zet6 嵌入式小白,如果有错误的地方,大家多多包涵!

GPIO 是控制或者采集外部器件的信息的外设,即负责输入输出

作用:单片机与外界交流信息的唯一途径 (TTL电平输入输出)--->(电脑通过ch340驱动芯片将usb电平转换为TTL电平就可以跟开发板交流了)

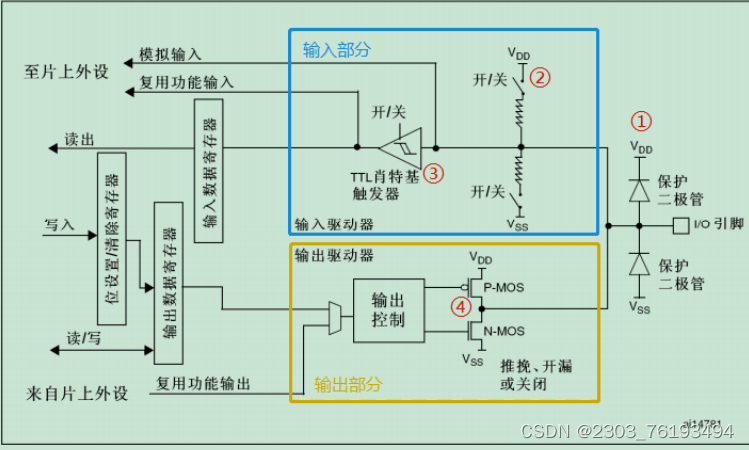

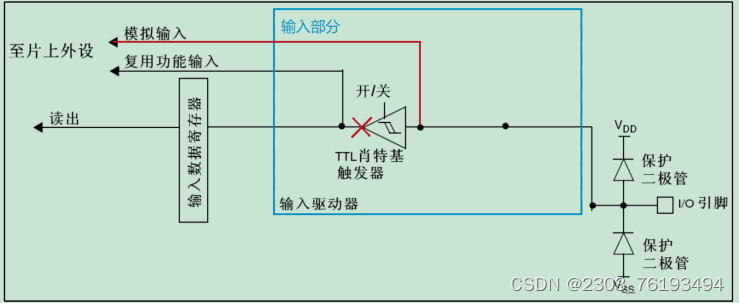

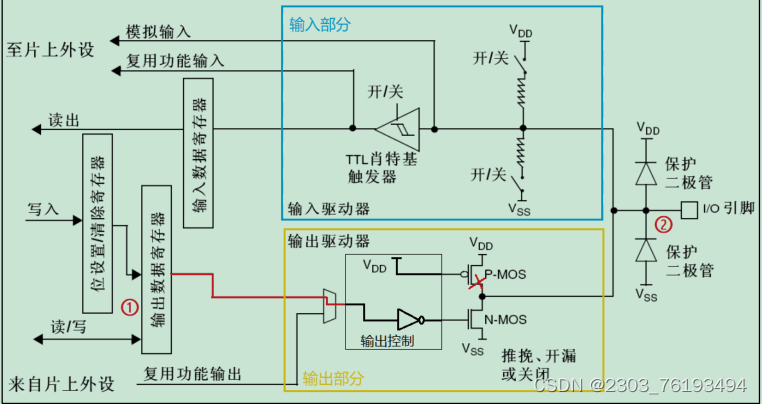

① 保护二极管

保护二极管共有两个,用于保护引脚外部过高或过低的电压输入。当引脚输入电压高于

VDD 时,上面的二极管导通,当引脚输入电压低于 VSS 时,下面的二极管导通,从而使输入

芯片内部的电压处于比较稳定的值。

② 上拉、下拉电阻

这两个开关由寄存器控制。即没有外部的上、下拉电压,引脚的电平由引脚内部上、下拉决定,开启内部上拉电阻工作,

引脚电平为高,开启内部下拉电阻工作,则引脚电平为低。STM32 的内部上拉是一种“弱上拉”,这样的上拉电流很弱,

如果有要求大电流还是得外部上拉。

上拉电阻和下拉电阻的用处和区别

上拉电阻和下拉电阻二者共同的作用是:避免电压的“悬浮”,造成电路的不稳定

上拉电阻:1、概念:将一个不确定的信号,通过一个电阻与电源VCC相连,固定在高电平;

2、上拉是对器件注入电流,灌电流;

3、当一个接有上拉电阻的IO端口设置为输入状态时,它的常态为高电平。

下拉电阻: 1、 概念:将一个不确定的信号,通过一个电阻与地GND相连,固定在低电平;

2、下拉是从器件输出电流,拉电流;

3、当一个接有下拉电阻的IO端口设置为输入状态时,它的常态为低电平。

③ 施密特触发器

施密特触发器可作为波形整形电路,能将模拟信号波形整形为数字电路能够处理的方波波形,

而且由于施密特触发器具有滞回特性,所以可用于抗干扰。

④ P-MOS 管和 N-MOS 管

这个结构控制 GPIO 的开漏输出和推挽输出两种模式

八大工作模式:

外设:分为片上外设(芯片以内,内核以外的)与片外外设(芯片以外)

输出:(通用模式是单片机CPU与外界交流,复用模式是片上外设与外界交流)

1.通用推挽输出(可以输出高低电平)

2.通用开漏输出(只能输出低电平,高阻态,如果外接上拉电阻,通常情况下输出高电平)(上拉电阻会跟电源连接在一起,下拉电阻接地)

3.复用推挽输出

4.复用开漏输出

输入:

1.浮空输入

2.上拉输入

3.下拉输入

4.模拟输入

输出过程:数据载入输出数据寄存器-->经过选择器-->mos管(推挽输出:P,N mos管都开启,Pmos管只允许输出高电平,Nmos管只允许输出低电平 开漏输出:Nmos管导通,只能输出低电平)。

怎么通过GPIOA操作相应寄存器?(寄存器是实物,它其实是一种时序逻辑电路,通过触发器或锁存器用来存放二进制数,用处存放数据和命令等)

GPIOA是一个宏定义指针,指向结构体首地址,对应的寄存器在结构体地址是连续的寄存器在STM32F407中IO口GPIOA挂载在AHP1总线上,

所以GPIOA等于AHP1总线基地址+外设基地址+寄存器偏移量,就是对应的寄存器位置,知道地址我们就能操控对应的寄存器了。

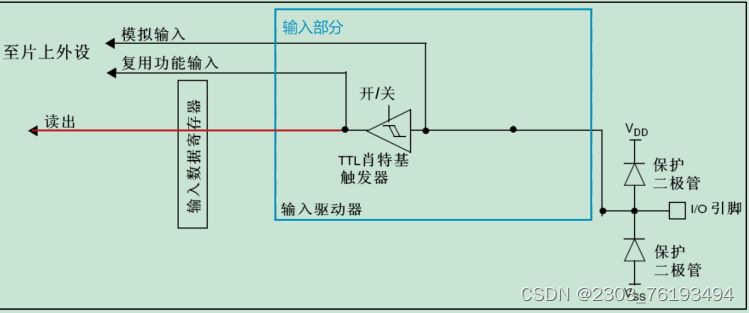

1、输入浮空

输入浮空模式:上拉/下拉电阻为断开状态,施密特触发器打开,输出被禁止。输入浮空模

式下,IO 口的电平完全是由外部电路决定。如果 IO 引脚没有连接其他的设备,那么检测其输

入电平是不确定的。

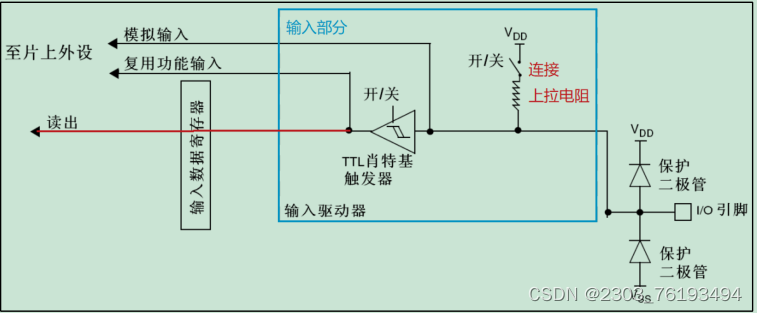

2、输入上拉

输入上拉模式:上拉电阻导通,施密特触发器打开,输出被禁止。在需要外部上拉电阻的

时候,可以使用内部上拉电阻,这样可以节省一个外部电阻,但是内部上拉电阻的阻值较大,

所以只是“弱上拉”,不适合做电流型驱动。

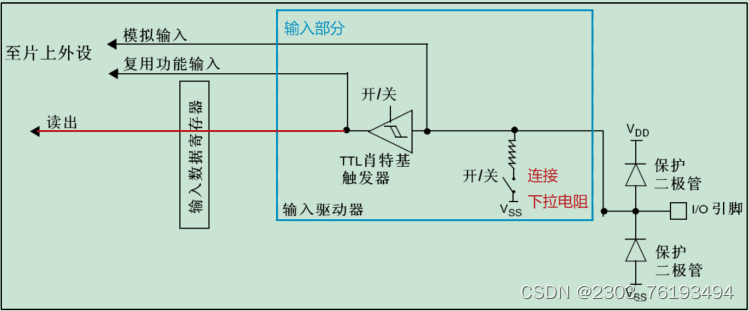

3、输入下拉

输入下拉模式:下拉电阻导通,施密特触发器打开,输出被禁止。在需要外部下拉电阻的

时候,可以使用内部下拉电阻,这样可以节省一个外部电阻,但是内部下拉电阻的阻值较大,

所以不适合做电流型驱动。

4、模拟功能

模拟功能:上下拉电阻断开,施密特触发器关闭,双 MOS 管也关闭。其他外设可以通过模

拟通道输入输出。该模式下需要用到芯片内部的模拟电路单元单元,用于 ADC、DAC、MCO

这类操作模拟信号的外设。

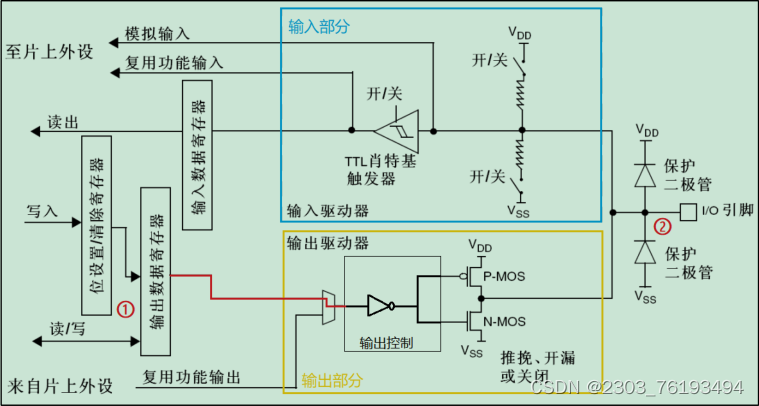

5、开漏输出

开漏输出模式:STM32 的开漏输出模式是数字电路输出的一种,从结果上看它只能输出低

电平 Vss 或者高阻态。开漏输出模式下 P-MOS 一直在截止状态,输出数据寄存器的逻辑 0 经过

“输出控制”的取反操作后,输出逻辑 1 到 N-MOS 管的栅极,这时 N-MOS 管就会导通,

使得 IO 引脚连接到 VSS,即输出低电平。如果输出数据寄存器的值为 1,经过“输出控制”

的取反操作后,输出逻辑 0 到 N-MOS 管的栅极,这时 N-MOS 管就会截止。又因为 P-MOS

管是一直截止的,使得 IO 引脚呈现高阻态,即不输出低电平,也不输出高电平。因此要 IO

引脚输出高电平就必须接上拉电阻。 又由于 F1 系列的开漏输出模式下,内部的上下拉电

阻不可用,所以只能通过接芯片外部上拉电阻的方式,实现开漏输出模式下输出高电平。

如果芯片外部不接上拉电阻,那么开漏输出模式下,IO 无法输出高电平。

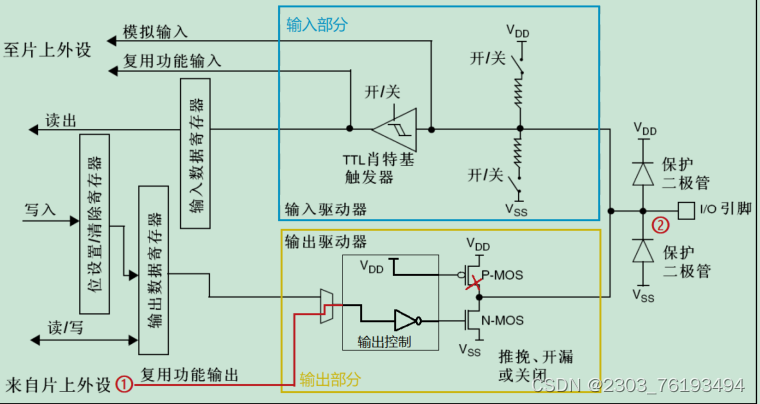

6、推挽输出

如果输出数据寄存器①的值为 0,经过“输出控制”取反操作后,输出逻辑 1 到 P-MOS

管的栅极,这时 P-MOS 管就会截止,同时也会输出逻辑 1 到 N-MOS 管的栅极,这时 N-

MOS 管就会导通,使得 IO 引脚接到 VSS,即输出低电平。

如果输出数据寄存器的值为 1 ,经过“输出控制”取反操作后,输出逻辑 0 到 N-MOS

管的栅极,这时 N-MOS 管就会截止,同时也会输出逻辑 0 到 P-MOS 管的栅极,这时 P-

MOS 管就会导通,使得 IO 引脚接到 VDD,即输出高电平。

7、开漏式复用功能和8、推挽式复用功能

一个 IO 口可以是通用的 IO 口功能

一个 IO 口可以是通用的 IO 口功能

这就是 IO 口的复用功能。一个 IO 口可以是多个外设的功能引脚,我们需要选择作为其中一个

外设的功能引脚。当选择复用功能时,引脚的状态是由对应的外设控制,而不是输出数据寄存

器。

GPIO配置流程:

1.打开对应的时钟(为外设的工作提供心跳)

2.清空对应的寄存器值,(防止复位后,复位值的影响)

3.设置模式寄存器(32位寄存器,每两位控制一个端口,比如PA0到PA15)

4.设置输出类型寄存器

5.配置输出速度寄存器

6.上下寄存器可配可不配,M4系列中是弱上下拉对输出电平没有什么影响

317

317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?