一、System Verilog

1. 发展背景和目的

SystemVerilog 的发展始于对传统 Verilog HDL 的扩展需求。Verilog 最初是一种用于描述和仿真数字电路的语言,但随着数字电路设计复杂性的增加,出现了更多的需求,如验证、复杂数据结构的支持以及高级抽象的引入。为了应对这些挑战,SystemVerilog 在 2002 年被推出,并在随后的几年中不断发展和完善,成为了一种全面的硬件设计和验证语言。

2. 主要特性

SystemVerilog 的设计目标是通过增强 Verilog 的能力来支持以下主要特性:

2.1硬件描述能力增强

SystemVerilog 在传统的 Verilog 基础上引入了更多的数据类型(如 bit, logic, byte, int, shortint, longint 等)、结构体、联合体、枚举等,使得可以更方便地描述复杂的硬件结构和数据。

2.2验证能力增强

引入了类(class)和对象(object)的概念,支持面向对象的编程方式,可以更轻松地组织和管理复杂的验证环境和测试用例。此外,引入了约束随机测试(Constraint Randomization)和事务级建模(Transaction Level Modeling,TLM)等技术,使得验证更高效、更容易实现全面的覆盖率。

2.3并发性和并行处理

支持多线程、进程和并发块(concurrent block)的定义,使得设计可以更好地利用现代硬件的并行处理能力。

2.4接口和连接

引入了更灵活的接口定义和连接方式,支持更复杂的模块互联和系统级集成。

2.5系统级建模

支持在较高的抽象层次上描述系统和模块之间的交互,使得可以更轻松地进行系统级仿真和验证。

3. 应用领域

3.1ASIC 设计

包括复杂的数字电路设计,如处理器、通信芯片等。

3.2FPGA 设计

用于实时应用和可编程逻辑密集型应用的设计。

3.3硬件验证

确保硬件设计在各种条件下都能按预期工作的领域。

3.4高级功能设计

支持复杂控制逻辑、数据结构和状态机的实现。

3.5仿真和调试

用于验证和调试硬件设计的工具。

3.6跨平台和复用性

能够在不同工具和平台上使用,并支持设计的复用。

4. Verilog 和 SystemVerilog 之间的区别

4.1数据类型和结构

Verilog 示例:

module example_verilog;

reg [7:0] data; // 定义一个 8 位寄存器

initial begin

data = 8'hFF; // 初始化 data 为全 1

$display("Verilog: data = %h", data); // 打印十六进制值

$finish;

end

endmodule

SystemVerilog 示例:

module example_systemverilog;

logic [7:0] data; // 定义一个 8 位逻辑类型

initial begin

data = 8'b10101010; // 初始化 data

$display("SystemVerilog: data = %b", data); // 打印二进制值

$finish;

end

endmodule

区别解释:

- Verilog 使用 reg 关键字定义寄存器,而 SystemVerilog 使用 logic 或具体的数据类型如 bit, byte

等。 - SystemVerilog 允许更精确地定义数据类型和位宽,例如 logic [7:0] 表示一个 8 位的逻辑向量。

4.2面向对象的编程能力

SystemVerilog 示例(面向对象):

class Counter;

int count;

// 构造函数

function new();

count = 0;

endfunction

// 成员函数

function void increment();

count++;

endfunction

// 成员函数

function int get_count();

return count;

endfunction

endclass

module test_counter;

Counter my_counter = new();

initial begin

my_counter.increment();

my_counter.increment();

$display("Count: %0d", my_counter.get_count());

$finish;

end

endmodule

区别解释:

- Verilog 不支持类和对象的概念,而 SystemVerilog 可以使用类(class)来定义对象,实现更模块化和可复用的代码结构。

4.3验证功能的增强

SystemVerilog 示例(使用约束随机测试):

module test_rand;

int unsigned a, b, c;

initial begin

// 使用 $random 生成随机数,使用 $urandom_range 生成指定范围内的随机数

a = $random;

b = $urandom_range(1, 100);

c = $urandom_range(0, 255);

// 打印随机数值

$display("Random values: a = %0d, b = %0d, c = %0d", a, b, c);

$finish;

end

endmodule

区别解释:

- Verilog 没有内置的约束随机测试支持,而 SystemVerilog 引入了 $random 和 $urandom_range 等函数,支持更高级的随机数生成和约束。

4.4接口和系统级建模的增强

SystemVerilog 示例(使用接口):

interface my_interface(input logic clk, input logic rst);

logic [7:0] data;

// 定义任务

task send_data;

$display("Sending data: %h", data);

endtask

// 定义连续赋值

always_ff @(posedge clk or posedge rst) begin

if (rst)

data <= 8'h00;

else

data <= data + 1;

end

endinterface

module top_module;

logic clk, rst;

my_interface dut(clk, rst);

initial begin

clk = 0;

rst = 1;

#10 rst = 0;

#100 $finish;

end

always #5 clk = ~clk;

endmodule

区别解释:

- SystemVerilog 中的接口(interface)可以用来定义模块之间的通信和信号传输,支持更复杂的模块化设计。

4.5功能性覆盖率和断言

SystemVerilog 示例(使用断言和覆盖率):

module counter (

input logic clk,

input logic reset,

output logic [3:0] count

);

always_ff @(posedge clk or posedge reset)

if (reset)

count <= 4'b0000;

else

count <= count + 1;

// 断言示例

assert property (

@(posedge clk)

disable iff(reset)

count != 4'b1111

) else $error("Counter overflow detected!");

// 覆盖率示例

cover property (

@(posedge clk)

disable iff(reset)

count >= 4

);

endmodule

区别解释:

- Verilog 不支持断言(assertions)和功能性覆盖率(functional coverage),而 SystemVerilog 引入了这些高级功能,有助于验证设计的正确性和完整性。

4.6接口的增强和参数化

SystemVerilog 示例(带参数化接口):

module producer #(parameter DATA_WIDTH = 8) (

input logic clk,

input logic reset,

output logic [DATA_WIDTH-1:0] data_out

);

// 简单的数据生成逻辑

logic [DATA_WIDTH-1:0] data;

always_ff @(posedge clk or posedge reset)

if (reset)

data <= {DATA_WIDTH{1'b0}};

else

data <= data + 1;

assign data_out = data;

endmodule

module consumer (

input logic clk,

input logic reset,

input logic [7:0] data_in

);

// 实例化带参数的接口

producer #(8) prod_inst (

.clk(clk),

.reset(reset),

.data_out(data_in)

);

endmodule

区别解释:

- SystemVerilog 允许模块和接口的参数化,可以根据需要定义不同的数据宽度和行为,提高了设计的灵活性和可复用性。

4.7动态数组和复杂数据结构

SystemVerilog 示例(使用动态数组):

module dynamic_array_example;

int data_array[];

initial begin

data_array = new[10]; // 创建一个包含 10 个元素的动态数组

foreach (data_array[i])

data_array[i] = i * 2;

$display("Array contents:");

foreach (data_array[i])

$write("%0d ", data_array[i]);

$display("");

$finish;

end

endmodule

区别解释:

- Verilog 不支持动态数组,而 SystemVerilog 引入了类似于高级编程语言的数据结构,如动态数组,使得数据结构更灵活和易于管理。

二、代码实现流水灯

1.led_flow.sv

module led_flow (

input logic clk, // 时钟信号

input logic rst_n, // 复位信号(低有效)

output logic [7:0] led // 8位LED输出

);

logic [23:0] counter; // 24位计数器,用于产生慢时钟信号

// 计数器逻辑

always_ff @(posedge clk or negedge rst_n) begin

if (!rst_n)

counter <= 24'd0;

else

counter <= counter + 1;

end

// LED流水灯逻辑

always_ff @(posedge counter[23] or negedge rst_n) begin

if (!rst_n)

led <= 8'b0000_0001;

else

led <= {led[6:0], led[7]};

end

endmodule

2.testbench

module led_flow_tb;

logic clk;

logic rst_n;

logic [7:0] led;

// 实例化待测试的流水灯模块

led_flow uut (

.clk(clk),

.rst_n(rst_n),

.led(led)

);

// 时钟信号生成

initial begin

clk = 0;

forever #10 clk = ~clk; // 50MHz时钟周期为20ns

end

// 测试逻辑

initial begin

// 初始化信号

rst_n = 0;

#100;

rst_n = 1;

// 仿真运行一段时间后结束

#1000000;

$stop;

end

endmodule

三、实验结果

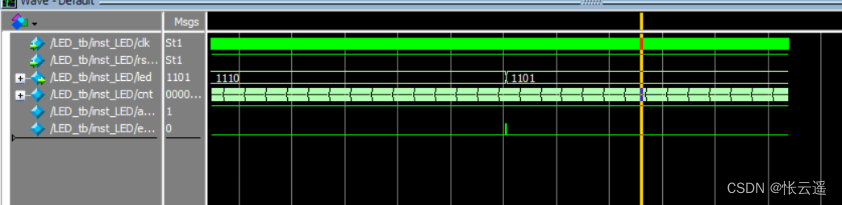

1.testbench图

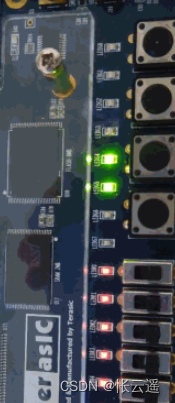

2.流水灯图

178

178

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?