【24蓝桥EDA】PCB绘制经验总结与分析V1.0

一.建议学习路径

EDA学习视频分享,这个讲得很好

https://www.bilibili.com/video/BV1At421h7Ui/?spm_id_from=333.337.search-card.all.click&vd_source=3ca547207338045ac672be8086fa0cda

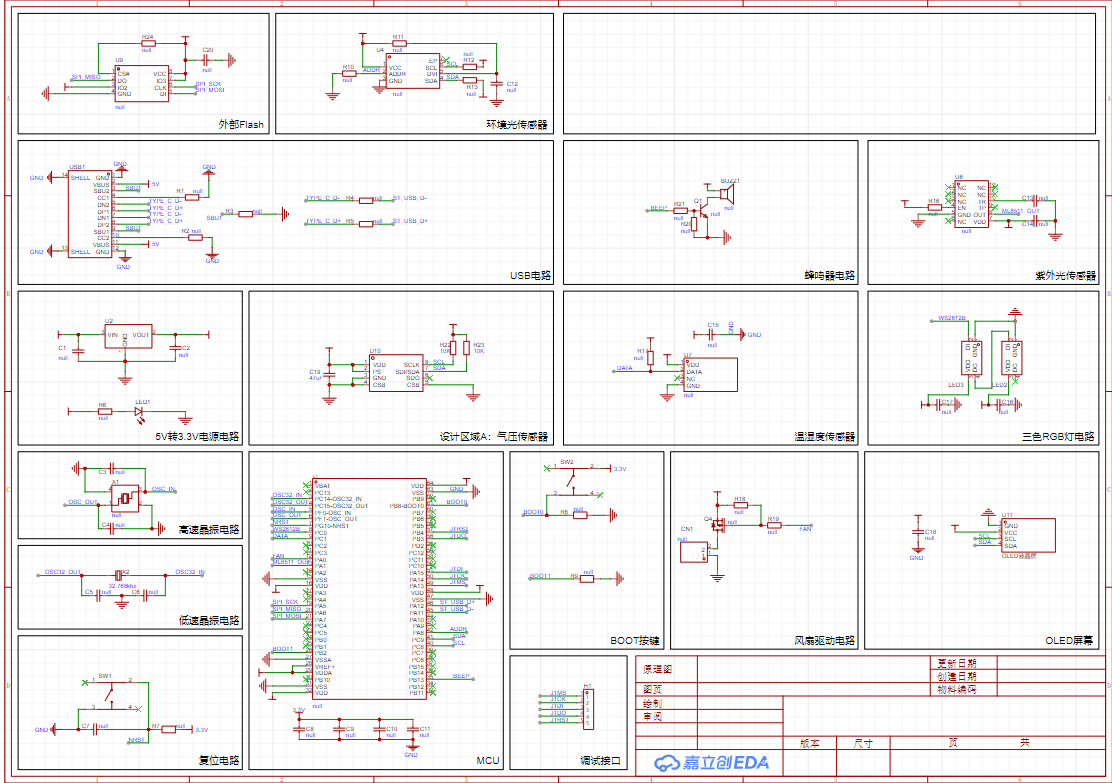

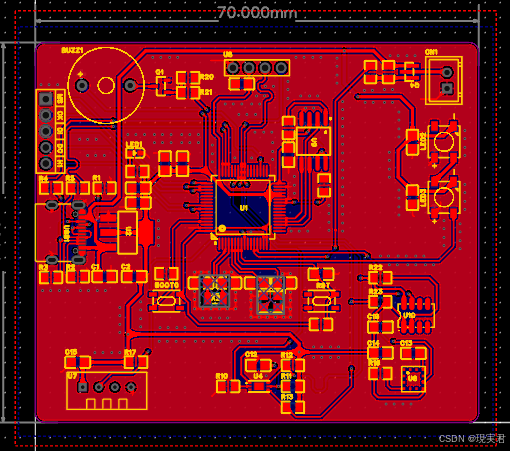

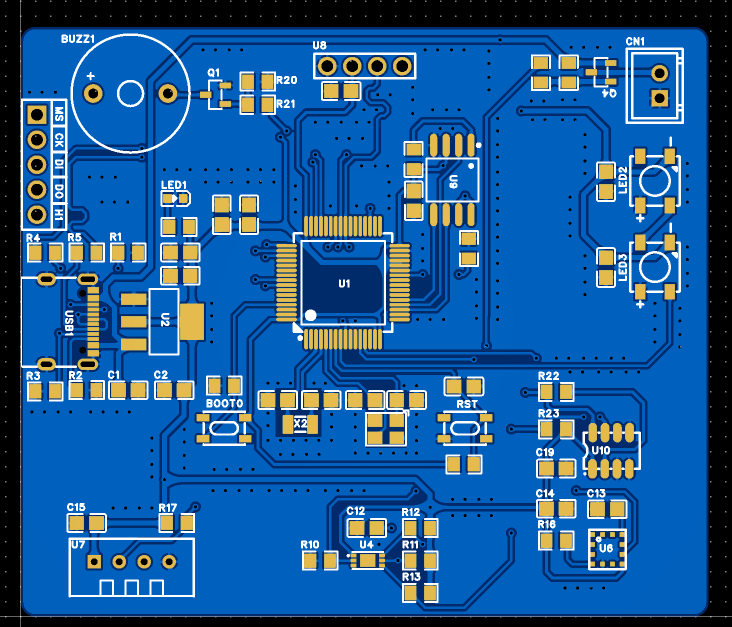

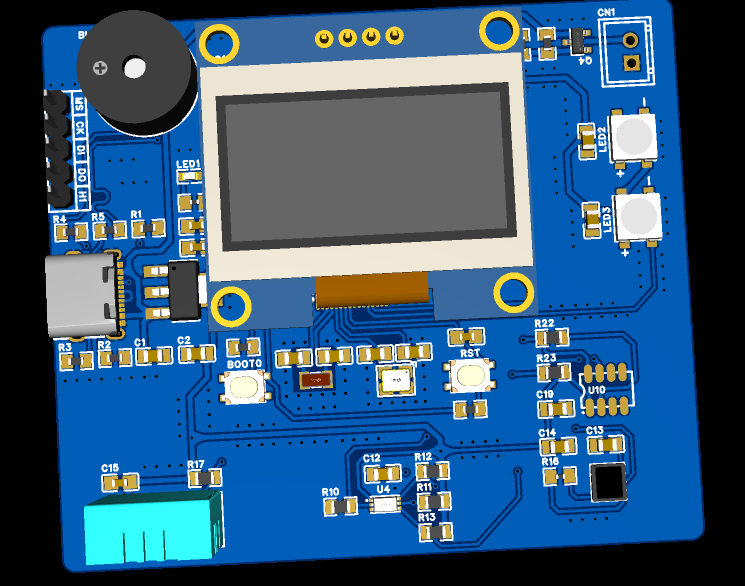

二.模拟题分析

三.准备工作

1.文件提取

离线模式——>文件——>(大压缩包)导入专业版——>导入文件;(小压缩包)提取库文件。

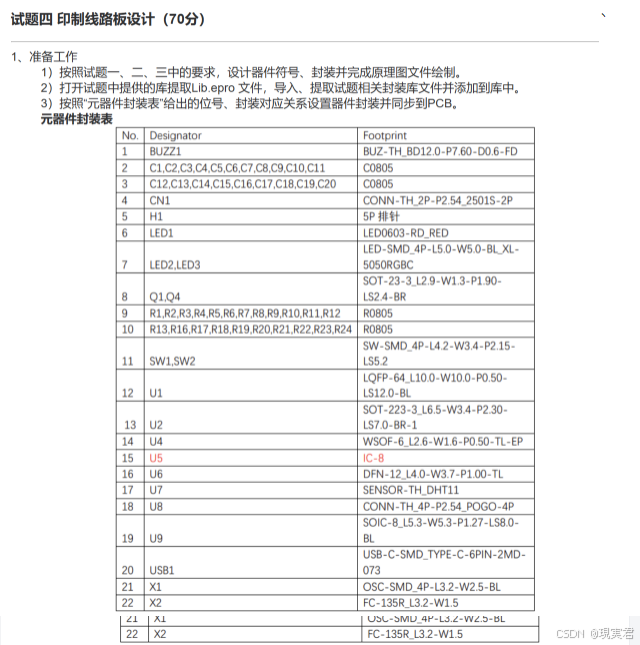

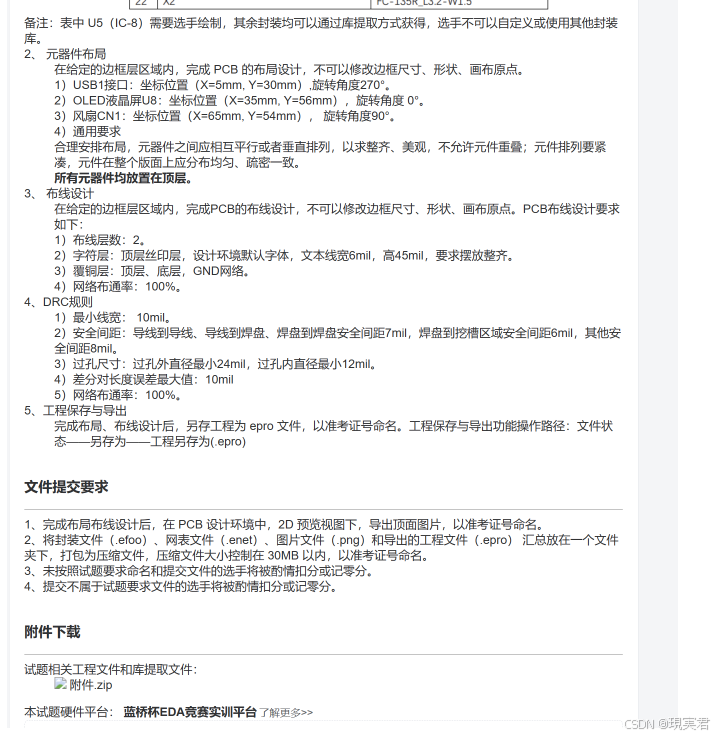

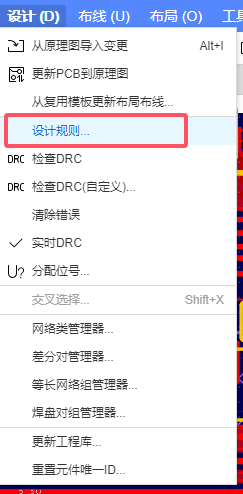

2.布线规则

先根据参赛文件改布线规则(间距,线宽)。

按照题目要求设置DRC规则

9.差分检查设置

四.最终工程

五.经验分享

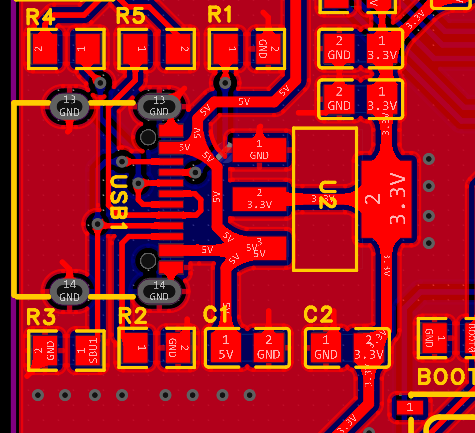

1.分模块布局,特别是电源模块要按照充电口的位置来安放

2.电源线路粗细大概得记得12mil配1A,22mil配1.5A。

3.电机电路和电源电路的电流比较大需要粗一点

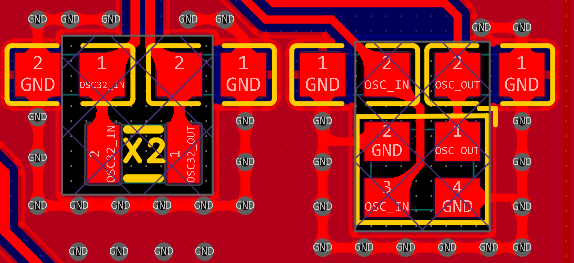

4.STM32有外部高速晶振,这个晶振要求距离芯片近一点,而且要差分等长布线。还有就是要求没有其他信号干扰。

5.心中要明白模块电路那里进那里出,并且放置滤波电容时要从大到小依次滤波。

6.为了方便布线,芯片一般都放置在板框中央部分,因为4边的引脚都需要使用

7.记得画丝印,不然软件要骂人的,特别是调试用的引脚

8.

9.散热孔和焊盘:合理放置散热孔以提高PCB板的散热效率;优化焊盘的设计和布局以提高焊接质量和PCB板的可靠性。

10. 1mil=0.0254mm,如果懒就按下Q,可以将设计mm和mil相互转换。

11.布线不允许出现直角和锐角,尖端放电。

12.走线尽量不要穿贴片电阻电容期间。不安全。

13.布线过程

1、先布电源线

2、再布每个模块内的短线

3、再布短的电源线

4、然后从芯片先拉出来几根线,也可以从模块拉出来几根线,看看具体应该怎么走,尽量快!

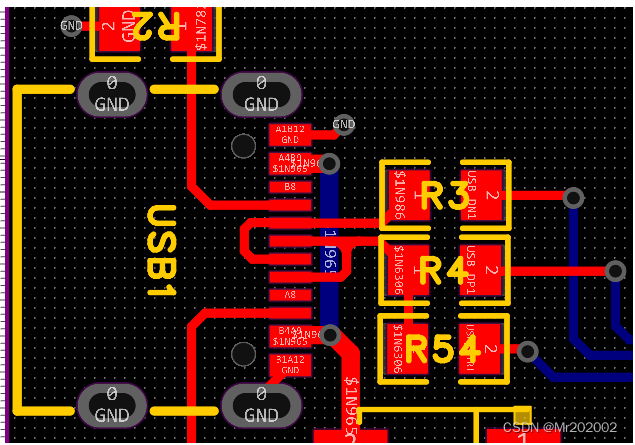

14.USB要走差分线,能不打孔尽量不要打孔。如果长度不够可以走蛇形线,进行等长处理。

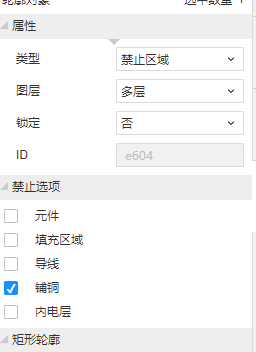

15.继电器底部禁止铺铜!!

16.TYPEC接口一般不要打孔可以类似于这样进行处理,一般用下面两个

17.一根线一般最多打两个过孔,不要打多,打多了会有影响

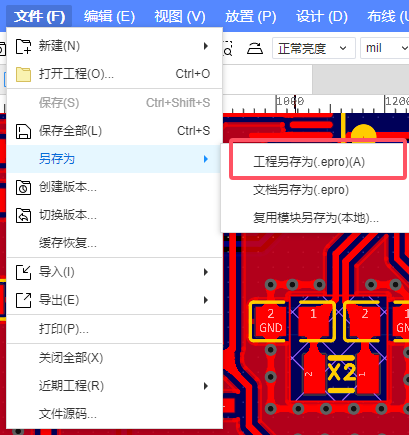

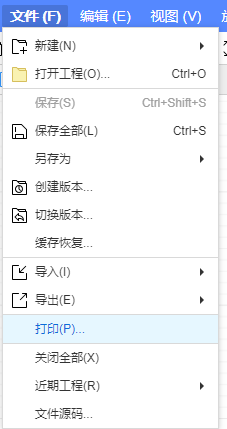

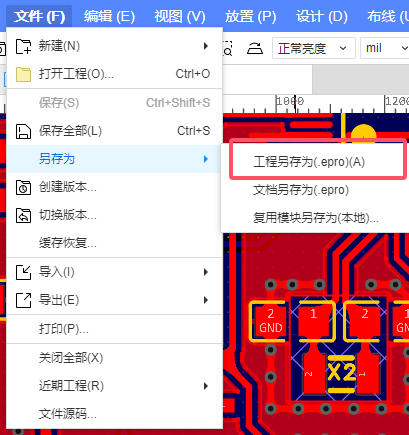

六.导出工程

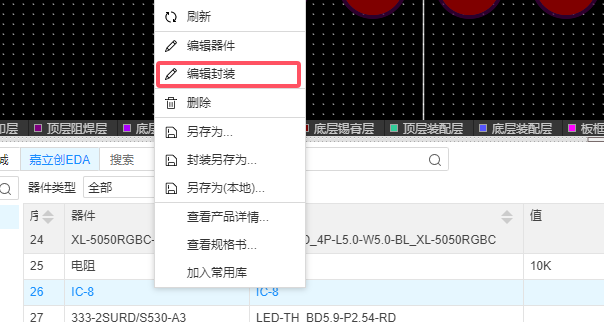

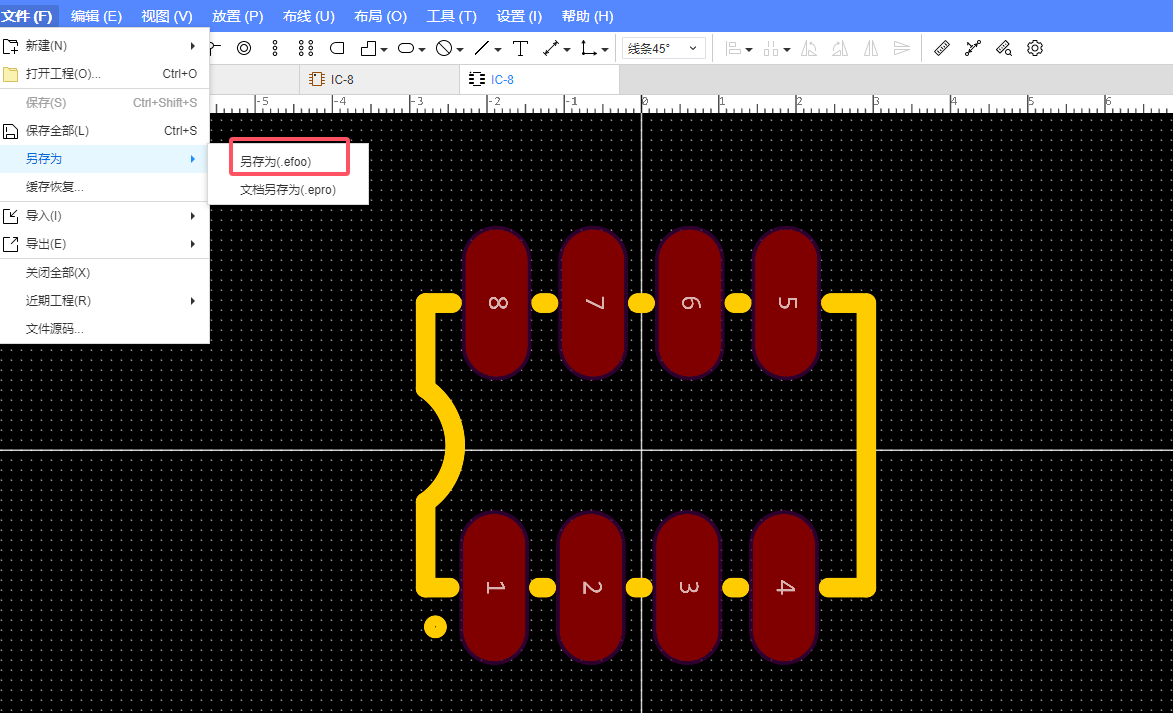

导出封装文件 efoo

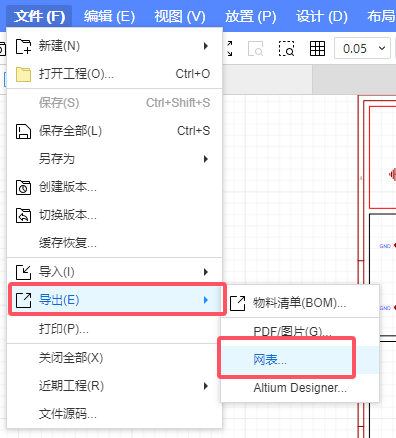

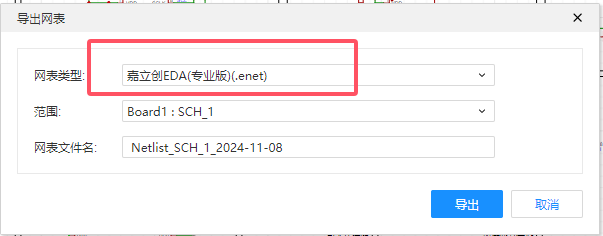

导出网表文件 enet

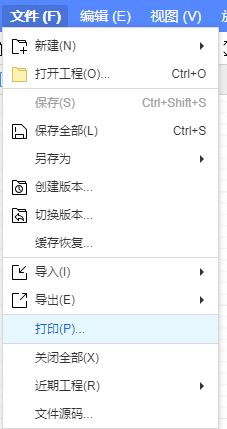

导出图片文件 png

导出工程文件 epro

导出图片文件 png

导出工程文件 epro

9505

9505

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?