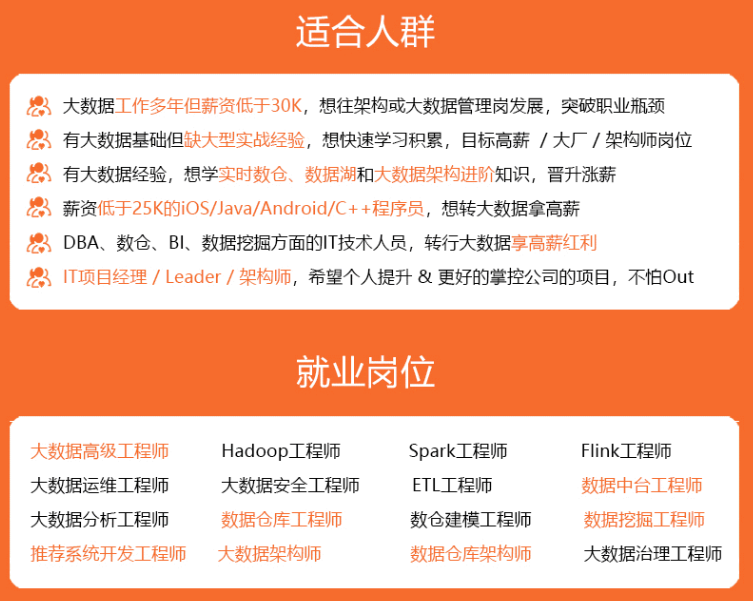

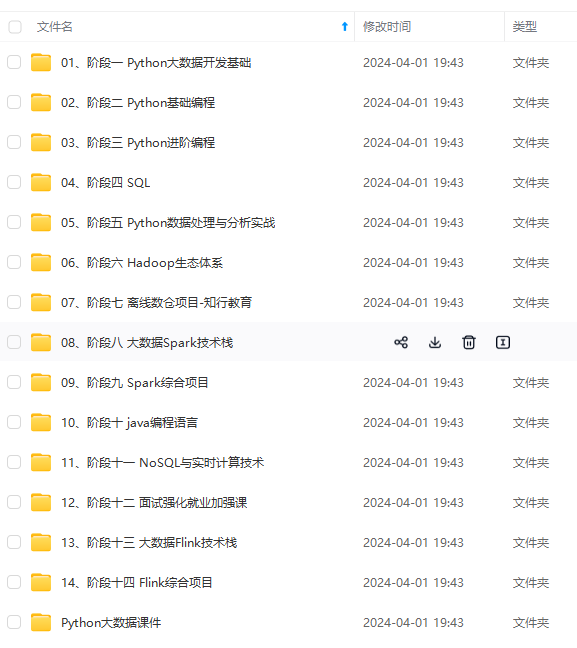

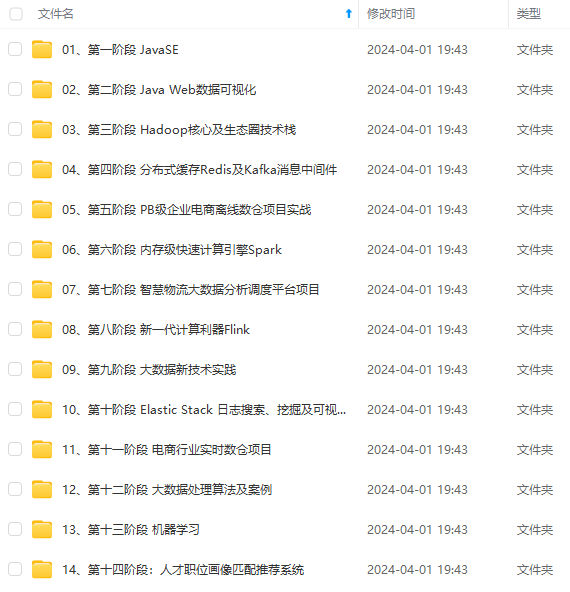

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

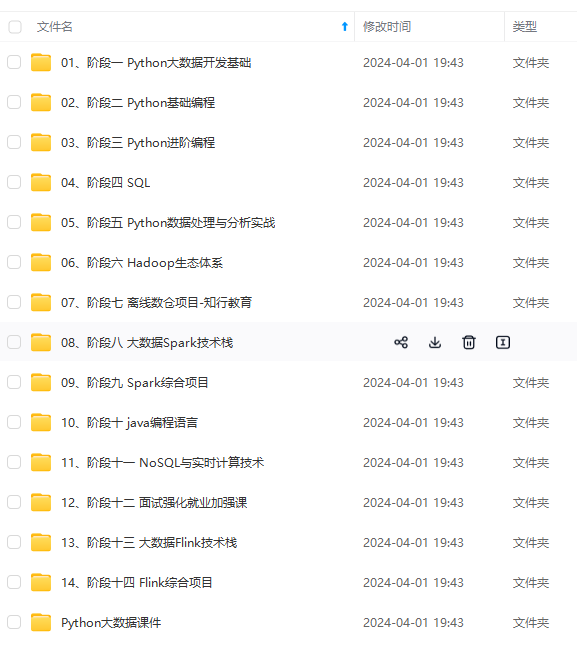

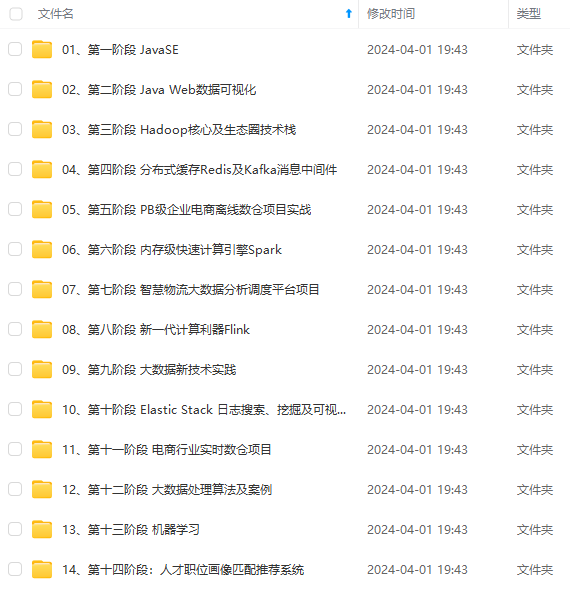

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

示例输入:

input A ,

input B ,

input C

示例输出:

output wire L

参考代码:

`timescale 1ns/1ns

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

module sel_exp(

input A ,

input B ,

input C ,

output wire L

);

data_sel m1(C,1’b0,A,B,1’b0,1’b0,L);

endmodule

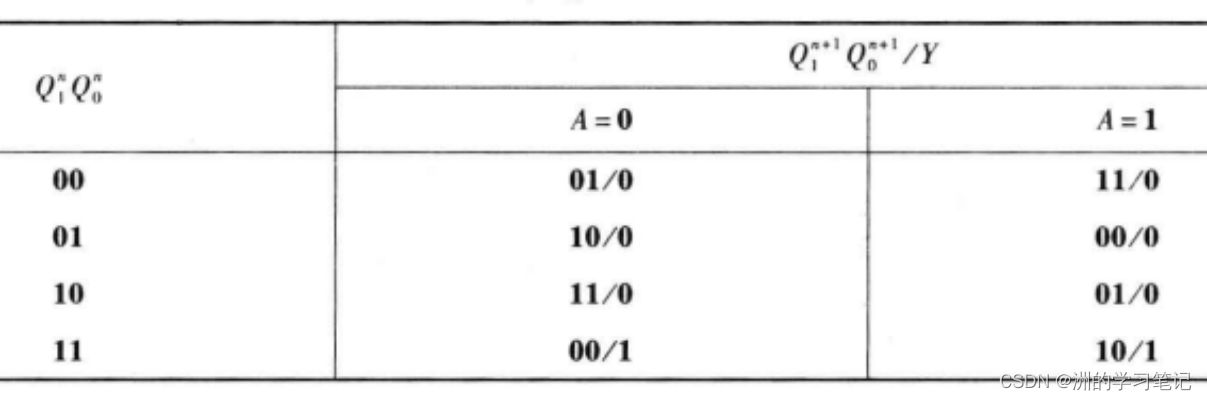

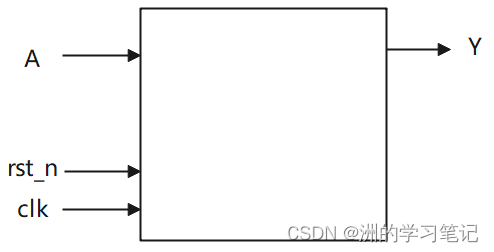

## Q2:根据状态转移表实现时序电路

问题描述:某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

电路的接口如下图所示。

示例输入:

input A ,

input clk ,

input rst\_n

示例输出:

output wire Y

参考代码:

`timescale 1ns/1ns

module seq_circuit(

input A ,

input clk ,

input rst_n,

output wire Y

);

reg[1:0]Q;

initial Q=2’b00;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

begin

Q<=2’b00;

end

else

begin

Q[0]<=~Q[0];

Q[1]<=(A)&(Q[1]^Q[0])|A&(Q[1]^Q[0]);

end

end

assign Y=Q[1]&Q[0];

endmodule

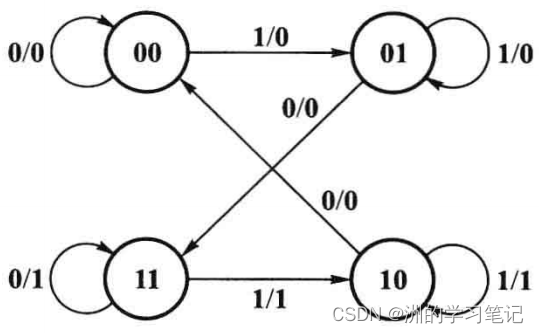

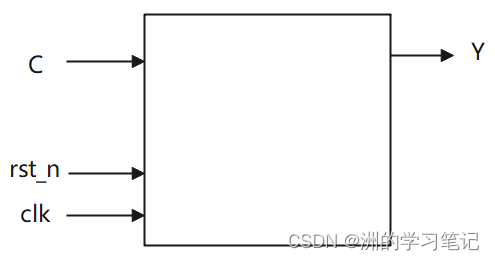

## Q3:根据状态转移图实现时序电路

问题描述:某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

电路的接口如下图所示,C是单bit数据输入端。

示例输入:

input C ,

input clk ,

input rst\_n

示例输出:

output wire Y

参考代码:

`timescale 1ns/1ns

module seq_circuit(

input C ,

input clk ,

input rst_n,

output reg Y

);

parameter [1:0] st0 = 2’b00,

st1 = 2’b01,

st2 = 2’b10,

st3 = 2’b11;

reg [1:0] cst,nst;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cst <= 2'b00;

nst <= 2'b00;

end

else

cst <= nst;

end

always@(\*) begin

case(cst)

st0:begin

nst = (C==1) ? st1 : st0;

end

st1:begin

nst = (C==1) ? st1 : st3;

end

st2:begin

nst = (C==1) ? st2 : st0;

end

st3:begin

nst = (C == 1) ? st2 : st3;

end

default:

nst = st0;

endcase

end

always @(\*) begin

if(((cst == st2) && C) || (cst == st3) )

Y = 1'b1;

else

Y = 1'b0;

end

endmodule

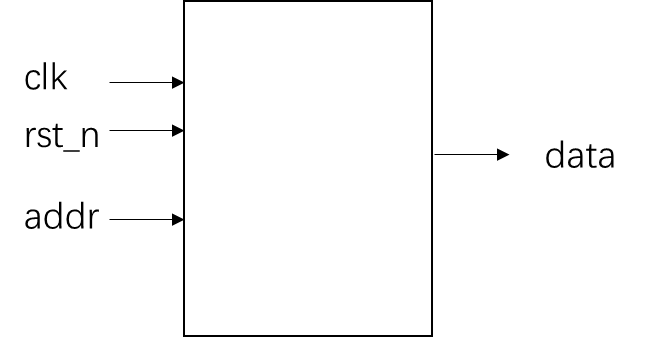

## Q4:ROM的简单实现

问题描述:实现一个深度为8,位宽为4bit的ROM,数据初始化为0,2,4,6,8,10,12,14。可以通过输入地址addr,输出相应的数据data。

接口信号图如下:

输入描述:

clk:系统时钟

rst\_n:异步复位信号,低电平有效

addr:8bit位宽的无符号数,输入到ROM的地址

输出描述:

data:4bit位宽的无符号数,从ROM中读出的数据

参考代码:

`timescale 1ns/1ns

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg [3:0] romreg[7:0];

integer i;

always @ (posedge clk or negedge rst_n)

begin

if (~rst_n) begin

romreg[0]<=4'd0;

romreg[1]<=4'd2;

romreg[2]<=4'd4;

romreg[3]<=4'd6;

romreg[4]<=4'd8;

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

存中…(img-oS03ybHn-1714995333533)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

2447

2447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?