基于LPM_ROM的4位乘4位无符号数乘法器

前言

本次实验所用软件为Quartus||9.0,所用板载为EPF10K20T144-4。

注意事项

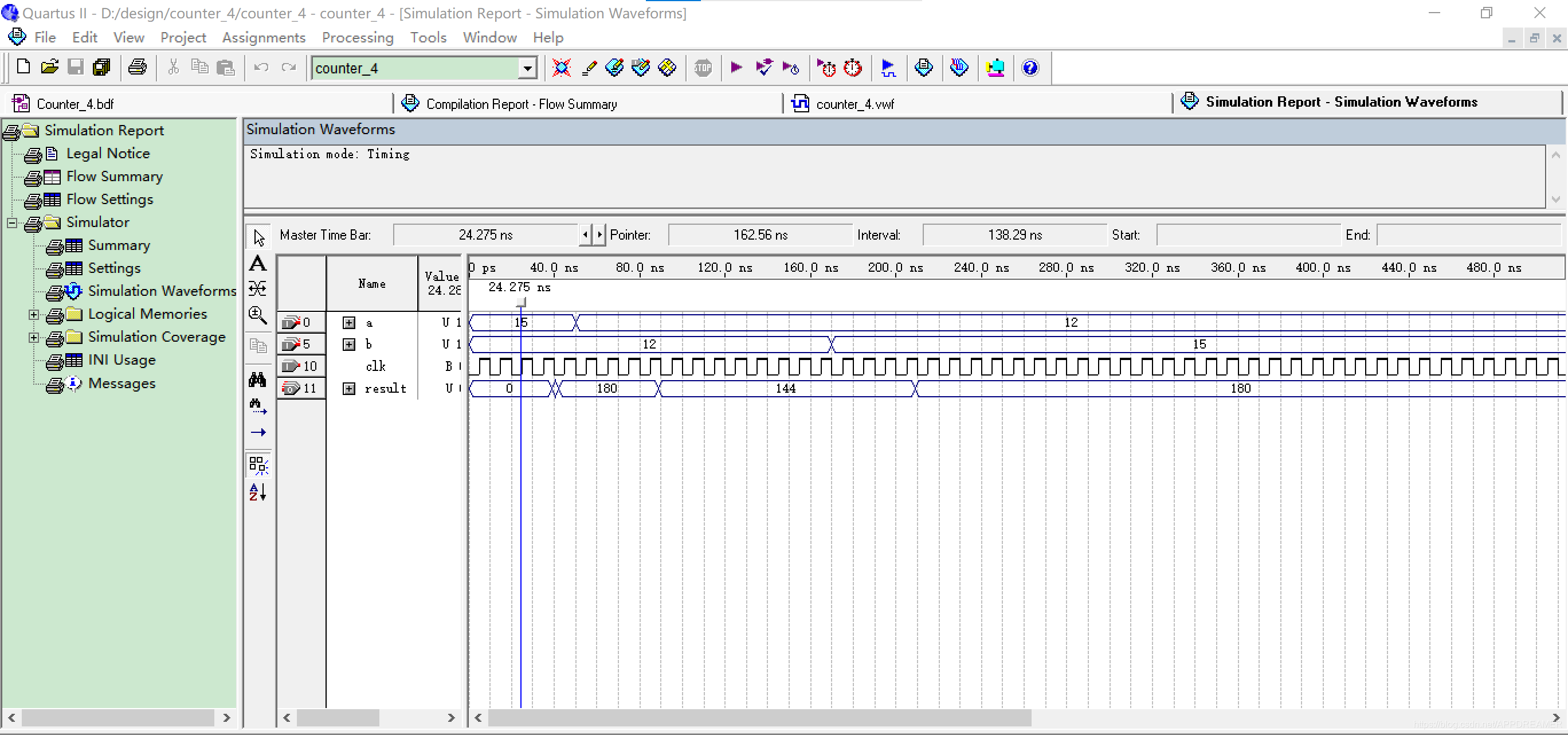

(1)本博客中所创建电路的的时序仿真可能出现问题,问题在于开头一段的0数据和52数据

(2)在向板载烧入程序的时候时记得安装驱动。

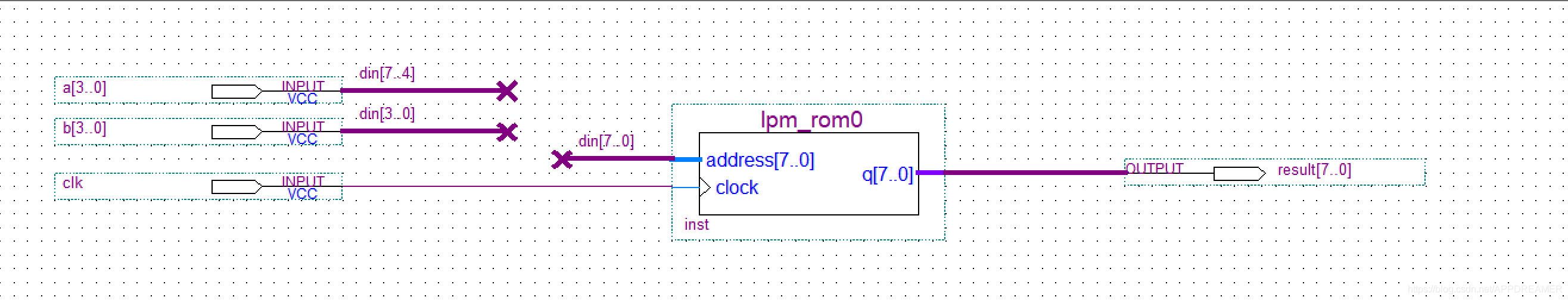

搭建仿真电路图

1、创建Block Diagram/Schematic File文件

2、搭建自己的电路图

(注:电路原理图如下)

2.1第二步可能遇到的问题:

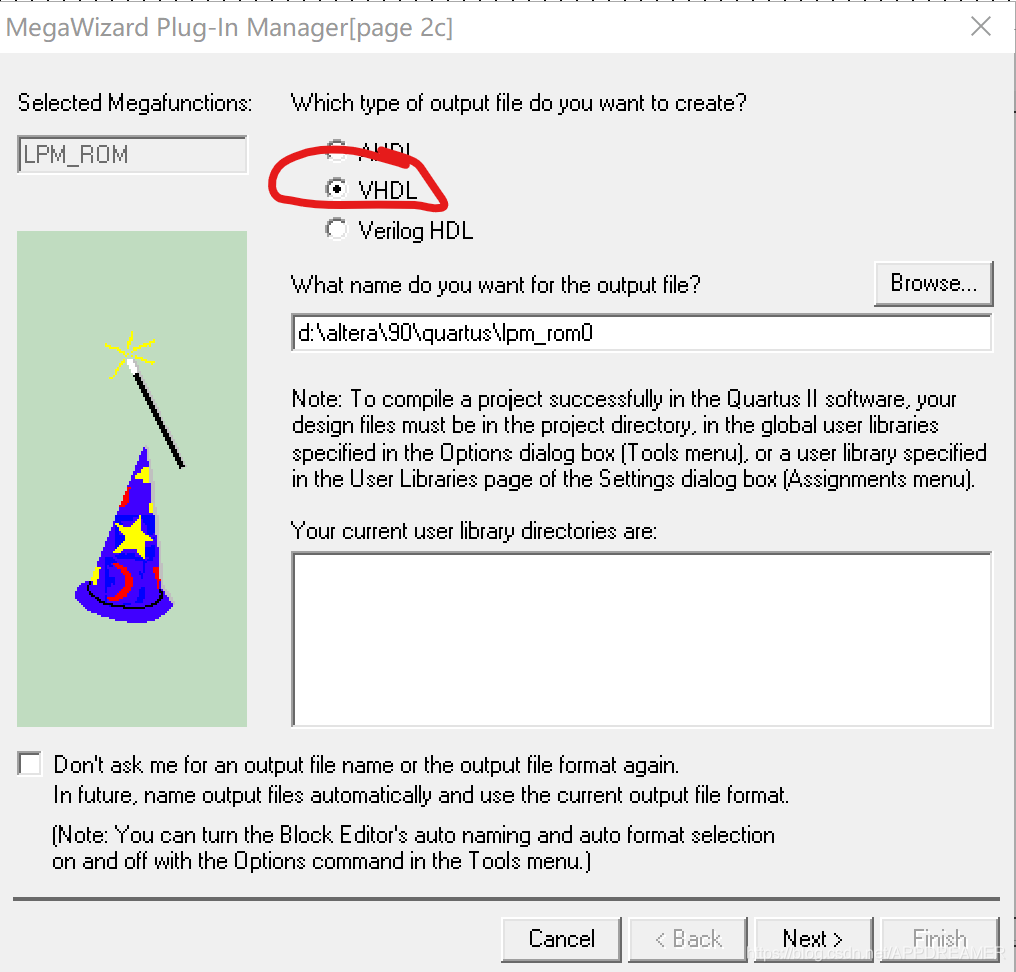

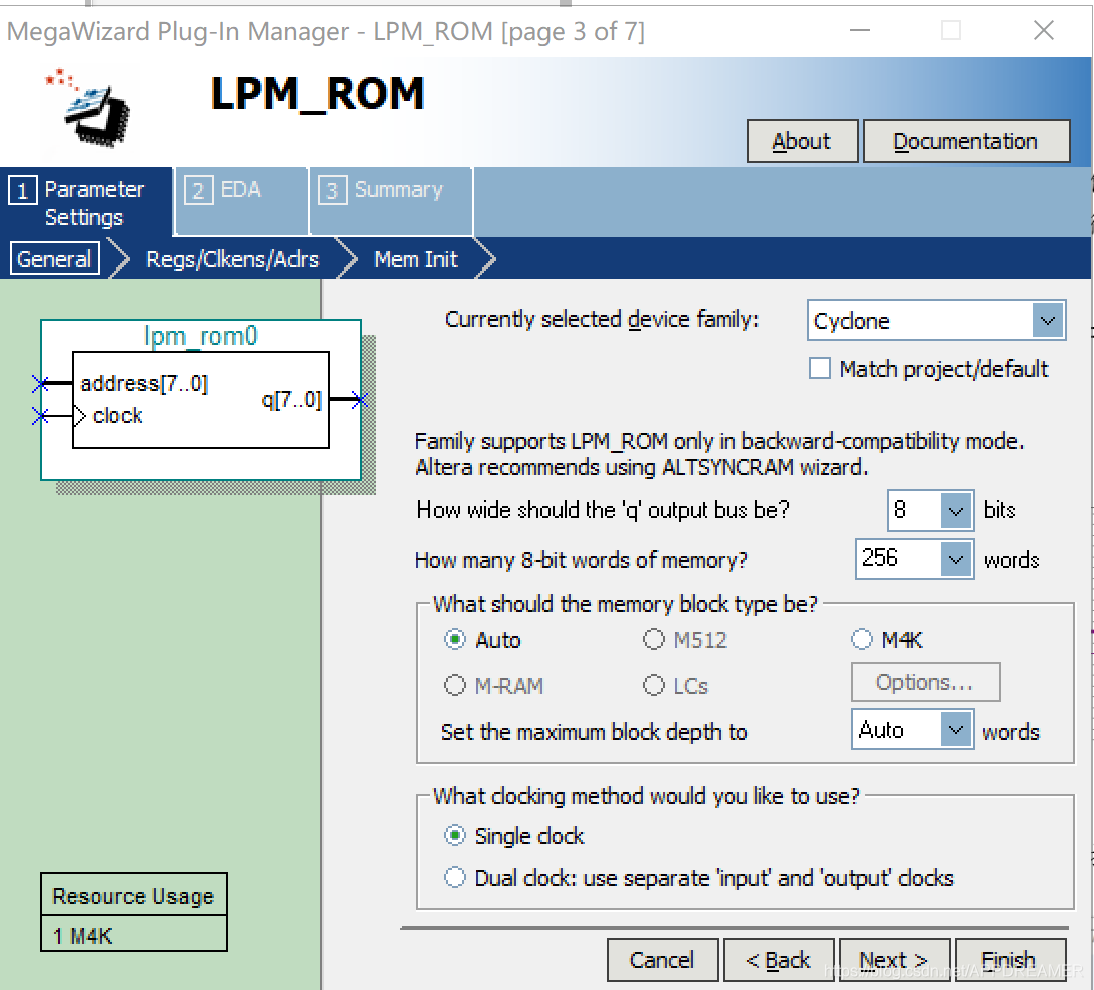

问题一:不会设置lpm_rom元件

解决办法:按如下步骤执行即可(注:下图步骤只到需要生成.mif文件,不是lpm_rom元器件设置的全部步骤)

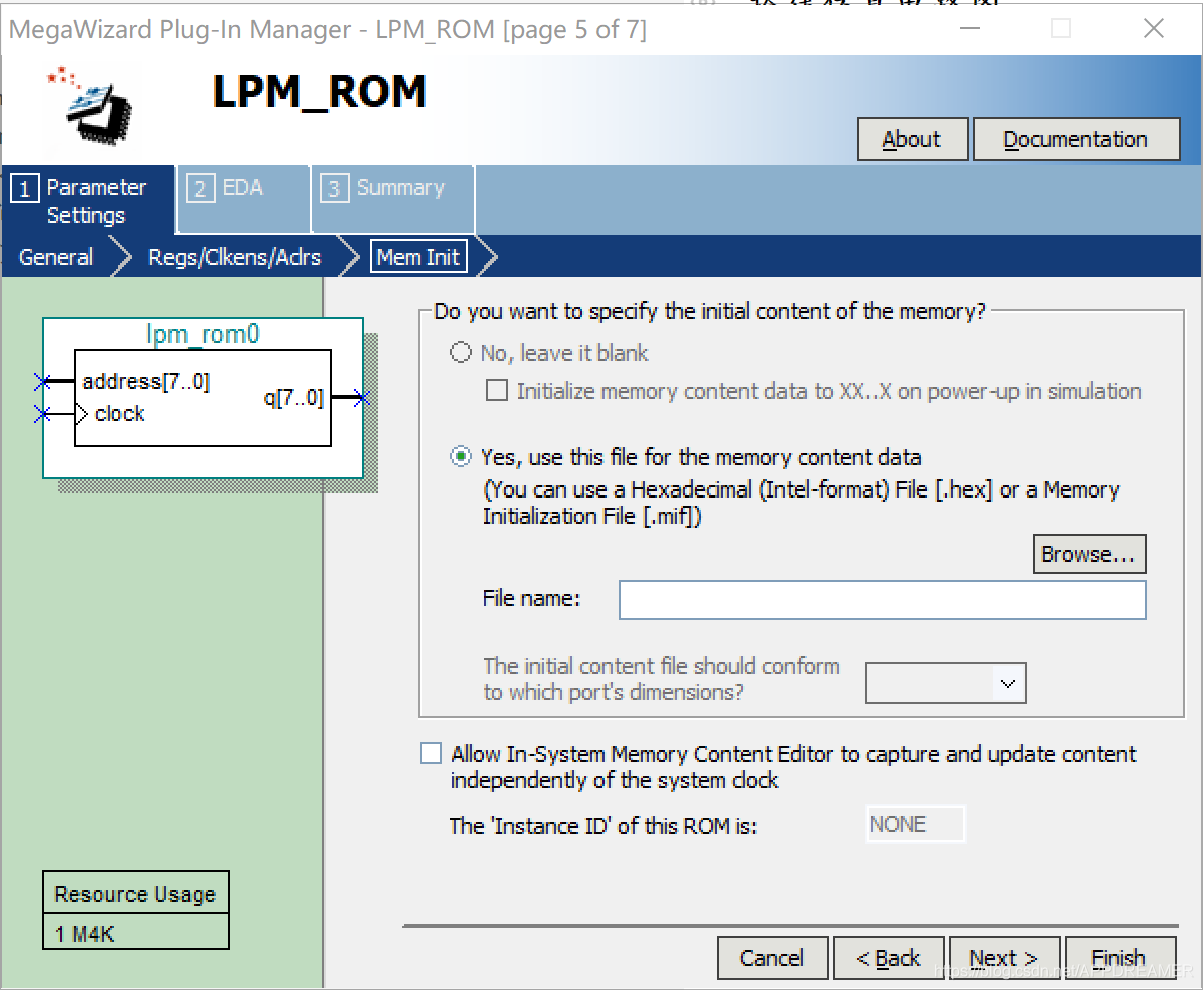

问题二:在逻辑单元lpm_rom时无法找到.mif文件

问题原因:没有生成.mif文件

解决办法:生成.mif文件

(注:生成.mif文件步骤一:new->Memory lntialization File)

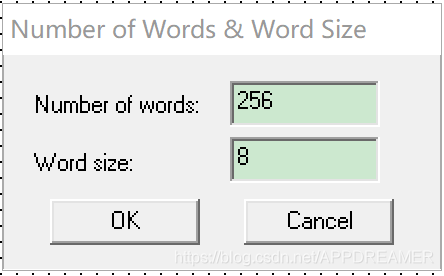

(注:生成.mif文件步骤二:在弹出的界面上输入如下界面的数字,输入完后点击“OK”)

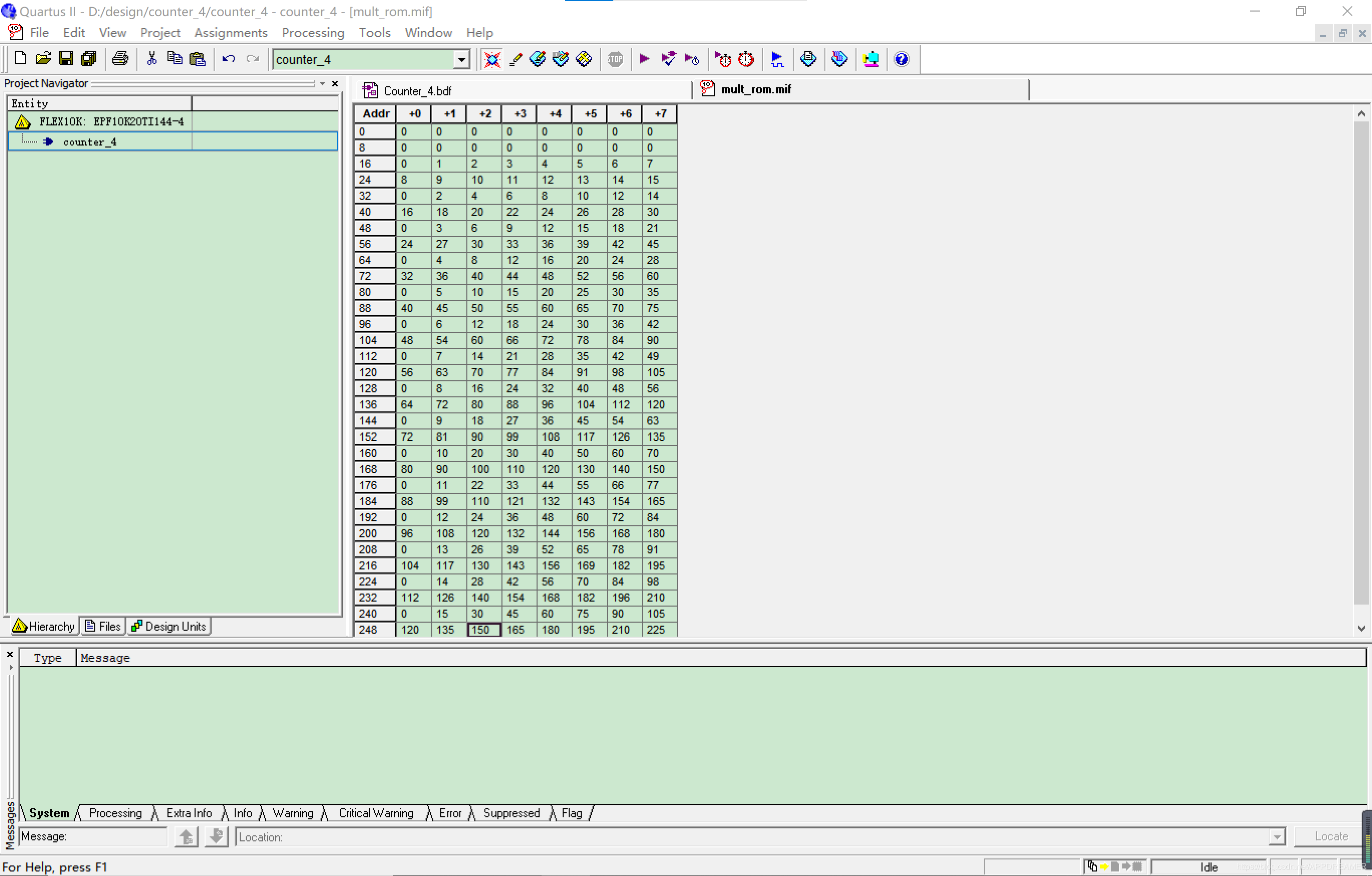

(注:生成.mif文件步骤三:在创建的.mif文件下输入如下界面的数字)

(注:生成文件所需数据由以下此段C程序产生,程序产生的数据可直接复制粘贴到.mif文件中)

#include<stdio.h>

int main(){

int i,j;

for(i=0;i<=15;i++){

for(j=0;j<=15;j++){

printf("%d ",i*j);

if(j==7||j==15){

printf("\n");

}

}

}

return 0;

}

(注:生成.mif文件步骤四:保存并命名文件为mult_rom.mif)

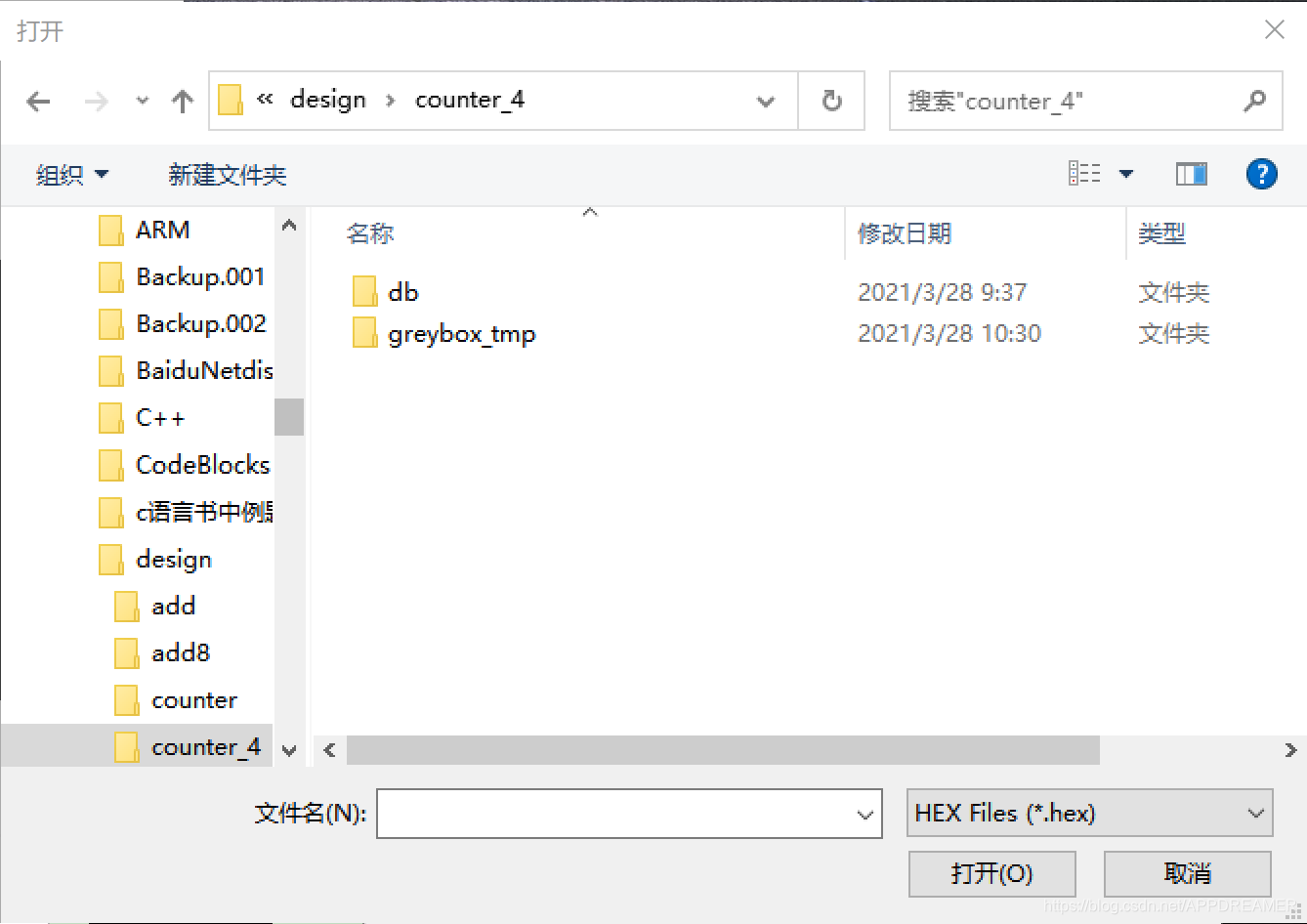

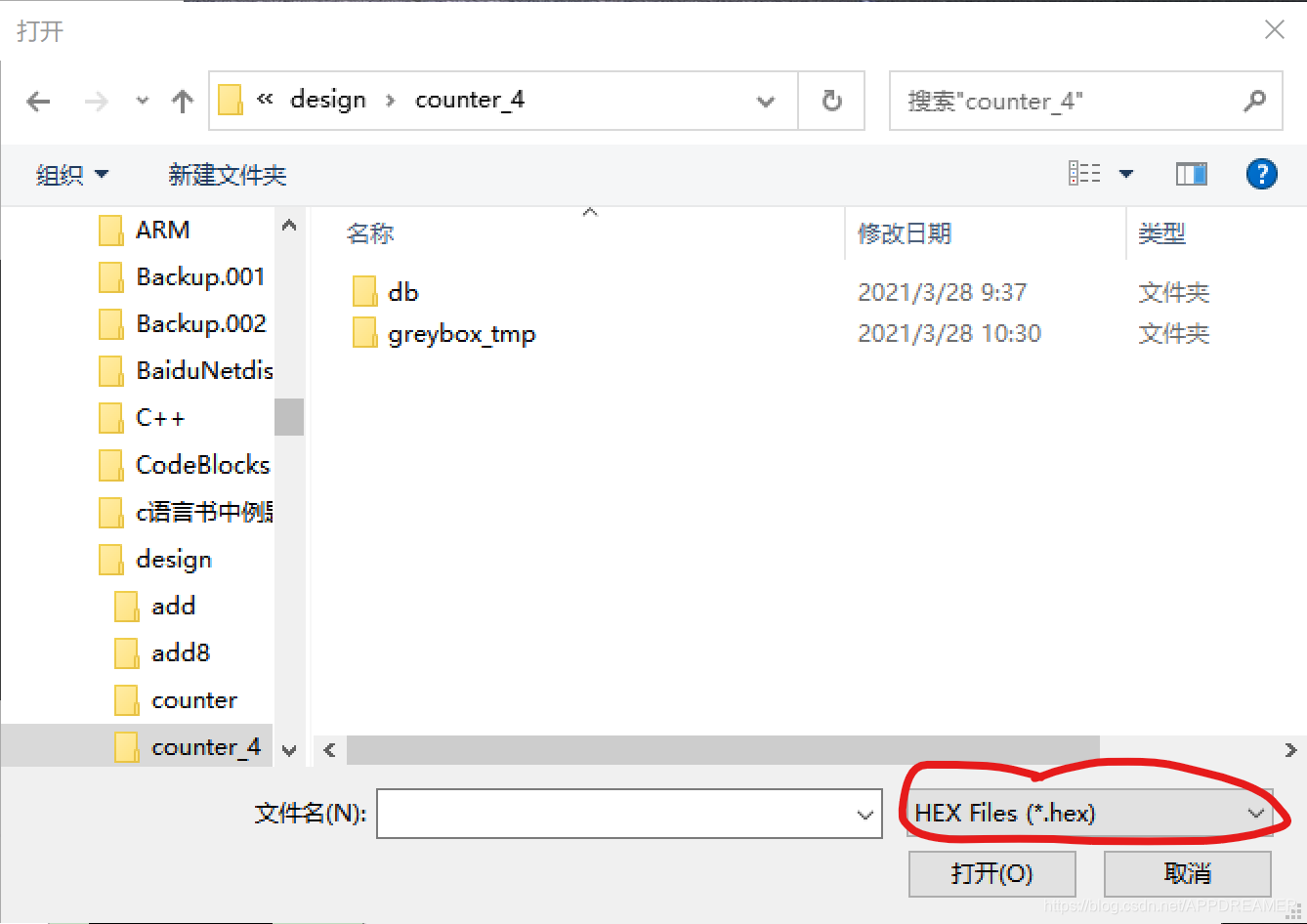

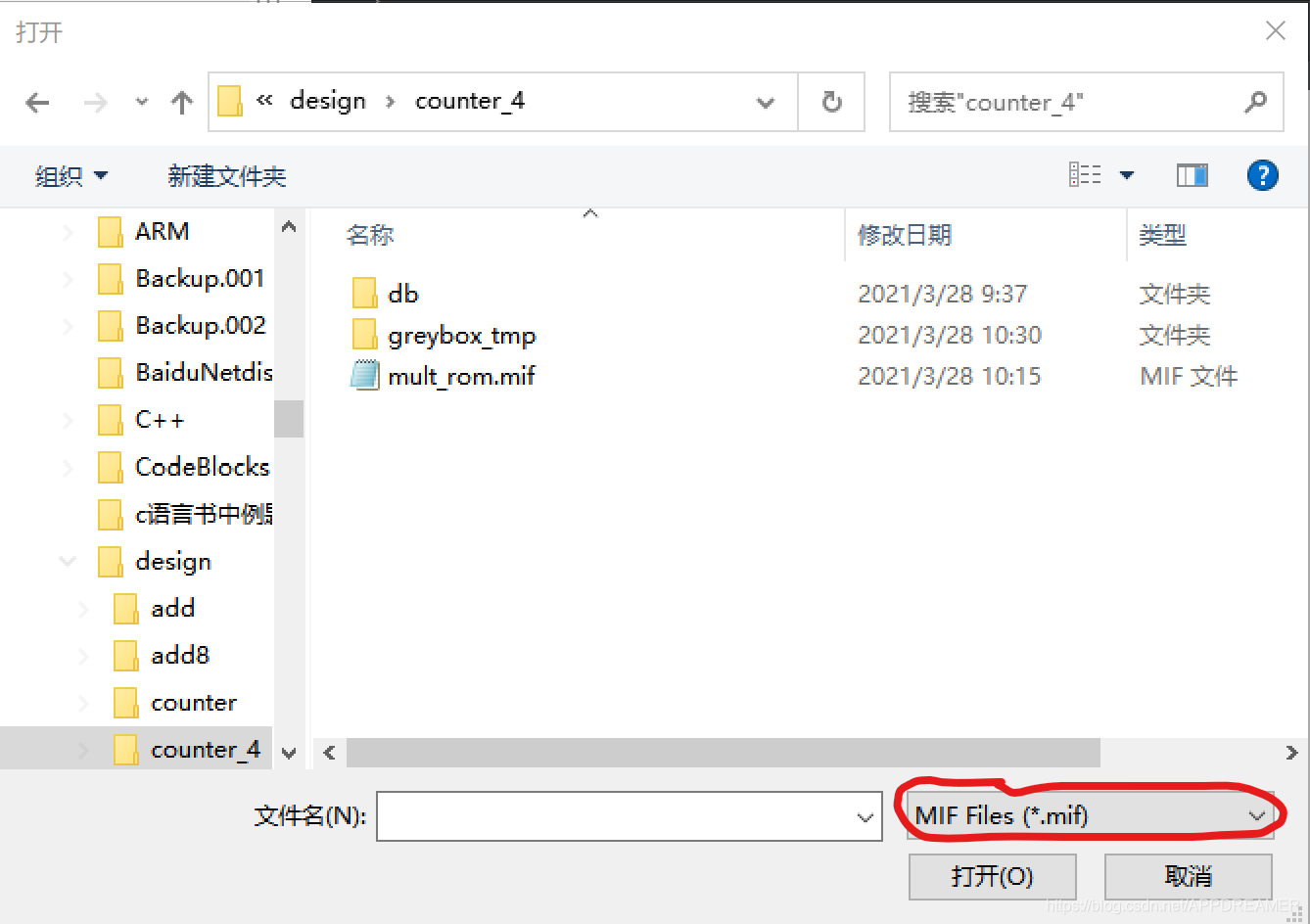

问题三:已经生成了,但在lpm_rom逻辑单元的时候找不到mult_rom.mif文件。

问题原因:没有更改搜索文件格式

解决办法:更改搜索文件格式位MIF Files(*.mif)。

3、对电路图进行编译。

对所搭建电路进行时序仿真

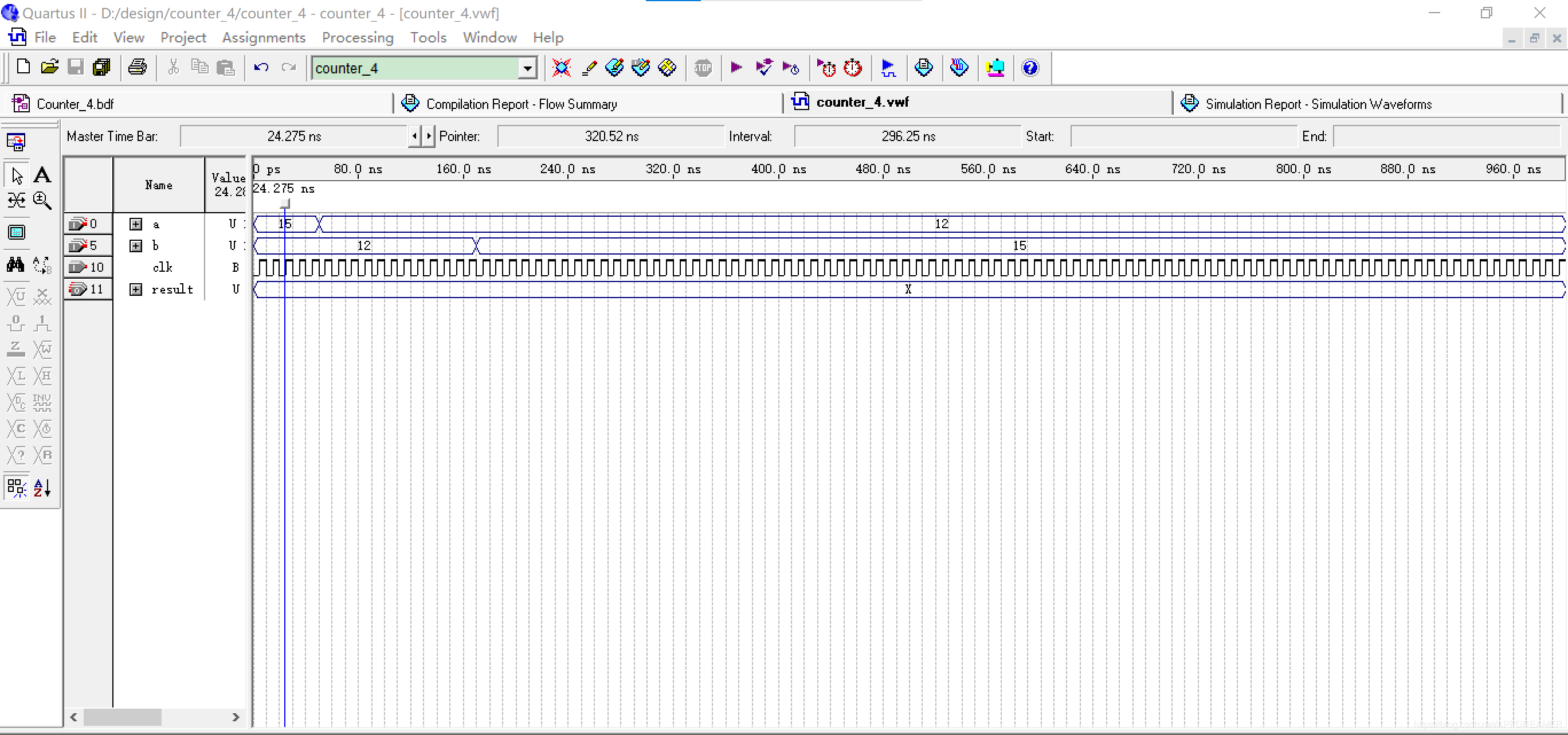

1、创建Vector Waveform File文件。

2、如图所示设置仿真引脚和初始化数值

3、生成仿真文件

对所搭建电路进行板载测试

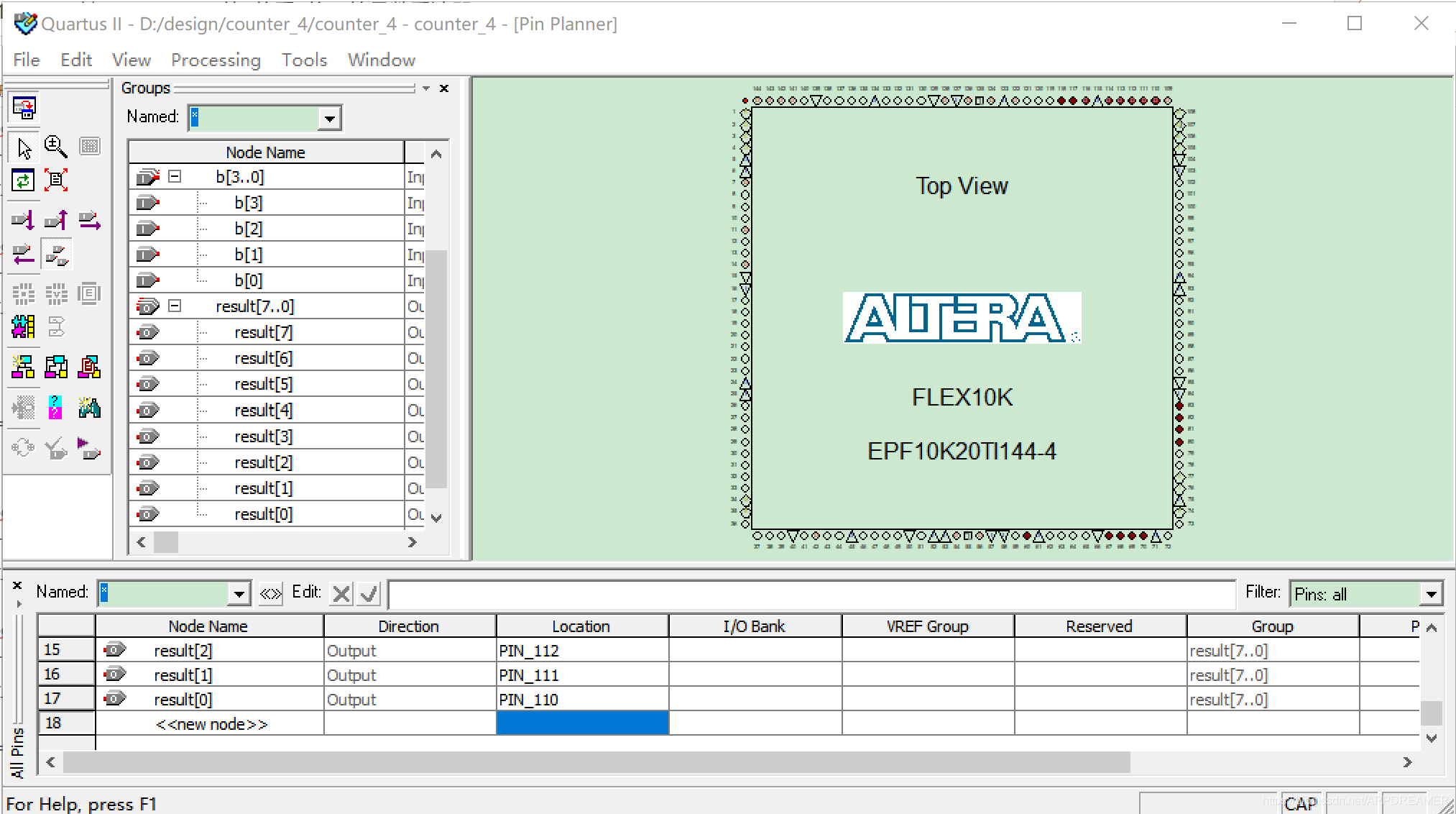

1、设置板载与电路图相对应的引脚

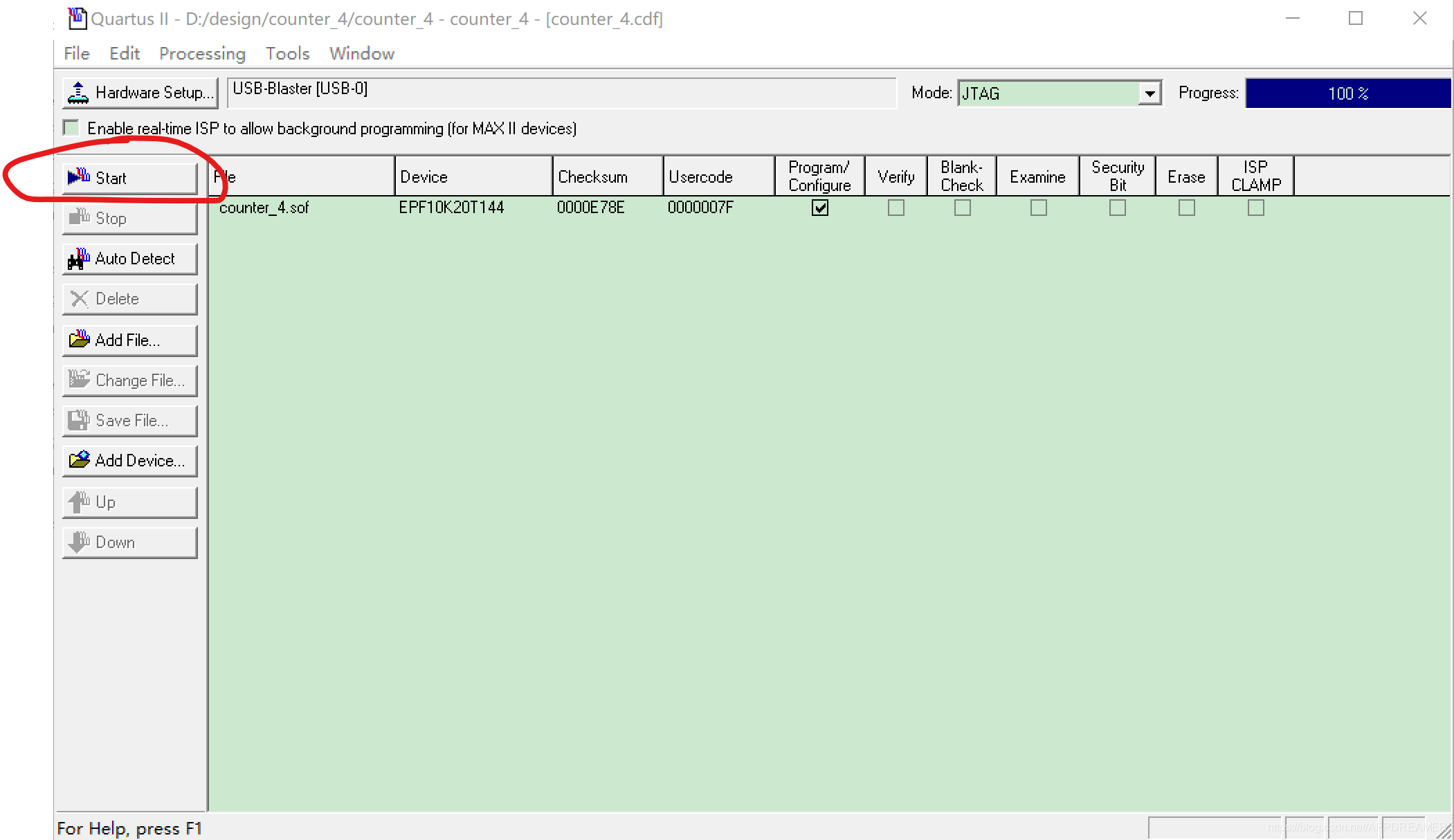

2、将电路图烧入板载

3、验证成功

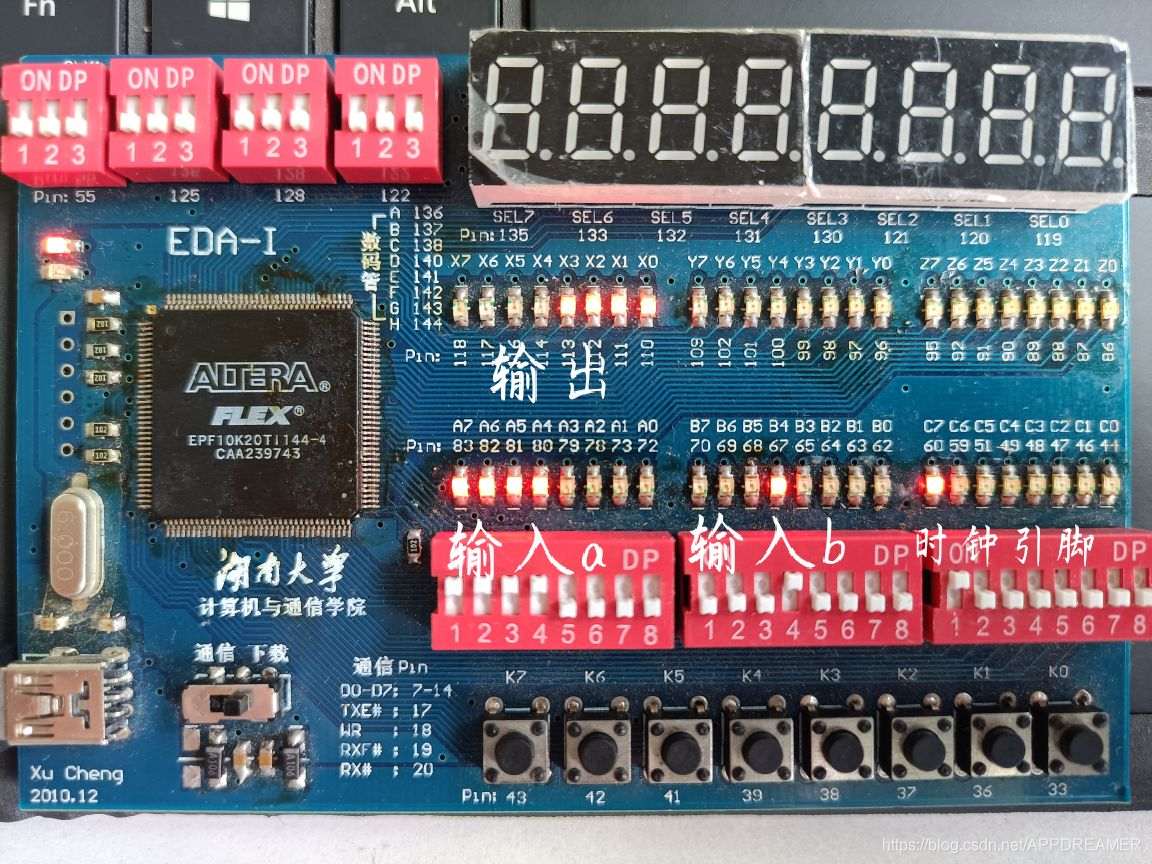

(注:板载使用方法一:输入a对应引脚PIN_83—PIN_80;输入b对应引脚PIN_70—PIN_69;)

(注:板载使用方法二:输出result对应引脚PIN_118—PIN_110;时钟对应引脚PIN_60;)

(注:板载使用方法三:调好输入后,要得到输出,必须调整clk的电位使其在0、1之间改变;)

本文档详细介绍了如何使用Quartus 9.0和EPF10K20T144-4板载资源,基于LPM_ROM构建4位乘4位无符号数乘法器。重点讨论了lpm_rom元件的设置方法,包括.mif文件的生成和在电路图中的应用。通过C程序生成乘法表数据,并将其导入.mif文件,最终完成电路编译、时序仿真及板载测试。文中还列举了在搭建和测试过程中可能遇到的问题及其解决方案。

本文档详细介绍了如何使用Quartus 9.0和EPF10K20T144-4板载资源,基于LPM_ROM构建4位乘4位无符号数乘法器。重点讨论了lpm_rom元件的设置方法,包括.mif文件的生成和在电路图中的应用。通过C程序生成乘法表数据,并将其导入.mif文件,最终完成电路编译、时序仿真及板载测试。文中还列举了在搭建和测试过程中可能遇到的问题及其解决方案。

1647

1647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?