Design Compiler(以下简称DC)是Synopsys公司用于做电路综合的核心工具,可以将HDL描述的电路转换为基于工艺库的门级网表。本系列主要介绍综合相关的知识以及DC工具的使用。

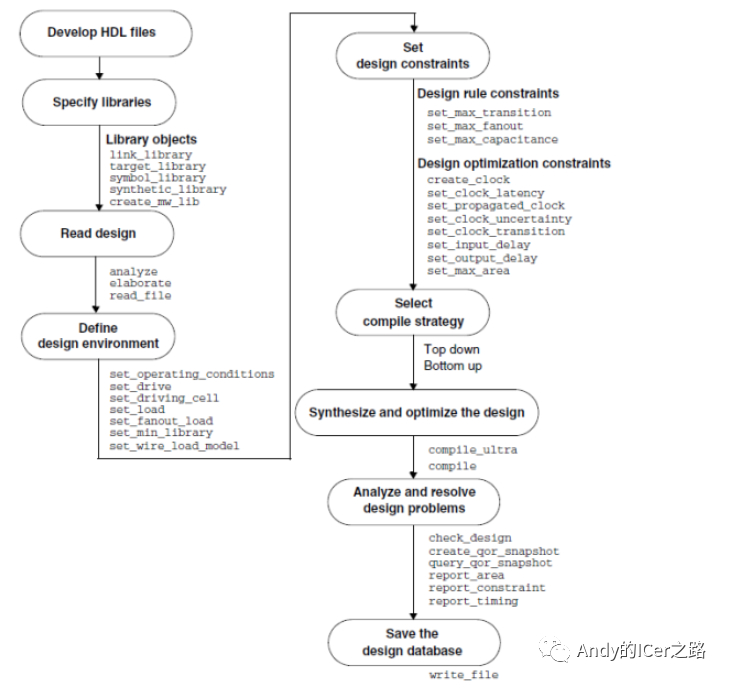

整体的综合流程图

三、定义设计环境

定义对象包括工艺参数(温度、电压等),I/O 端口属性(负载、驱动、扇出), 统计 wire-load 模型,设计环境将影响设计综合及优化结果。

四、设置设计约束

设计约束包括设计规则约束和优化约束,设计规则约束(design rule constraint)由工艺库决定,在设计编译过程中必须满足,用于使电路能按功能要求正常工作。设计优化约束定义了DC要达到的时序和面积优化目标,该约束由用户指定,DC在不违反设计规则约束的前提下,遵循此约束综合设计。

五、选择编译策略

对于层次化设计,DC中有两种编译策略供选择,分别为top down 和bottom up。在top down策略中,顶层设计和子设计在一起编译,所有的环境和约束设置针对顶层设计,虽然此种策略自动考虑到相关的内部设计,但是此种策略不适合与大型设计,因为top down编译策略中,所以设计必

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?