Reference: Xilinx FPGA权威设计指南

Xilinx Vivado集成开发环境为设计者提供了通过设置FPGA内对象的属性实现对FPGA内对象进行约束的物理约束。这些约束包括:

(1)I/O约束,如位置和I/O标准

(2)布局约束,如单元的位置

(3)布线约束,如固定的布线

(4)配置约束,如配置模式

对于大多数的物理约束,其语法格式表示为:

set_property <property><value><object_list>Note:当XDC中出现非法的约束条件时,Vivado提示“Critial Warning”信息,其中也包括对设计中没有的对象进行约束的情况。Xilinx推荐设计者仔细查看严重警告信息,以保证所有的约束条件都是正确的。

1. I/O约束 -- 约束输入输出引脚的位置和电气标准

I/O约束的命令如下所示:

set_property PACKAGE_PIN G13 [get_ports reset]

set_property IOSTANDARD LVCMOS18 [get_ports reset]2. 网表约束

网表约束用于设置网表对象,如端口,引脚,网络或者单元。这样,编译工具可以以特殊的方式处理它们。

(1)CLOCK_DEDICATED_ROUTE

该属性控制时钟信号的布线方式。当没有使用专用时钟资源时,该属性可以设置为FALSE。该值允许Vivado工具使用通用的布线资源,将来自输入端口的时钟连接到一个全局时钟资源,如BUFG和MMCM等。

(2)MARK_DEBUG

在RTL中的一个网络上设置该属性,使得在网表中可以看到该网络。这样,允许在编译流程中,在任意点将该网络连接到逻辑调试工具中。

(3)DONT_TOUCH

在叶子单元(Leaf Cell),层次化单元或者网络对象上设置DONT_TOUCH,用于在网表优化的过程中保护这些网表对象。该属性用于:

1)禁止优化由DONT_TOUCH声明的网络。

2)禁止合并人工复制的逻辑。

这里书中提到一个注意点就是:由于Vivado集成设计环境不能实现平坦化(flatten)逻辑层次,因此在实现设计时避免在层次单元上使用DONT_TOUCH。在综合时,使用KEEP_HIERARCHY保持逻辑层次。但是,我发现Vivaod工具在实现时,其实是默认先将设计整个flatten进行整体优化,然后再重新生成原HIERARCHY结构的。很奇怪,也就是Vivado集成设计环境是能实现flatten逻辑层次优化的。

(4)LOCK_PINS

LOCK_PINS是一个单元的属性,用于在逻辑LUT的输入(I0,I1,I2,...)和LUT物理引脚(A6,A5和A4)之间指定映射关系。普遍的用法是,将时序上有严格要求的LUT输入强制映射到最快的A6和A5的物理输入。如下是将I1映射到A6,I0映射到A5.

set myLUT2 [get_cells u0/u1/i_365]

set_property LOCK_PINS {I0:A5 I1:A6} $myLUT2

get_property LOCK_PINS $myLUT23. 布局约束

将布局约束应用到单元,用于控制这些单元在FPGA元器件内的位置。布局约束包括:

(1)LUTNM

唯一的字符串名字应用到两个LUT,用于控制它们在单个LUT位置上的布局。不像HLUTNM和LUTNM,可以用于组合属于不同层次单元的LUT。

(2)HLUTNM

唯一的字符串名字应用到相同层次上的两个LUT,用于控制它们在单个LUT位置上的布局。

(3)PROHIBIT

禁止布局到某个位置。

(4)PBLOCK

将一个逻辑块约束到FPGA元器件内的一个物理区域内。PBLOCK是一个只读单元属性,即其单元所分配到Pblock的名字。

(5)PACKAGE_PIN

在目标元器件封装的一个引脚上指定一个设计端口的位置。

(6)LOC

将来自网表的一个逻辑元素放置到FPGA元器件内的一个位置外。

(7)BEL

将来自网表的一个逻辑元素放置到FPGA元器件上一个切片内一个指定的BEL上。

在Vivado工具中,提供了两种类型的布局。

(1)Fixed Placement,由设计者通过指定的布局:手工布局,XDC约束,对加载到存储器中的设计的一个单元对象上使用IS_LOC_FIXED或者IS_BEL_FIXED约束。

(2)Unfixed Placement,由实现工具所执行的布局。

1)以下是将一个BRAM放置在RAMB18_X0Y10的位置,并且将其位置固定。

set_property LOC RAMB18_X0Y10 [get_cells u_ctrl0/ram0]2)以下是将一个LUT放置到一个切片内的C5LUT BEL的位置,并且将BEL的分配固定。

set_property BEL C5LUT [get_cells u_ctrl0/lut0]3)以下是将输入总线寄存器放置到ILOGIC单元中。这样做的目的是为了更短输入延迟。

set_property IOB TRUE [get_cells mData_reg*]4)以下是将两个小的LUT组合到一个LUT6_2中,它使用了O5和O6输出。

set_property LUTNM L0 [get_cell {u_ctrl0/dmux0 u_ctrl0/dmux1}]5)以下是用于阻止布线器使用第一列的BRAM

set_property PROHIBIT TRUE [get_sites {RAMB18_X0Y* RAMB36_X0Y*}]4. 布线约束

布线约束应用于网络对象,用于控制它们的布线资源。

固定布线:固定布线是用于锁定布线的一种机制。锁定一个网络布线包含3个网络属性。

1)ROUTE: 只读网络属性

2)IS_ROUTE_FIXED: 用于将整个布线标记为固定。

3)FIXED_ROUTE: 一个网络的固定布线部分

注意:为了保证一个网络布线是固定的,则布线上的所有单元必须预先也是固定的。

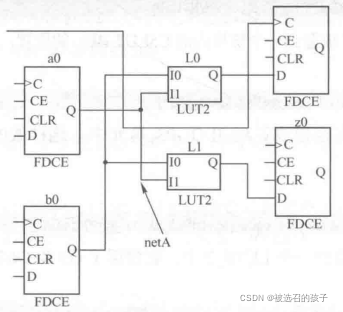

如对下图1中电路中的netA的布线进行固定。

图 1

set_property LOC SLICE_X0Y47 [get_cells {a0 L0 L1}]

set_property BEL CFF [get_cells a0]

set_property BEL A6LUT [get_cells L0]

set_property BEL B6LUT [get_cells L1]

set_property LOCK_PINS {I1:A4 I0:A2} [get_cells L0]

set_property LOCK_PINS {I1:A3 I0:A2} [get_cells L1]

set_property FIXED_ROUTE {CLBLL_LL_CQ CLBLL_LOGIC_OUTS6 FAN_ALT5 FAN_BOUNCE5 {IMUX_L17 CLBLL_LL_B3} IMUX_L11 CLBLL_LL_A4} [get_nets netA]5. 布局约束实现

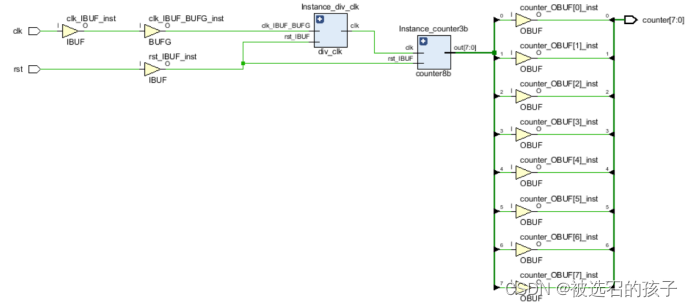

图 2

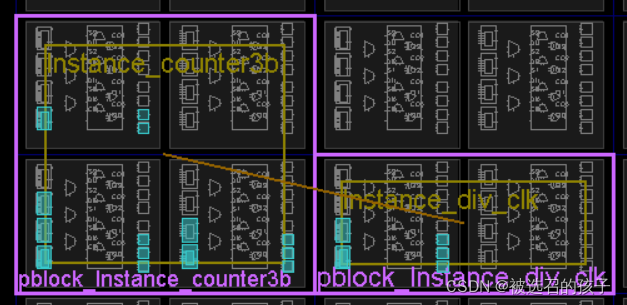

如图2所示的电路,对其进行自动布局实现后的结果如图3所示,白色高亮的器件是Instance_counter3b 实现,蓝色高亮的器件是Instance_div_clk实现。这时,我想让每个module实现靠近一些,因此对其进行布局约束。

图 3

图 4

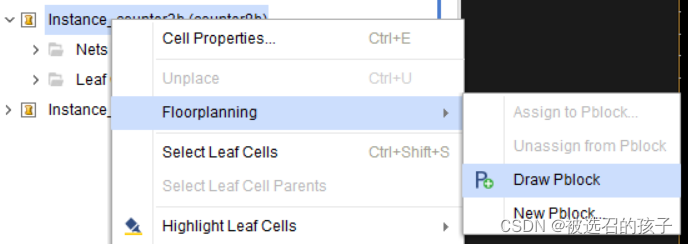

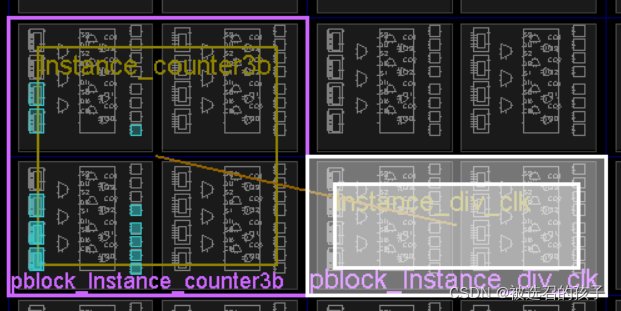

在Netlist菜单栏中,选中相应的Instance,右键出Draw Pblock在Device中进行布局约束。完成的布局约束如图5所示。

图 5

使用Pblock的XDC约束如下所示,首先为Instance创建pblock,然后将具体的Instance与创建的pblock绑定,最后,为pblock添加相应的资源。

create_pblock pblock_Instance_counter3b

add_cells_to_pblock [get_pblocks pblock_Instance_counter3b] [get_cells -quiet [list Instance_counter3b]]

resize_pblock [get_pblocks pblock_Instance_counter3b] -add {SLICE_X0Y8:SLICE_X1Y9}

create_pblock pblock_Instance_div_clk

add_cells_to_pblock [get_pblocks pblock_Instance_div_clk] [get_cells -quiet [list Instance_div_clk]]

resize_pblock [get_pblocks pblock_Instance_div_clk] -add {SLICE_X2Y8:SLICE_X3Y8}最后,经过布局约束后实现的资源分布图如下所示:

图 6

6. 布线约束实现(有些地方还没相通,再研究研究)

7. 配置约束原理

配置约束是全局约束,用于当前设计的比特流生成。其中包含对配置模式的约束。

(1)下面是将CONFIG_MODE设置为M_SELECTMAP

set_property CONFIG_MODE M_SELECTMAP [current_design](2)下面是将元器件的E11和F11引脚设置为电压参考引脚

set_property VREF {E11 F11} [current_design](3)下面是禁止CRC检查

set_property BITSTREAM.GENERAL.CRC Disable [current_design]

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?