1. 序

Video PHY Controller IP是为实现与视频(DisplayPort和HDMI™技术)MAC传输或接收子系统的即插即用连接而设计的。视频MAC层和PHY层的接口是标准化的,能方便的使用共享收发器(transceiver)资源。同时AXI4-Lite接口提供了动态获取收发器(transceiver)状态和控制收发器(transceiver)的功能。Video PHY Controller就是为了能够方便使用串行收发器(serial transceivers)和实现专用域的配置。注意:Video PHY Controller并不符合TMDS specification.

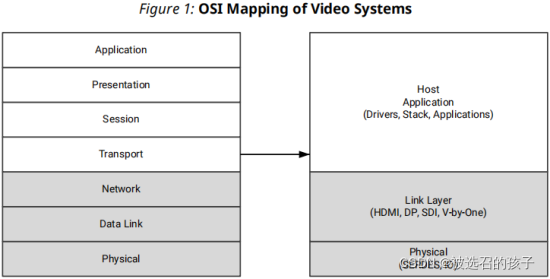

图 1

1.1 支持的功能

(1) 支持DisplayPort和HDMI协议

(2) 对HDMI的特定功能有-HDMI时钟检测(clock detector); 可以使用第4个GT channel作为TX TMDS clock; 用于低线速率数据恢复的非整型数据恢复单元(Non-integer data recovery unit(NI-DRU))

(3) TX和RX的具有独立的线速率(因为在GT channel中,接收器(Receiver)和传输器(Transmitter)可以使用独立的时钟,可以参考之前的GTH结构整理)

(4) 支持单个GT Quad

(5) 支持通过软件来切换PLL(Phase-locked loop)

(6) Transmit and receiver user clocking

(7) 支持收发器动态重配置端口,实现收发器的动态重配置

(8) Advanced clocking support(不是很理解...)

对于支持的功能,要特别注意两点,一是对于Kintex-7,QPLL1/2不支持所有DP的线速率方位,建议对TX路径使用CPLL。二是对于Artix -2 和-3 devices,因为fabric的限制,所以只支持HDMI 1.4的数据率。

1.2 不支持的功能

(1)不支持Multi-MAC控制

(2)支持混合MAC controller,比如HDMI输入,DP输出。

(3)不支持一个例化多个协议接口,比如两个HDMI输入,或者两个HDMI输出。

(4)不能单独使用,需要搭配HDMI或者DP Subsystem IP。

2. 产品规格说明(Product Specification)

Video PHY Controller core是为了配置和使用收发器(transceivers).通过标准化的接口和软件配置串行收发器的功能,简化了串行收发器(Serial transceiver)的使用。

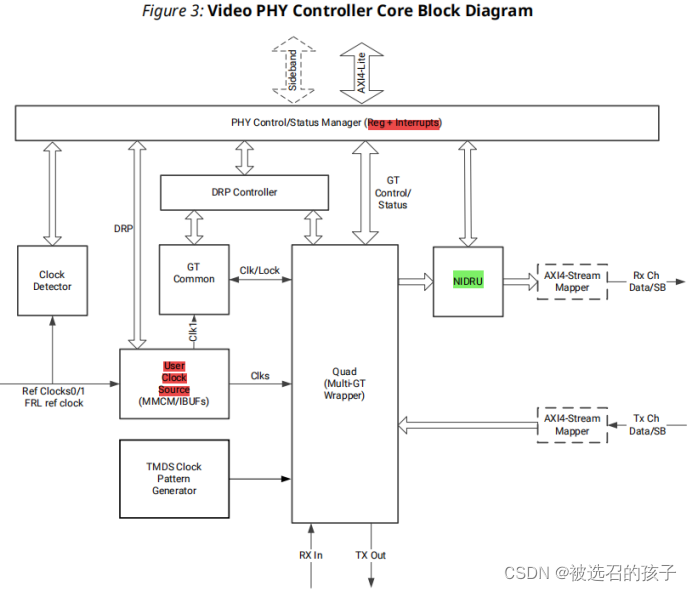

图 2

上图所示,是Video PHY Controller的基本结构图,主要由以下功能块构成。

(1)PHY Control/Status Manager:该功能块管理AXI4-Lite接口协议,处理内存映射和中断。

(2)DRP Controller:该功能块控制AXI4-Lite接口和GT DRP,MMCM/PLL之间的握手交互,当完成握手后,一个新的动态重配置事务(DRP transaction)产生。

(3)User Clock Source:该功能块由GT的时钟输入buffers和为GTs生成USRCLK和USRCLK2。当TX buffer被旁路(bypassed)时,一个MMCM(mixed-mode clock manager)基于TX/RXOUTCLK生成所需要的时钟。该功能也会产生HDMI 1.4/2.0 TX Subsystem和HDMI 1.4/2.0 RX Subsystem需要的video clocks,差分或者单端时钟信号。该功能块buffers RX TMDS CLK并将它转换成差分或者单端时钟输出。

这里要注意,除了GTPE2外的串行收发器(transceiver),它们的最大时钟频率为297MHz,GTPE2的最大时钟频率为148.5MHz。这意味着GTPE2不能支持video clock大于148.5MHz的视频格式。

(4)GT Common:该功能块控制串行收发器(serial transceiver)的COMMON primitive.

(5)AXI4-Stream Mapper:该功能块将GT的输入输出数据转换成AXI4-Stream协议的数据格式。

(6)NI-DRU:该功能块用于当线速率过低时,数据恢复。在HDMI中,当RX的TMDS clock低于特定的GT类型的阈值要求时,NI-DRU就会被使能。

对于GTXE2的阈值是:QPLL=74.125MHz, CPLL = 80.000MHz; 对于GTPE2的阈值是: PLL0/1 = 80.000MHz; GTHE3, GTHE4, 和GTYE4的阈值是:QPLL0=61.250MHz, CPLL = 50.00MHZ。QPLL1没有在NI-DRU中使用。

注意,NI-DRU需要额外的固定参考时钟去给低线速率的数据,进行数据恢复。该时钟可以和FRL的参考时钟相同。

(7)TMDS Clock Pattern Generator:当使用第4个GT Channel作为TX TMDS clock时,当模块被使能。该模块连接到第4个GT Channel,提供GT channel发送TMDS clock的模板。

2.1 端口介绍

2.2.1 时钟和复位端口

个人认为时钟端口是Video PHY Controller的核心,因为在GTH结构整理时钟输入的。理清各种输入参考时钟的关系和输出时钟的功能,对于HDMI和DP接口设计中知道GT是可以由多个参考有很大的必要性。

(1)mgtrefclk0_pad_(p/n)_in:该差分参考时钟对端口是在Advanced Clock mode没有使能或者GTREFCLK0被选择作为HDMI的输入时钟源时产生。

(2)mgtrefclk1_pad_(p/n)_in:该差分参考时钟对端口是在Advanced Clock mode没有使能或者GTREFCLK1被选择作为HDMI的输入时钟源时产生。

(3)mgtrefclk0_in:该单端参考时钟端口是在Advanced Clock mode使能时产生。

(4)mgtrefclk1_in:该单端参考时钟端口是在Advanced Clock mode使能时产生。

(5)mgtrefclk(0/1)_odiv2_in:这两对差分参考时钟对端口在Advanced Clock mode使能,且GTREFCLK0/1其中之一被作为输入时钟时产生,ODIV2输出必须被配置成除以1的输出(divided-by-1)[除以1??,不应该二分频的吗]

(6)gtnorthrefclk(0/1)_in: 这两对差分参考时钟对端口在Advanced Clock mode使能,或者GTNORTHCLO0/1其中之一被作为输入时钟时产生。来自当前Quad垂直方向上的上一个Quad,具体参考GTH结构整理。

(7)gtsouthrefclk(0/1)_in: 这两对差分参考时钟对端口在Advanced Clock mode使能,或者GTSOUTHREFCLK0/1其中之一被作为输入时钟时产生。来自当前Quad垂直方向上的下一个Quad,具体参考GTH结构整理。

(8)gtnorthrefclk(0/1)_odiv2_in:该差分参考时钟对端口在GTNORTHREFCLK0/1其中之一被作为输入时钟时产生,用于UltraScale和UltraScale+的HDMI。

(9)gtsouthrefclk(0/1)_odiv2_in:该差分参考时钟对端口在GTSOUTHREFCLK0/1其中之一被作为输入时钟时产生,用于UltraScale和UltraScale+的HDMI.

(10)gtnorthrefclk00_in:当Advanced Clock mode使能,或者当GTNORTHREFCLK0被选择作为输入时钟源且QPLL0有效时,该端口产生。

(11)gtnorthrefclk01_in:当Advanced Clock mode使能,或者当GTNORTHREFCLK0被选择作为输入时钟源且QPLL1有效时,该端口产生。

(12)gtnorthrefclk10_in:当Advanced Clock mode使能,或者当GTNORTHREFCLK1被选择作为 输入时钟源且QPLL0有效时,该端口产生。

(13)gtnorthrefclk11_in:(使能情况没有提及),但应该是当Advanced Clock mode使能,或者当GTNORTHREFCLK1被选择作为输入时钟源且QPLL1有效时,该端口产生。

(14)gtsouthrefclk00_in:当Advanced Clock mode使能,或者当GTSOUTHREFCLK0被选择作为输入时钟源且QPLL0有效时,该端口产生。

(15)gtsouthrefclk01_in:当Advanced Clock mode使能,或者当GTSOUTHREFCLK0被选择作为输入时钟源且QPLL1有效时,该端口产生。

(16)gtsouthrefclk10_in: 当Advanced Clock mode使能,或者当GTSOUTHREFCLK1被选择作为输入时钟源且QPLL0有效时,该端口产生。

(17)gtsouthrefclk11_in: 当Advanced Clock mode使能,或者当GTSOUTHREFCLK1被选择作为输入时钟源且QPLL1有效时,该端口产生。

(18)gteastrefclk(0/1)_in:当GTEASTREFCLK0/1其中之一被选择为输入时钟源时,该端口产生。针对于HDMI和GTPE2 devices

(19)gtwestrefclk(0/1)_in:当GTWESTREFCLK0/1其中之一被选择为输入时钟源时,该端口产生。针对于HDMI和GTPE2 devices

(20)drpclk: free runing clock

(21)vid_phy_tx_axi4s_aclk:传输用的AXI4-Stream Link clock的输入端口(用于TX Subsystem到Video PHY)

(22)vid_phy_rx_axi4s_aclk:接受用的AXI4-Stream Link clock的输入端口(用于Video PHY到RX Subsystem)

(23)txoutclk: Video PHY的输出时钟,用于HDMI TX Subsystem的link clock

(24)rxoutclk: Video PHY的输出时钟,用于HDMI RX Subsystem的link clock

(25)tx_refclk_rdy:表明输入的TX的参考时钟是否Locked.

(26)tx_tmds_clk: 单端TX TMDS clock输出

(27)tx_tmds_clk_p/n: 差分TX TMDS clock输出

(28)tx_video_clk: HDMI TX Subsystem的video clock

(29)txrefclk_ceb: TX外部参考时钟IBUFDS选择信号

(30)rx_tmds_clk:单端RX TMDS clock输出

(31)rx_tmds_clk_p/n:差分RX TMDS clock输出

(32)rx_video_clk: HDMI RX Subsystem的video clock

(33)rxrefclk_ceb:RX外部参考时钟IBUFDS选择信号

3. Video PHY Controller Callback Functions

具体参考:

HDMI设计3--HDMI 1.4/2.0 Transmiiter Subsystem IP

HDMI设计4--HDMI 1.4/2.0 Receiver Subsystem IP

261

261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?