在以往的IC之间的源同步当中,发送的信号包括数据流信号,以及随着数据流信号同步的时钟信号,时钟信号在低速传输的情况下:1G以下传输,外部的扰动以及时钟抖动不会太影响数据流的恢复,但是如果时钟信号突破了1G甚至更高的情况下,外界环境中比如EMI的各种影响会引起时钟发生抖动,在高速采样恢复的过程中,这就没办法使用该时钟信号恢复数据,这里就用到了高速Serdes串行接口的恢复办法,将数据和时钟都通过高速线上传输,然后接受端通过PLL从数据流中恢复时钟,即使在传输的线上有轻微抖动,但是时钟和数据同时抖动,同时考虑到收发两处如果共地很难实现这里就要使用到了差分传输技术,将收发两部都设置为差分传输模式,即使不共地,即使传输过程中有轻微扰动,也不会影响从数据流中恢复出时钟信息;那么如何从串行的数据流中恢复出时钟信息呢?

这里就要用到了编码技术,也就是8B10B编码或者6466B编码;

Comma检测:

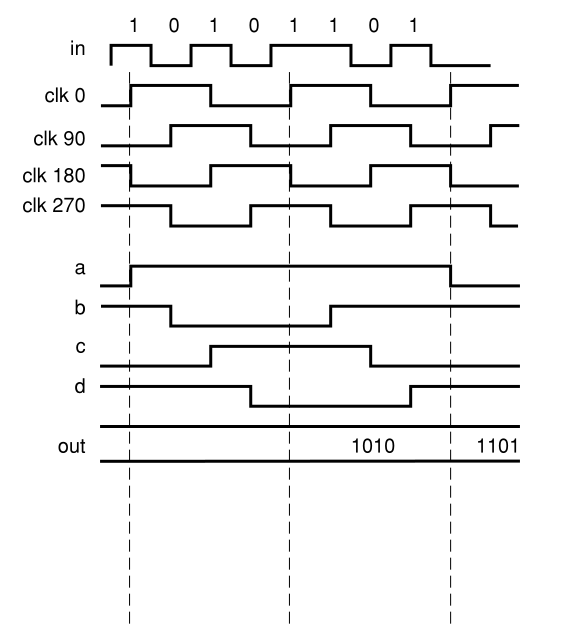

在Serdes上面的高速穿行流转换为多字并行,如何要找到字边界进行对齐,这就需要特殊序列就是Comma检测,而且千万不能和传输的数据冲突,这就是K码,逗号检测,在数据链路同步对齐过程中,逗号检测就是意为从该指定位置开始进行对齐操作,指专用的一两个符号,是特定的序列,是完成串并转换的起始位置,而且逗号序列也必须是唯一的,其他任何传输序列或者传输数据中也不能包含逗号序列,否则容易产生误判。

比如在JESD204B传输中使用K28.5作为逗号。

在很多基于Serdes的高速串行协议中传输数据都是以包的形式进行发送,包包括帧头数据帧尾,在大多数的串行数据链路包中Serdes都需要一种特殊的序列将数据对齐,尤其是在需要恢复时钟的数据包中,必须找到数据恢复和时钟恢复的起始位置,此时就可以将逗号作为起始或者结束的标志,空闲符号是另一个重要概念,在没有数据传输的时候,也就是在串行线上没有数据的时候就发送空闲字符,而进行连续数据传输时就可以确保链路保持对齐,PLL保持恢复的时钟锁定。

在进行高速串行数据如果需要恢复时钟,这里就需要一个参考时钟的概念,这里的参考时钟必须极其精确,ref_clk需要的晶振要求较高。

通常情况下的时钟矫正技术:在时钟校正中,每个MGT包含一个FIFO,然后在使用中,将数据通过高速串行时钟将数据送入FIFO中,然后通过内部的并行时钟将数据从FIFO中读出,这里完成了一个跨时钟域传输,在使用时钟校正中用到了FIFO,用到FIFO就需要考虑到时钟的空满,如果CDR(Clock and Data Recovery)时钟和本地时钟并不完全相同,如果不采取某些手段那么必然会导致FIFO出现空满,为了防止这种情况出现在传输的过程中必须周期性的发送一些可以复制或者可以删除的某些字节以防止FIFO的溢出或不足;

当然如果传输过程中参考时钟发送给收发器双发的时钟信息相同,那么就不需要采用时钟校正。

MGT通道传输的接受FIFO要比传输FIFO深度要大的多,因为需要完成时钟校正和通道绑定,时钟校正在上方已经提及,通道绑定:

就是在某些具体传输过程中,单个的串行链路传输数据容量已经不够满足数据传输容量,这里也就需要通过多个数据传输通道,多个并行的数据传输通道在结果上看就是数据容量扩大了,但是这也就导致数据通道必须对齐,这就是通道绑定;

通道绑定技术就是将多个通道之间的产生的偏斜计算出来然后传输给用户,完成数据对齐

在将数据传输到FIFO中后,从FIFO中读出数据时,会根据具体数据通道的偏斜量根据延迟从FIFO中读出数据,完成数据对齐;

高速串行总线的电平信号及预加重技术

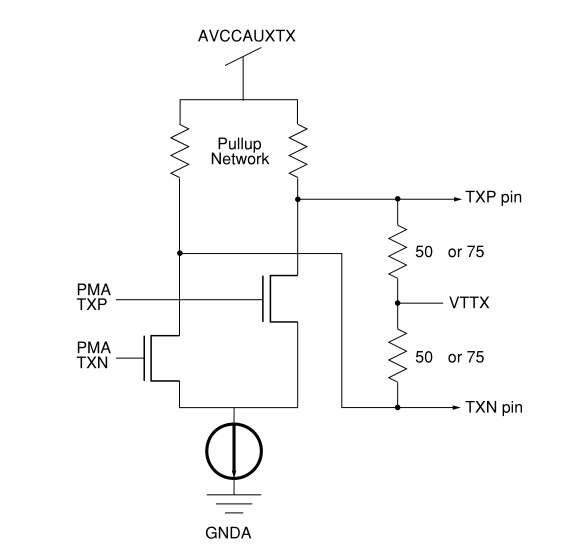

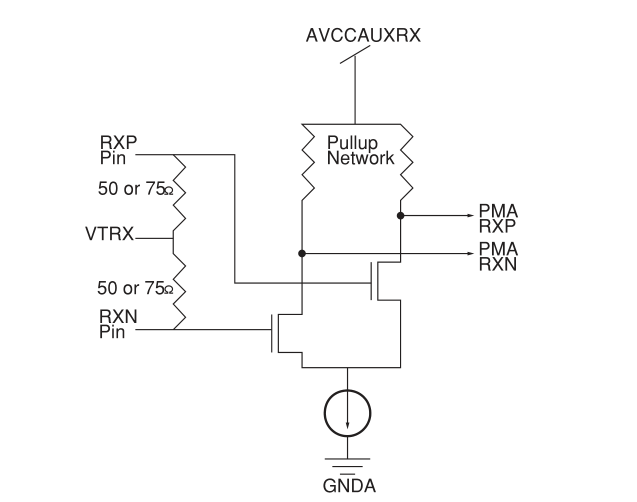

Serdes的物理接口上采用了基于差分的电接口模式,差分电流模式上选择CML电流模式逻辑,发送端:

接受端:

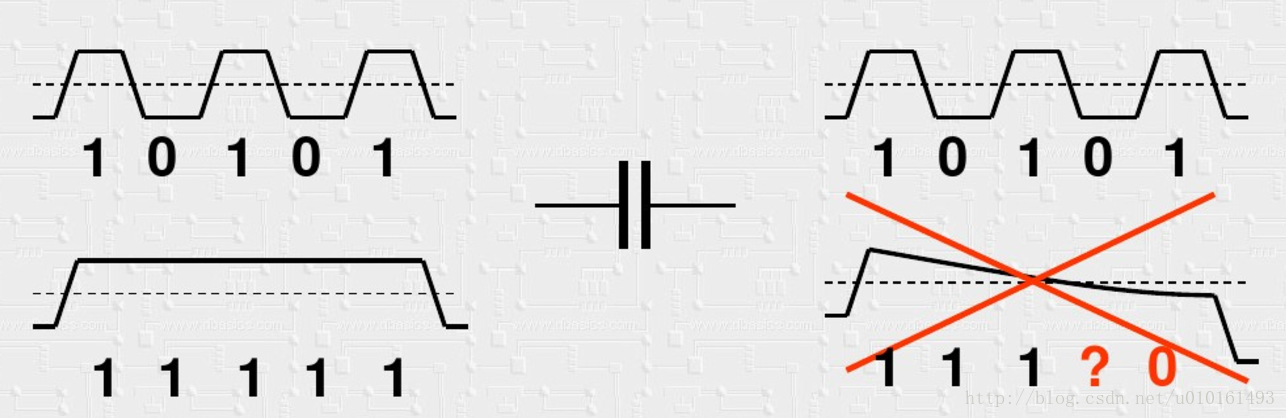

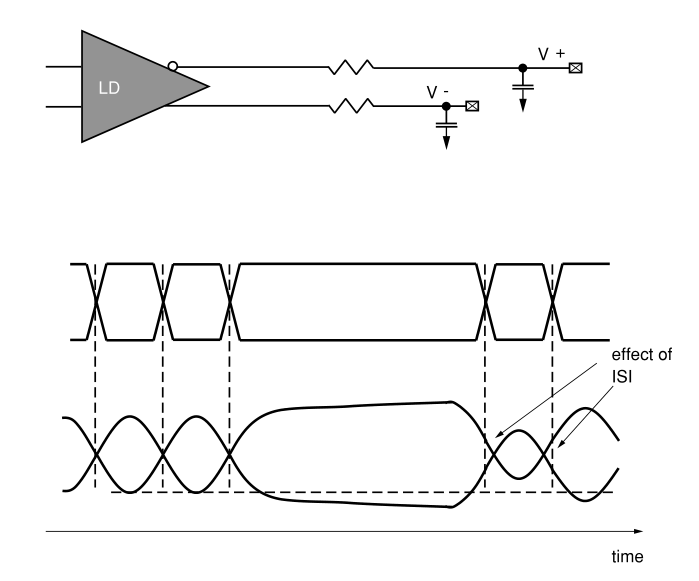

预加重是因为在高速串行数据流中符号符号之间存在串扰,也就是符号间干扰,

符号间干扰指的是当串行流中包含若干个相同的值时间后有短的相反值时间时就会发生符号间干扰,在较短的值时间内由于充电时间短,所以产生的振幅低。

预加重就是在充电时候进行过度驱动,所以在发生符号间干扰时,即使充电的时间较短,但是存在过度驱动的情况也就会发生幅值并不是太低的情况了。

本文只是一个比较统观的概念,笔者由于项目需求,离不开高速串行接口的使用,而实际上在具体的工程项目中,基本上都离不开高速串行接口的使用,无论是X家的Transceiver还是A家的Serdes,都必须通透理解,而具体的使用也必须经历过上板调试之后才可以说是已经学会甚至融汇贯通了,所以这里留个坑,接下来就要面对痛苦的上板调试过程了~~

1338

1338

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?